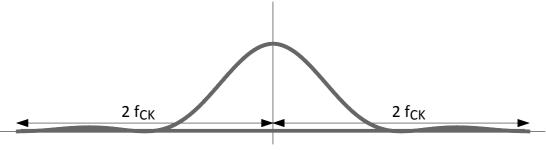

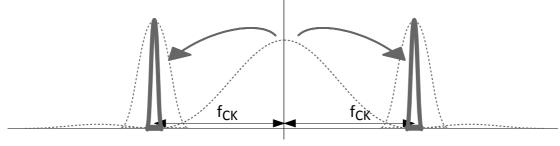

Signal spectrum (random bits)

(there is no energy at the clock frequency, whatever the bit pattern)

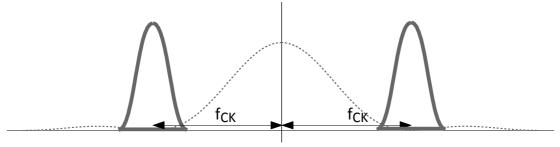

Non-linear processing can retrieve the embedded clock (which is not a pure line, but a spread out (=jittered) signal)

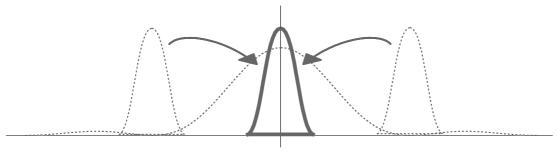

The phase comparator extracts the clock jitter and shifts it to d.c. (Clock jitter = VCO clock - RX embedded clock)

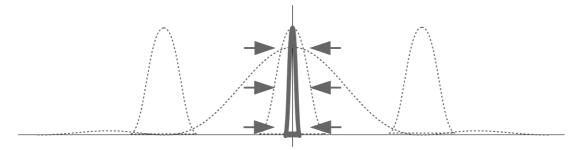

The PLL filter block is a lag corrector and rejects most of the high frequency jitter (its output signal is then fed as a FM modulating signal to the VCO)

The VCO is frequency modulated by output of the loop filter (As the modulation is a relatively low index FM, its spectrum around  $f_{CK}$  is almost the same)