TECHNICAL REPORT SECTION

NAVAL POSTGRADUATE SCHOOL

MONTEREY, CALIFORNIA 93940

NPS62-80-003PR

# NAVAL POSTGRADUATE SCHOOL

## Monterey, California

DIGITAL CONTROL AND INTERFACING FOR A HIGH

SPEED SATELLITE

COMMUNICATIONS SIGNAL PROCESSOR

John E. Ohlson Richard Mead

January 1980

Project Report

Approved for public release; distribution unlimited

Prepared for: Naval Electronic Systems Command

PME-106-1

Washington, D.C. 20360

## NAVAL POSTGRADUATE SCHOOL Monterey, California

Rear Admiral T. F. Dedman Superintendent

Jack R. Borsting Provost

The work reported herein was supported in part by the Naval Electronic Systems Command, PME-106-1.

Reproduction of all or part of this report is authorized.

This report was prepared by,

#### UNCLASSIFIED

| SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)       |                                            |                                                                |  |  |  |  |

|----------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| REPORT DOCUMENTATION                                           | READ INSTRUCTIONS BEFORE COMPLETING FORM   |                                                                |  |  |  |  |

| I. REPORT NUMBER                                               | 3. RECIPIENT'S CATALOG NUMBER              |                                                                |  |  |  |  |

| NPS62-80-003PR                                                 |                                            |                                                                |  |  |  |  |

| 4. TITLE (and Subtitle)                                        |                                            | 5. TYPE OF REPORT & PERIOD COVERED                             |  |  |  |  |

| Digital Control and Interfact<br>High Speed Satellite Communic | ing for a                                  | Project Report                                                 |  |  |  |  |

| Signal Processor                                               | Callons                                    | 6. PERFORMING ORG. REPORT NUMBER                               |  |  |  |  |

|                                                                |                                            |                                                                |  |  |  |  |

| 7. AUTHOR(s)                                                   |                                            | 8. CONTRACT OR GRANT NUMBER(s)                                 |  |  |  |  |

| John E. Ohlson                                                 |                                            |                                                                |  |  |  |  |

| Richard Mead                                                   |                                            |                                                                |  |  |  |  |

|                                                                |                                            |                                                                |  |  |  |  |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS                    |                                            | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |  |  |  |  |

| Naval Postgraduate School                                      |                                            |                                                                |  |  |  |  |

| Monterey, California 93940                                     | N0003980WR09137                            |                                                                |  |  |  |  |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                        |                                            | 12. REPORT DATE                                                |  |  |  |  |

| Naval Postgraduate School                                      |                                            | January 1980                                                   |  |  |  |  |

| Monterey, California 93940                                     |                                            |                                                                |  |  |  |  |

|                                                                |                                            | 105                                                            |  |  |  |  |

| 14. MONITORING AGENCY NAME & ADDRESS(If different              | t from Controlling Office)                 | 15. SECURITY CLASS. (of this report)                           |  |  |  |  |

|                                                                | Unclassified                               |                                                                |  |  |  |  |

|                                                                | 15a. DECLASSIFICATION/DOWNGRADING SCHEDULE |                                                                |  |  |  |  |

| 16. DISTRIBUTION STATEMENT (of this Report)                    |                                            |                                                                |  |  |  |  |

Approved for public release; distribution unlimited

- 17. DISTRIBUTION STATEMENT (of the abstract entered in Block 20, if different from Report)

- 18. SUPPLEMENTARY NOTES

- 19. KEY WORDS (Continue on reverse side if necessary and identify by block number)

Digital Interface, Array Processor, Data Acquisition Unit

20. ABSTRACT (Continue on reverse eide if necessary and identify by block number)

A digital interface has been designed and constructed as part of the Naval Postgraduate School Satellite Signal Analyzer System. This interface enables a Floating Point System, AP-120B, Array Processor to perform Direct Memory Access transfers with the Data Acquisition Unit.

#### ABSTRACT

A digital interface has been designed and constructed as part of the Naval Postgraduate School Satellite Signal Analyzer System. This interface enables a Floating Point System, AP-120B, Array Processor to perform Direct Memory Access transfers with the Data Acquisition Unit.

#### TABLE OF CONTENTS

| I.     | INT | TRODUCTION                                  | 9   |

|--------|-----|---------------------------------------------|-----|

|        | Α.  | BACKGROUND                                  | 9   |

|        | в.  | SPECIFIC GOALS                              | 9   |

|        | c.  | SCOPE OF THIS REPORT                        | 9   |

|        | D.  | SATELLITE SIGNAL ANALYZER                   | 1,0 |

| II.    | DES | SIGN CONCEPTS                               | 12  |

| III.   | AP/ | /IOP-16 CHARACTERISTICS                     | 13  |

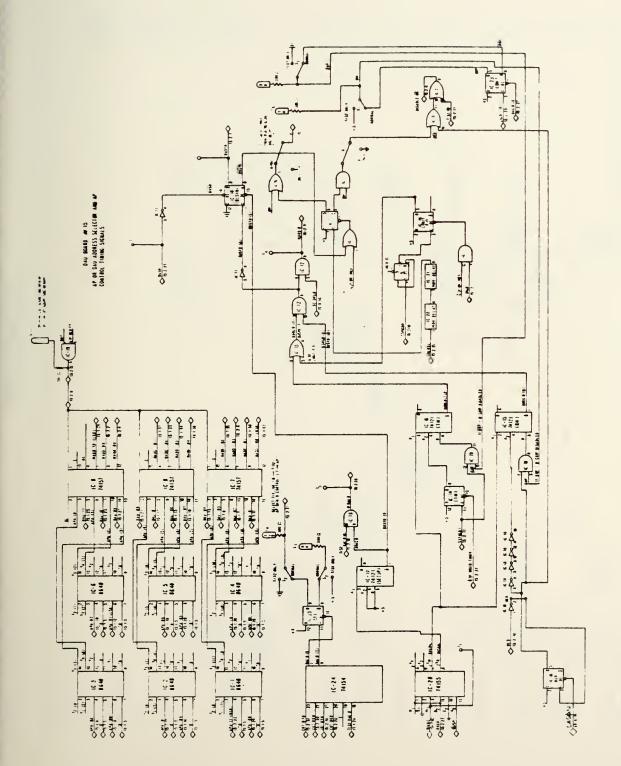

| IV.    | DAU | U MODIFICATIONS                             | 29  |

|        | Α.  | INTRODUCTION                                | 29  |

|        | В.  | MODIFICATION OBJECTIVES                     | 29  |

|        | c.  | ADDITIONAL HARDWARE                         | 33  |

|        |     | 1. Overview                                 | 33  |

|        |     | 2. Data and Control Lines                   | 33  |

|        |     | 3. Control Signals and Address Lines        | 33  |

|        |     | 4. Block Mode Read                          | 46  |

|        |     | 5. Toggle Mode Read                         | 49  |

| V.     | FLC | DATING POINT SYSTEMS AP-12ØB (AP) SIMULATOR | 62  |

|        | Α.  | INTRODUCTION                                | 62  |

|        | В.  | AP SIMULATOR OPERATION                      | 62  |

|        | c.  | USE OF AP SIMULATOR                         | 64  |

| VI.    | AP  | SOFTWARE                                    | 70  |

| VII.   | CON | NCLUSION                                    | 71  |

| APPENI | DIX | A - SOFTWARE PROGRAM                        | 72  |

| APPENI | DIX | B - DAU CIRCUIT BOARD SCHEMATICS            | 74  |

| APPENDI | X C - | DAU   | BOARD  | COMPONENT | LAYOUTS | <br>- | - | - | - | - | 82  |

|---------|-------|-------|--------|-----------|---------|-------|---|---|---|---|-----|

| APPENDI | K D - | DAU   | WIRING | G LISTS   |         | <br>- | - | - | - | - | 86  |

| LIST OF | REFE  | RENCE | ES     |           |         | <br>- | - | - | - | - | 1ø4 |

| INITIAL | DIST  | RIBUI | ION L  | IST       |         | <br>_ | _ | _ | _ | _ | 105 |

## LIST OF FIGURES

| 1.  | DAU System Block Diagram                                                                         | 11  |

|-----|--------------------------------------------------------------------------------------------------|-----|

| 2.  | IOP Registers and Data Paths                                                                     | 14  |

| 3.  | Timing Diagram IOP to External Device                                                            | 19  |

| 4.  | Timing Diagram External Device to IOP                                                            | 21  |

| 5.  | Typical External Bus Line                                                                        | 24  |

| 6.  | AP Backplane Connector                                                                           | 25  |

| 7.  | AP-12ØB - Backplane                                                                              | 27  |

| 8.  | AP-12ØB Simulator Backplane                                                                      | 28  |

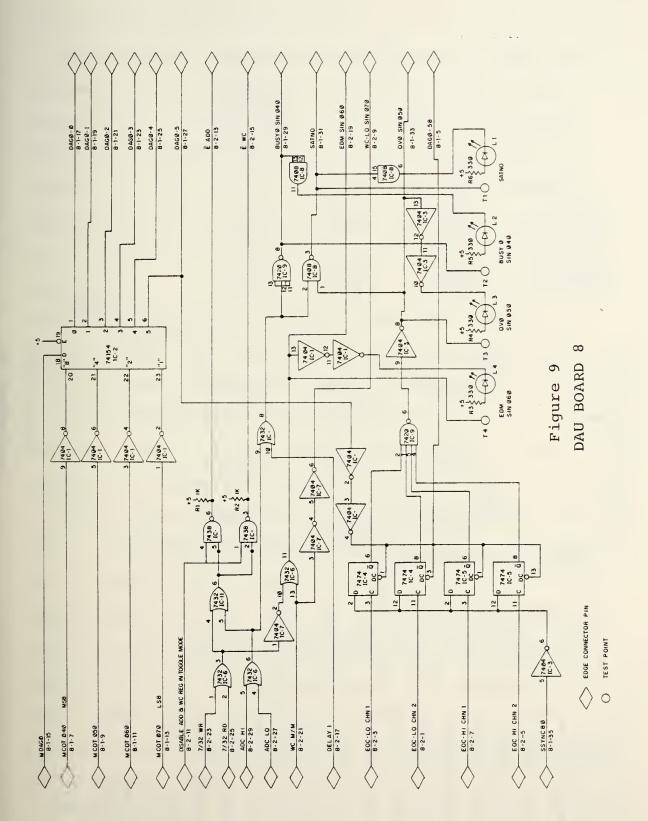

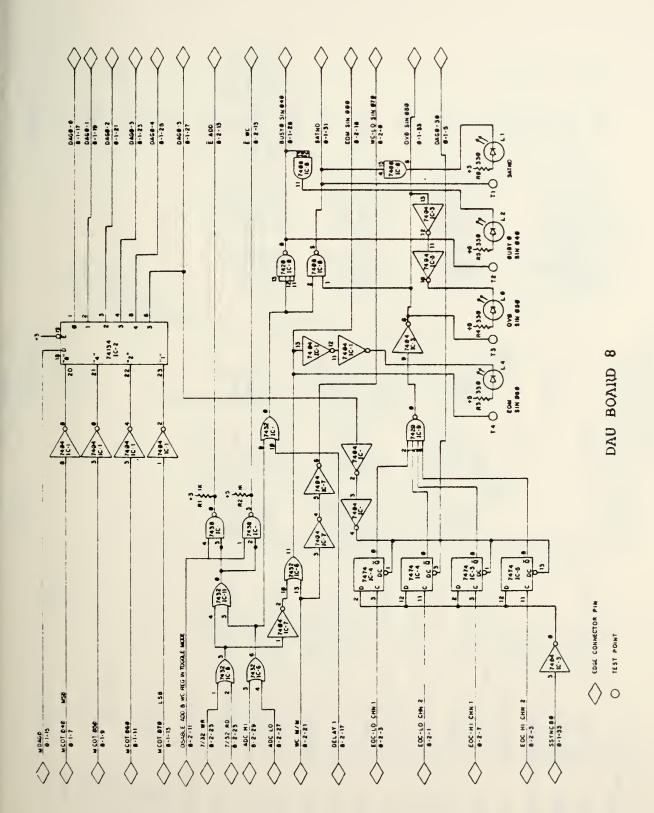

| 9.  | DAU Board 8                                                                                      | зø  |

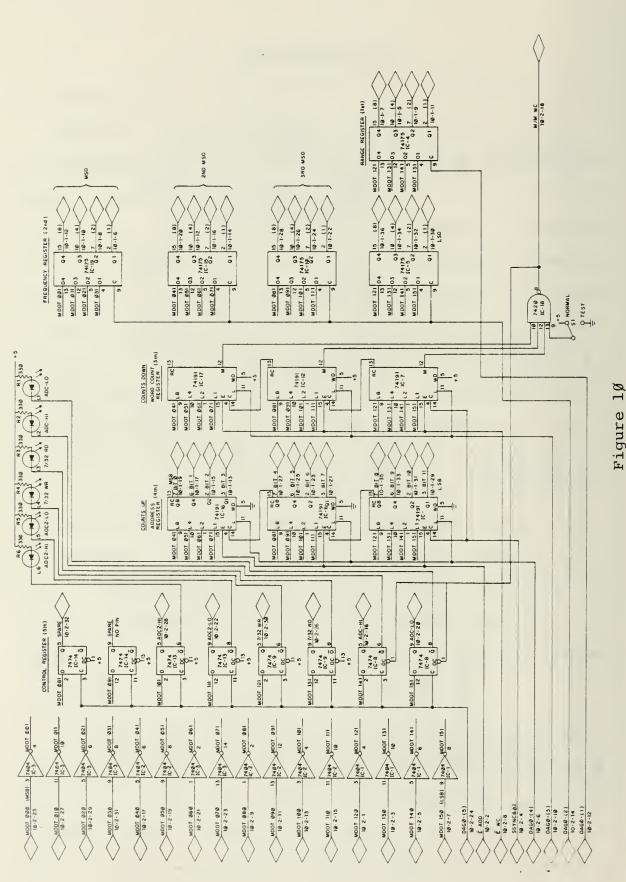

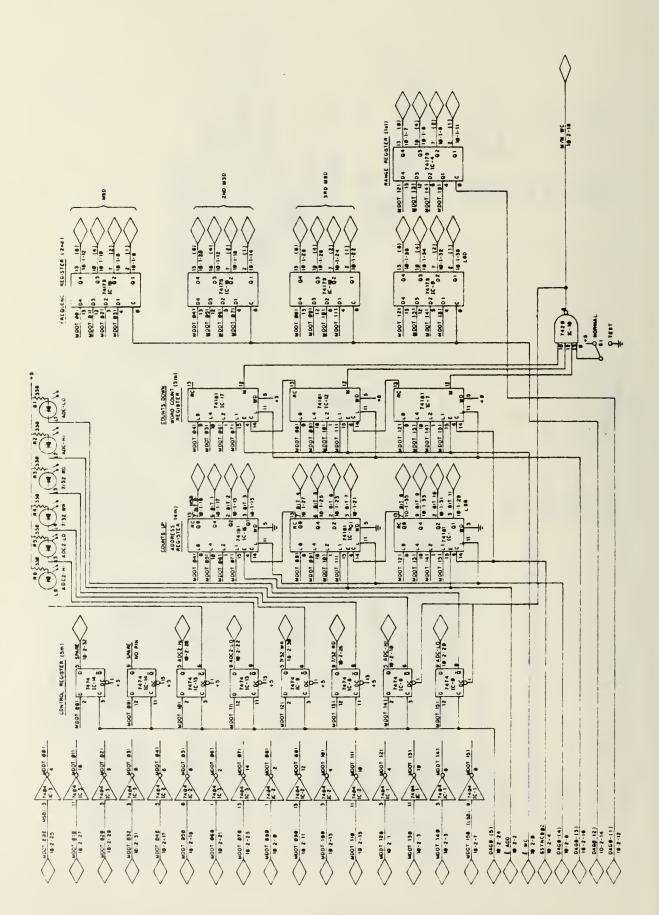

| lø. | DAU Board 10                                                                                     | 31  |

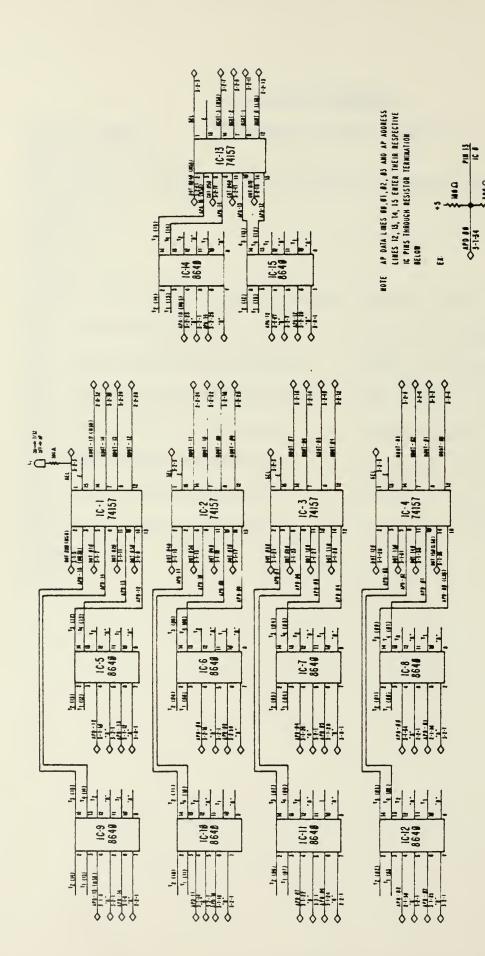

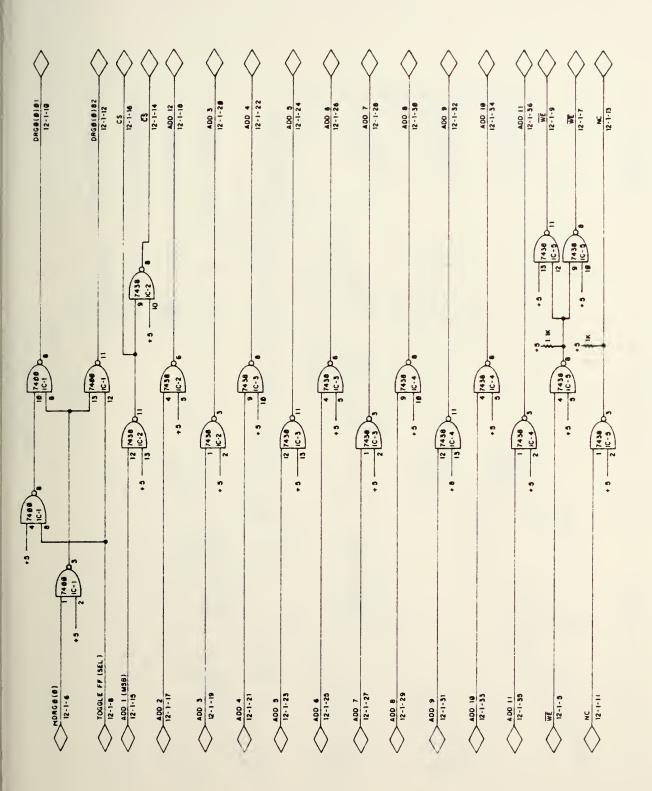

| 11. | DAU Board 3                                                                                      | 34  |

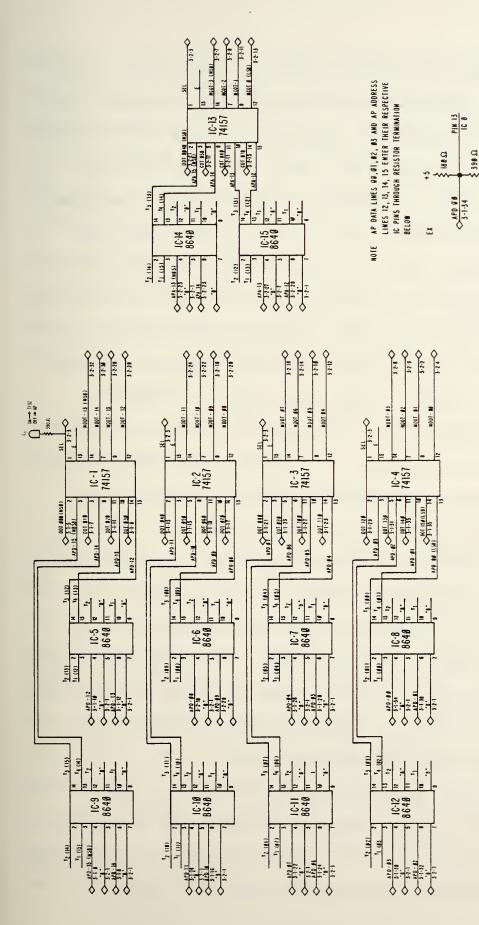

| 12. | Typical Combinational Logic For AP Data and Address Lines Through 8640 Receivers on DAU Board 15 | 37  |

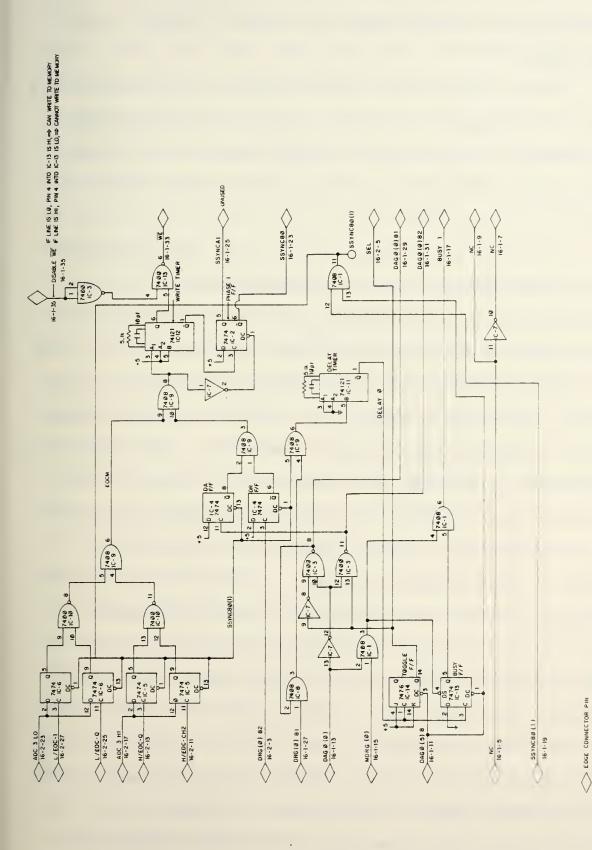

| 13. | DAU Board 12-1                                                                                   | 38  |

| 14. | DAU Board 15                                                                                     | 4 Ø |

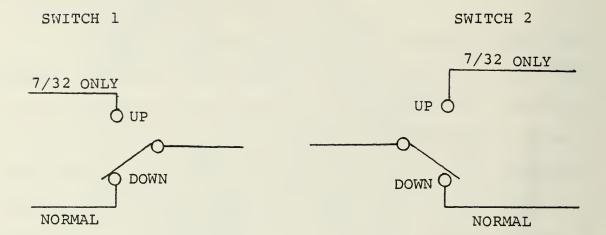

| 15. | Positions of Control Switches 1 and 2 on DAU Board 15                                            | 41  |

| 16. | Truth Table for BUSDAGØ and BUSDRGØ                                                              | 44  |

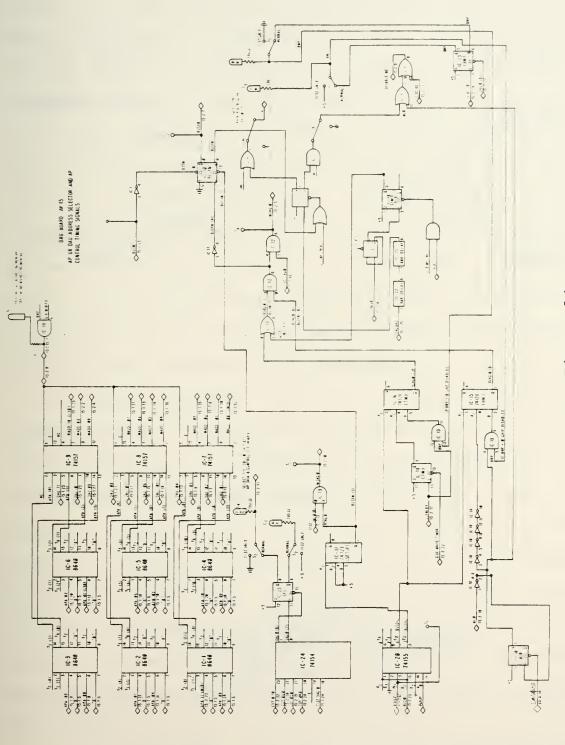

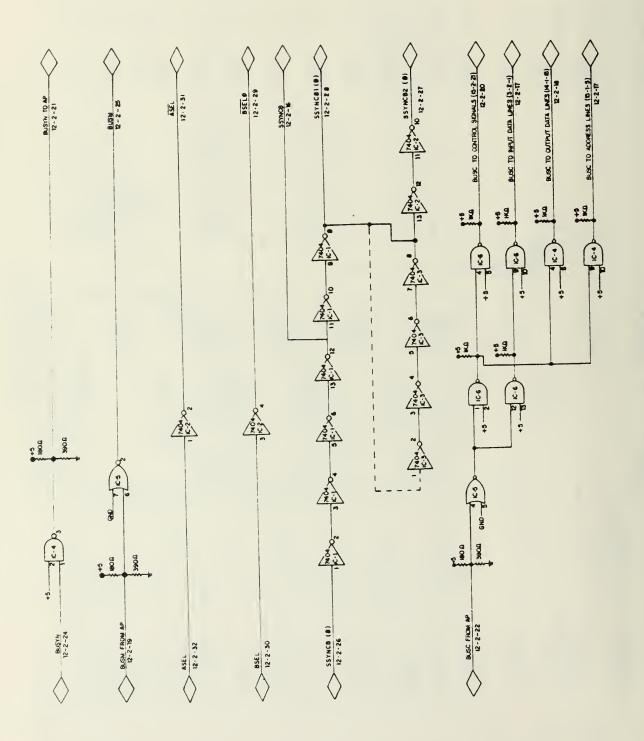

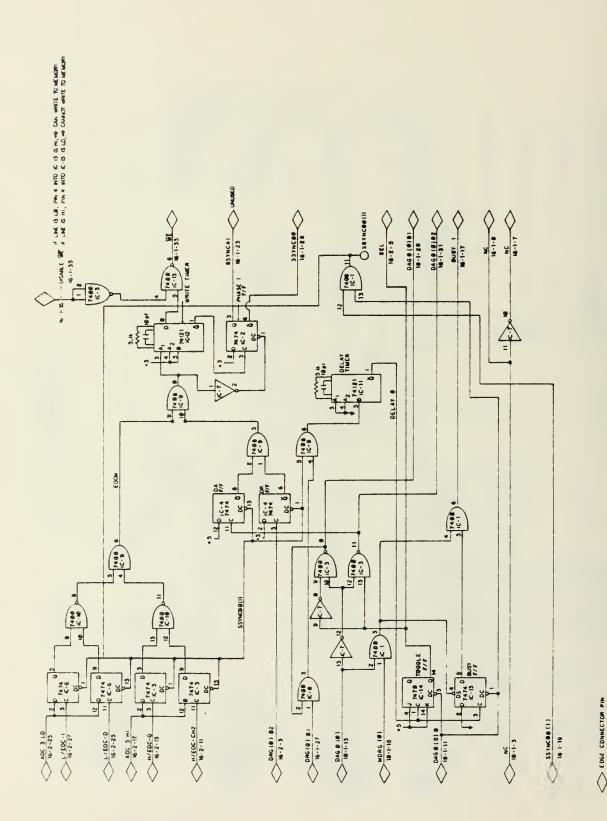

| 17. | DAU Board 16                                                                                     | 52  |

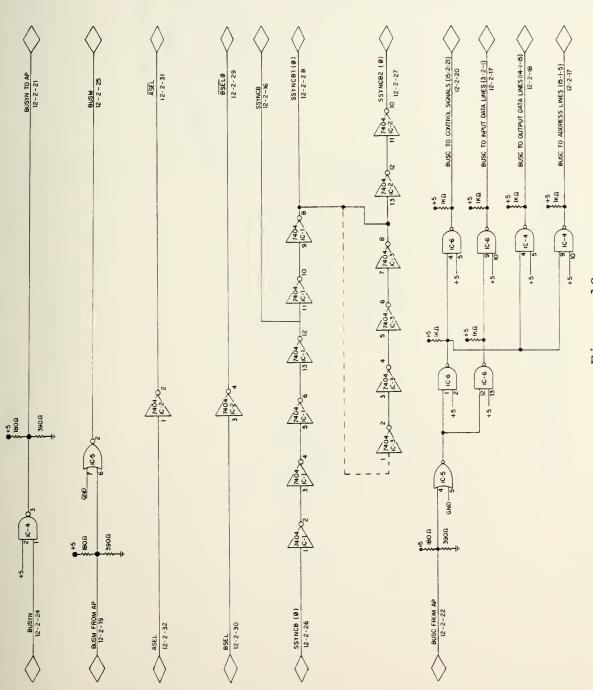

| 18. | DAU Board 12-2                                                                                   | 58  |

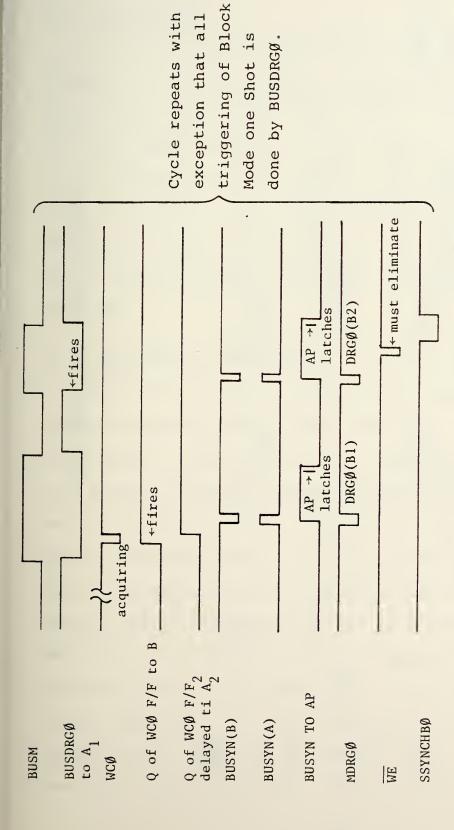

| 19. | Block Mode Read Timing Diagram                                                                   | 6ø  |

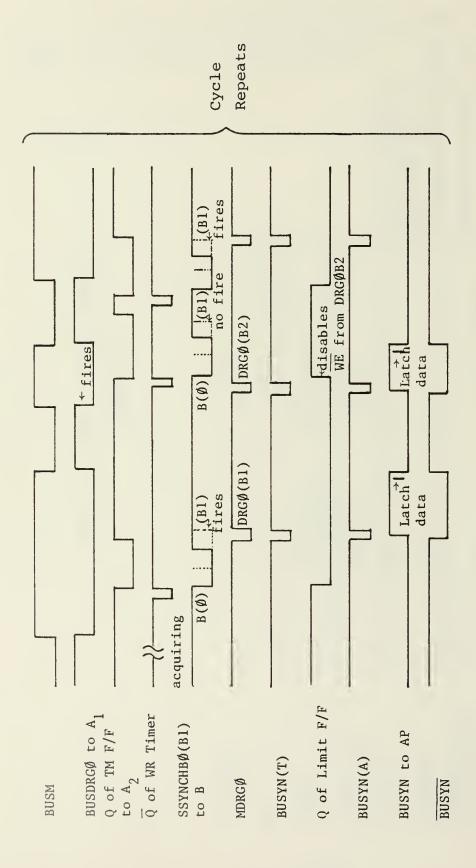

| 2Ø. | Toggle Mode Read Timing Diagram                                                                  | 61  |

| 21. | AP Simulator Circuit Schematic                                                                   | 63  |

### LIST OF TABLES

| I.   | IOP External Bus Signals                                                    | 17 |

|------|-----------------------------------------------------------------------------|----|

| II.  | Summary of AP/IOP Signals and Their State at Different DAU System Locations | 23 |

| III. | Test Points and Lights on DAU Board 15                                      | 57 |

| IV.  | AP Simulator Summary                                                        | 65 |

| V.   | AP Simulator Operation                                                      | 69 |

This page intentionally blank.

#### I. INTRODUCTION

#### A. BACKGROUND

This project is one of a series of research projects undertaken by the Naval Postgraduate School (NPS) Satellite Communications Laboratory concerning Navy UHF Satellite Communications. In March of 1977, this laboratory received funding from PME 106-1 of the Naval Electronic Systems Command (NAVELEX) to develop, design and construct a Satellite Communication (SATCOM) Signal Analyzer at NPS. The purpose of the SATCOM Signal Analyzer is to provide high speed spectrum analysis of the Navy UHF communication satellite transponders while in orbit.

#### B. SPECIFIC GOALS

The specific goals in the development of this system are: (1) to provide all necessary equipment to make realtime measurements at NPS; (2) develop satellite signal analysis techniques; (3) to provide equipment design for use in a follow-on version of the Fleet Satellite Monitoring System (FSM) presently in use at the Naval Communication Stations to monitor the GAPFILLER and FLTSAT satellites.

#### C. SCOPE OF THIS REPORT

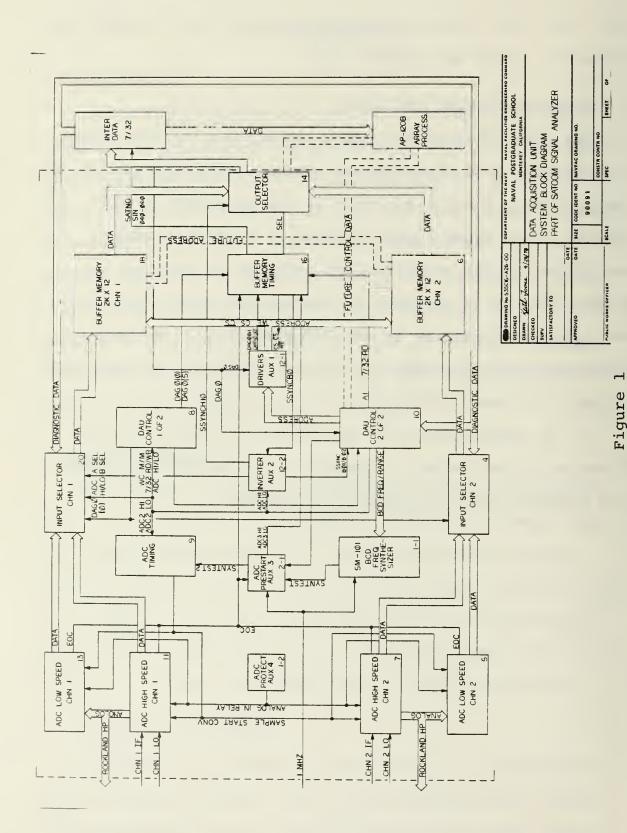

Figure 1 is a simplified block diagram of the SATCOM

Signal Analyzer System. This report documents the design

and construction of the interface between the Data Acquisi-

tion Unit (DAU) and the Floating Point Systems AP-12ØB Array Processor, shown as a dashed line.

#### D. SATELLITE SIGNAL ANALYZER

The SATCOM Signal Analyzer has been constructed around an INTERDATA 7/32 minicomputer system, which provides all the necessary control for most of the equipment in the system. High speed signal processing of data acquired, analog-to-digital converted and buffered in the Data Acquisition Unit is provided by the AP-12ØB Array Processor, as a peripheral device to the INTERDATA 7/32. Additional peripherals are provided for display, control, and software support as shown in Figure 1.

11

#### II. DESIGN CONCEPTS

The design goals for the SATCOM Signal Analyzer have been ordered in two major phases. Phase I produced an operational signal analyzer, including a working Data Acquisition Unit (DAU) integrated into the installed system. The first phase is presented in /1/2 and /2/2. Phase II is intended to optimize the system performance within the constraints of the present devices. Phase II involves modifications of the DAU to allow a direct interface with the AP-12ØB. This means data previously acquired and buffered in the DAU, then passed to the 7/32, then to the AP-12ØB for processing will now be sent directly to the AP-12ØB resulting in a considerable savings of system overhead. This will also allow the INTER-DATA 7/32 to perform more control functions and greatly increase system throughput rates.

#### III. AP/IOP-16 CHARACTERISTICS

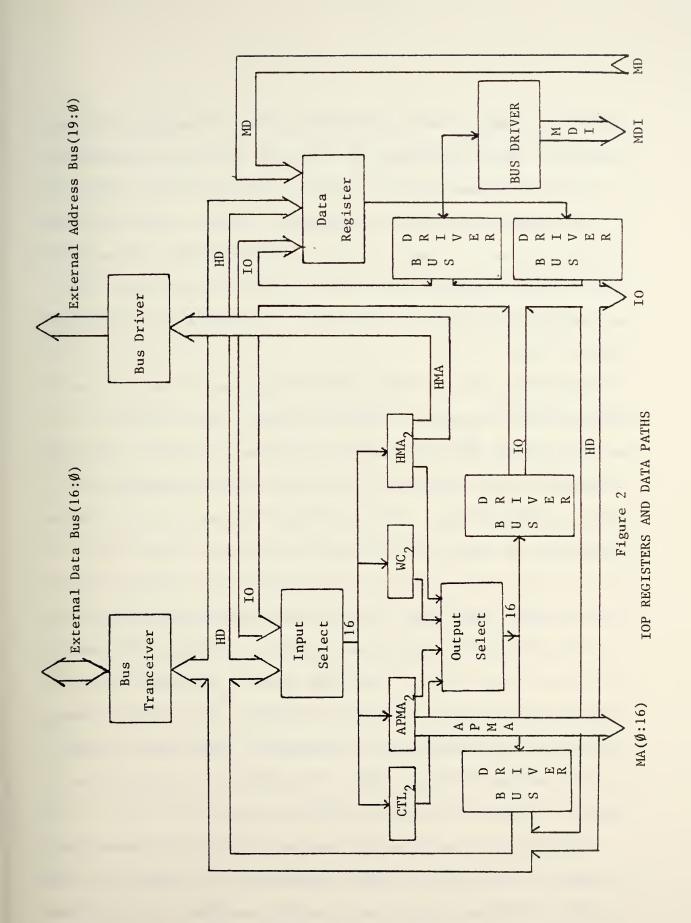

The Array Processor, AP-12ØB, has an input/output port (IOP) that provides for a hardware interface design connection to an external device, i.e. the DAU. The internal I/O registers and Direct Memory Access (DMA) converse with an external device via the IOP. The IOP appears to the DAU, or any external device, as a data bus 16 bits wide, an address bus 2Ø bits wide, and control lines / 3 7, see Figure 2.

The IOP uses a separate DMA priority level compared to that of the AP-12ØB processor and the host interface INTER-DATA 7/32. This implies that while the AP-12ØB is accessing memory, the IOP and 7/32 can perform time multiplexed cycle stealing. The memory controller of the AP-12ØB grants the priority of requests as follows: 7/32 highest, IOP next, AP-12ØB processor last. Thus, cycles stolen by the 7/32 and IOP are transparent to an executing AP-12ØB program.

The IOP is comprised of four DMA registers and a data register organized around the Host Data (HD) bus, see Figure 2. All data going from/to the DAU to/from the IOP passes through this HD bus. Note that data from the AP-12ØB memory to the IOP data register passes through the main data (MD) bus. Data from the IOP to AP-12ØB memory goes over the main data input (MDI) bus. Data and DMA control words pass from the AP internal registers to the IOP DMA control registers via the I/O bus. Main data memory addresses are

supplied to the AP main data memory over the memory address (MA) bus. Note that there is a direct path from the External Device Address Register (HMA2) to the external address bus. An important point to remember is that while the 7/32 and the IOP have a common access to the AP-12ØB I/O and MD buses, the two interfaces cannot directly communicate. Intercommunication must be effected by executing AP-12ØB programs  $\sqrt{3}$ .

Utilizing the four DMA control registers, the IOP regulates block transfers to/from the DAU. The External Device Address Register (HMA2) maintains the address of the peripheral device or memory for the source/destination of the transferred data. The Word Count register (WC2) counts the number of data words in the DMA process. When WC2 hits zero the DMA transfer stops. Hardware prevents WC2 from counting past zero. The AP-12ØB Memory Address Register (APMA2) points to consecutive locations in Main Data memory during the DMA transfer. The DMA Control Register (CTL2) controls the direction, mode of transfer, and provides status information pertaining to the transfer. HMA2, WC2, APMA2, and CTL2 are all 16 bits wide. A precise functional description of the CTL2 bits is provided in \( \subseteq 3.7 \).

While either the external device, DAU in this case, or the AP-120B can initiate DMA transfers, this design utilizes only DMA transfers initiated from the AP-120B. The IOP DMA control registers are accessed by the AP as devices on the

AP internal I/O bus. The AP selects a particular register and loads its address into the Device Address (DA) register. Then when the DA register is set the AP can load the selected register. Note that single word DMA transfers are made by setting  $WC2=\emptyset\emptyset\emptyset\emptyset\emptyset1$ .

The rate at which the IOP can DMA transfer words over the external bus depends on the speed of Main Data (MD) Memory. The maximum rate is one 16-bit word/667ns or 1.5 MHz. It is possible for Host interference to cause a delay of up to 500ns on an individual cycle. Note that since the Host has a higher priority level to access MD memory, it could conceivably lock out the IOP. However, the 7/32 can transfer at a rate of 1MHz only if it is performing no other operations. Thus the IOP should be able to access MD memory during simultaneous transfers.

The IOP provides 16 data lines, 20 address lines, and three control signals to the DAU. These signal names and their functions are listed in Table 1.

The device that initiates the DMA transfer assumes the driver role. The driver places the appropriate address on the address lines, enables data onto the data lines, puts BUSC in the proper state. After allowing a specified time for data and address lines to settle, the driver asserts BUSM to initiate the transfer. Having performed the task as directed, the driven device responds with BUSYN. The driver then removes BUSM upon receiving BUSYN, and after

#### TABLE I

## IOP EXTERNAL BUS SIGNALS

| SIGNAL                             | FUNCTION                                                                                                                                                                         |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSD 16-BUSD ØØ<br>(APD 16-APD ØØ) | 16 data transfer lines                                                                                                                                                           |

| BUSA 19-BUSA ØØ<br>(APA 19-APA ØØ) | $2\emptyset$ external device address lines. Used by the driving device to select a register in the driven device. Note BUSA $\emptyset\emptyset$ is always zero (high).          |

| BUSMSYN (BUSM)                     | BUSMASTER. Driving device syn-<br>chronization strobe. Initiates<br>data transfer in the driven device.                                                                          |

| BUSSYN (BUSYN)                     | BUSYNCHRONIZER. Drive device synchronization strobe. Indicates to the driving device that the driven device has either accepted data or has data ready for the driver to accept. |

| BUSC                               | BUS CONTROL signal. Used by the driving device to select the direction of transfer. Low ("1") selects driver to driven device. High (" $\beta$ ") selects driven to driver.      |

Note: With respect to this report, at all times the IOP is the driving device and the DAU is the driven device.

allowing for propagation delay in the cable, releases the data and address lines. When the driven device receives false BUSM (low), it removes BUSYN and the cycle is ready to start again.

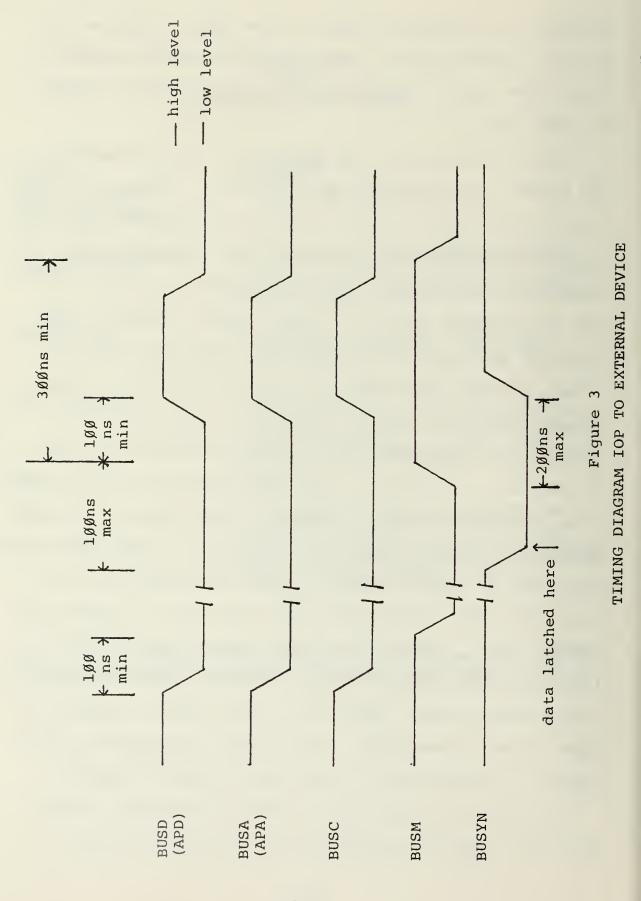

For the purposes of this report, the IOP will assume the driver role during all DMA transfers. A diagram of the timing relationships among bus signals is shown in Figure 3. A cycle begins with the IOP driving the address and data lines to a desired state and forcing BUSC true (low on the bus), for transfer from IOP to DAU. After a delay of 100ns (minimum) to allow address and data to propagate and stabilize, the IOP drives BUSM true (low on the bus). If the DAU was prepared to accept the data, it would strobe the data into the addressed register and drive BUSYN true (low on the bus). A maximum of 100ns after the IOP receives BUSYN true, it removes BUSM, i.e. makes it false (high on the bus). The address lines are held true a minimum of 100ns after BUSM goes false to insure against a change while BUSM is still true. The IOP considers the cycle over when it removes the address lines. The external device should remove BUSYN no later than 200ns after BUSM goes false to prevent interfacing with the next cycle. BUSM will go true again a minimum of 300ns after it goes false. The actual time depends on the number of cycles stolen by Host from AP-12ØB MD memory.

Note that the cycle time is actually dependent on the speed with which the driven device responds with BUSYN.

This dependency allows DMA transfers to take place at the driven device speed. A time-out circuit is provided in the IOP to prevent "hanging" the IOP forever if the external device fails to respond due to an error  $\sqrt{3}$ . The factory installed time-out is 20 microseconds. If no response is seen within that time, the entire DMA process is terminated. This time-out may be lengthened or disabled by adjusting the resistor-capacitor timing on chip A-19 of board 237. The resistor,  $R_T$ , should be kept in the range  $5k\Omega < R_T < 500 k\Omega$ . Defining TW as pulse width, the equation TW =  $(0.32)(R_T \cdot C_{EXT})(1 + 0.7/R_T)$  applies for chip A-19 (74123) where 0.32 is a constant,  $0.32 \cdot R_T = k\Omega(total)$ ,  $0.32 \cdot R_T = R_T = R_T \cdot R_T =$

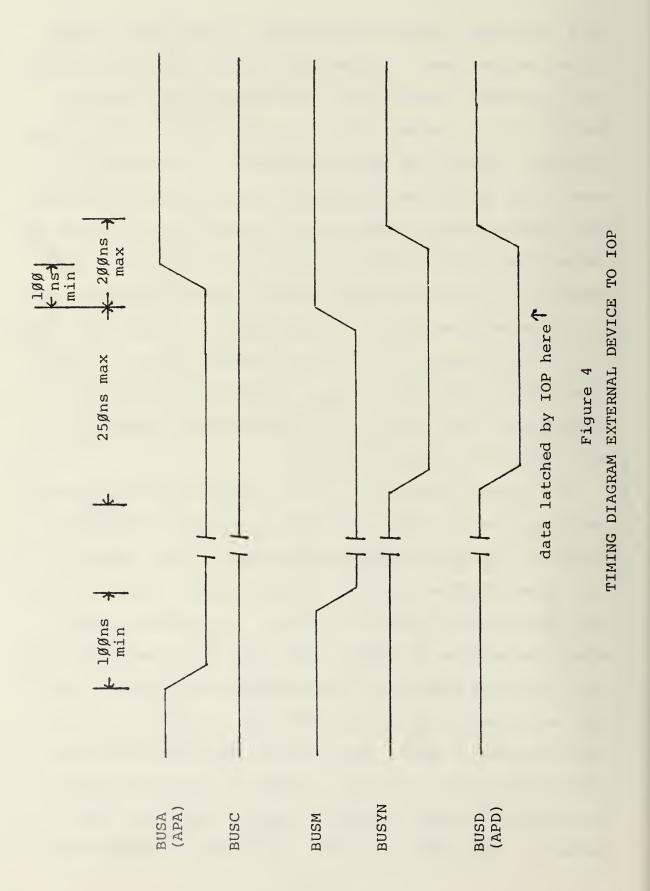

The timing diagram for a DMA transfer from the external device to the IOP under IOP control is snown in Figure 4.

First the IOP drives address data onto the bus. BUSC is left false (high on the bus) to indicate the transfer is from the external device to the DAU. A minimum of løøns after the address is driven, BUSM goes true (low on the bus). Upon receiving BUSM true, the external device should drive data onto the bus and return BUSYN, all within 0.5s from the assertion of BUSM. When the IOP receives BUSYN true, the IOP will wait a minimum of 25øns to allow the data to propagate and settle, before strobing it into the DATA2

Register. When data is latched, the IOP will remove BUSM

and a minimum of 100ns later remove the address data from the bus. The external device should remove BUSYN and the data no later than 200ns after BUSM goes false. The IOP will drive BUSM true (low on the bus) again no sooner than 300ns after it went false.

To assist the reader and system user, a summary of AP/

IOP signals and their active states at different DAU system

locations is provided in Table II.

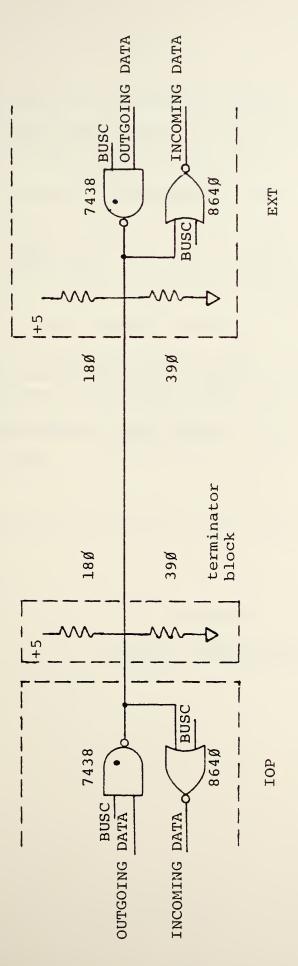

All of the external bus signals are open collector bidirectional lines. A signal is considered true when in the low state on the bus. The method recommended by Floating Point Systems for interfacing is shown in Figure 5. The drivers are 7438 open-collector buffers. The receivers are 8640 bus receivers. One line input to each driver-receiver pair is connected to BUSC or BUSC to appropriately enable or disable the chip for directional control of data flow.

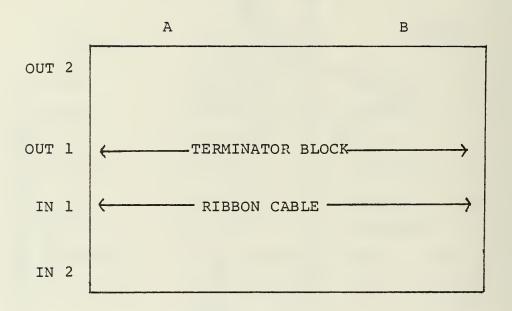

Appendix D contains a wiring pin-out list for the backplane of the AP. Data is carried to the external device via

a Ribbon cable. Figure 6 shows a representation of the AP

backplane as viewed from the back of the AP. Note there

are two input terminals IN1 and IN2 and two output terminals

OUT1 and OUT2 referenced with respect to the AP. Since the

SATCOM LAB has only one IOP-16, terminals IN1 and OUT 1 are

used. The terminal block referenced on Figure 6 is placed

in the OUT1 terminal location. The ribbon cable enters the

IN1 location.

TABLE II

SUMMARY OF AP/IOP SIGNALS AND THEIR

STATE AT DIFFERENT DAU SYSTEM LOCATIONS

|       | INSIDE AP*     | ON<br>BUS CABLE | INSIDE<br>DAU** |  |  |

|-------|----------------|-----------------|-----------------|--|--|

| BUSC  | H=+5=T=1       | L=GND=T=Ø       | H=+5=T=1        |  |  |

|       | L=GND=F=Ø      | H=+5=F=1        | L=GND=F=Ø       |  |  |

| BUSM  | H=+5=T=1       | L=GND=T=Ø       | H=+5=T=1        |  |  |

|       | L=GND=G=Ø      | H=+5=F=1        | L=GND=F=Ø       |  |  |

| BUSYN | H=+5=T=1       | L=GND=T=Ø       | H=+5=T=1        |  |  |

|       | L=GND=F=Ø      | H=+5=F=1        | L=GND=F=Ø       |  |  |

| BUSD  | H/L=+5/GND=1/Ø | H/L=+5/GND=Ø/1  | H/L=+5/GND=1/Ø  |  |  |

| BUSA  | H/L=+5/GND=1/Ø | H/L=+5/GND=Ø/L  | H/L=+5/GND=1/Ø  |  |  |

H = HIGH

L = LOW

GND = GROUND

T = TRUE

F = FALSE

\* → BEFORE LINE DRIVER

\*\* → AFTER LINE RECEIVER

TYPICAL EXTERNAL BUS LINE

Figure 5

Figure 6

AP BACKPLANE CONNECTOR

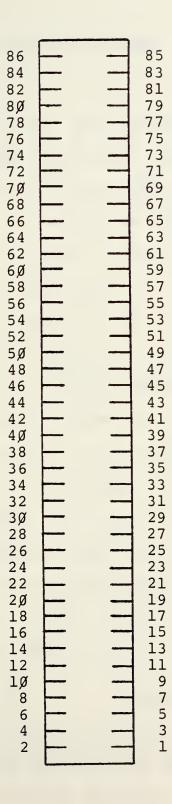

The letters on the backplane diagram, Figure 7, correspond to a wiring list internal to the AP /3\_7. For convenience, the IN1 terminal connector can be thought of as an 80 pin connector, even numbers on the top and odd on the bottom as shown in Figure 8. Note that the connector in the back of the DAU where the ribbon cable attaches is an 86 pin connector. A plug is placed in pin hole 81-82 for compensation to insure proper connection. Inspection of the ribbon cable reveals an insert at pin locations 37-45 to fit the AP backplane. This means pins 37-45 must not be used in the DAU. Care must be exercised at all times when handling the ribbon cable.

```

1

2

1

2

1

2

1

2

Α

Α

Α

Α

В

В

В

В

C

C

C

C

C

D

D

D

D

E

E

E

E

E

F

F

F

F

F

Η

Η

Η

Η

H

H

J

J

J

J

J

J

J

K

K

K

K

K

L

L

L

L

L

L

Μ

M

M

M

M

M

M

N

N

N

Ν

N

N

Ν

P

P

P

P

P

P

R

R

R

R

R

R

R

S

S

S

S

S

S

T

T

T

T

T

T

T

U

U

U

U

U

U

V

V

V

V

V

V

2

1

1

2

1

1

1

2

1

2

1

2

1

1

Α

Α

Α

Α

Α

Α

В

В

В

В

В

C

C

C

C

C

C

D

D

D

D

D

D

D

E

E

Ε

Ε

Ē

E

F

F

F

F

F

F

F

Η

Η

Η

H

H

Η

J

J

J

J

J

J

K

K

K

K

K

K

L

L

L

L

L

Μ

Μ

Μ

Μ

Μ

Μ

N

Ν

N

N

N

N

N

P

P

P

P

P

P

R

R

R

R

R

R

S

S

S

S

S

S

T

T

Т

Т

Т

U

U

U

U

U

V

V

V

V

1

2

1

2

1

```

Α

В

Figure 7

AP-12ØB - BACKPLANE

Figure 8

AP-12ØB SIMULATOR BACKPLANE

#### IV. DAU MODIFICATIONS

#### A. INTRODUCTION

Originally the DAU was setup and controlled solely by the INTERDATA 7/32. The 7/32 passed addresses via COT lines and data via DOT lines to boards 8 and 10, Figures 9 and 10 respectively. This data was passed via backplane connectors two (2) and three (3) from the 7/32. The five key internal registers of the DAU: (1) range, (2) frequency, (3) address, (4) word count, and (5) control, were set up by data passed from the 7/32. The internal buffer memory was addressed only from the DAU address register (3). Consequently as data was acquired and then read out, the address register (3) was reset to zero to insure the first point acquired was the first point readout. The Word Count register (4) was set initially for acquisition and then reset when reading out to insure all the data was read. The control register (5) was set as desired to high speed acquisition, low speed acquisition, read, etc. Note that the sample rate was first set in registers (1) and (2) and remains until changed.

#### B. MODIFICATION OBJECTIVES

The modification objectives of this report consist of using the AP-120B's IOP-16 interface as a smart device to set up and control the internal device registers. So, utilizing the IOP-16 under program control of the AP makes it, the IOP-16, the controller of the DAU from a user program

that can be passed from the 7/32.

Conceptually, to minimize lost processing time in the AP-12ØB, a program using AP Assembly Language can start the DAU into an acquisition mode and continue to process data already stored in the AP main data memory from a previous acquisition. At the same time, the IOP-16 having started the DAU into an acquisition mode, will wait for an end of acquisition signal from the DAU, i.e. word count equals zero in the Block Mode read. Then the most recently acquired data will be stored in AP main data memory in a non-processing block location via DMA transfer. When the AP has finished processing a block of data it will check to see if the new DMA is completed and if so it will start yet a new acquisition and commence processing the most recent DMA transfer from the DAU.

During slow sample rates, i.e. less than 700KHz, the IOP is theoretically capable of transferring out the new data directly after it acquired it on a word by word basis vice a block of words. This is referred to as the Toggle Mode. In this mode data is available to the AP almost immediately after the A/D conversion. For sample rates above 700KHz the data will be transferred out in blocks, i.e. Block Mode, after each block is acquired and stored in buffer memory. The block transfers for high sample rates will not affect AP throughput since the time between "processing" modes is greater than the time between "start"

acquisition" for those sample rates. NOTE: The user may select Block Mode at any sample rate independent of speed.

#### C. ADDITIONAL HARDWARE

### 1. Overview

The modifications outlined in this report consist essentially of multiplexing AP/IOP-16 data and address lines with 7/32 data and address lines and providing additional control hardware.

Initially, it should be noted that at the backplane of the DAU the 7/32 lines now enter at connectors one (1) and three (3) vice two (2) and three (3) as in  $\sqrt{2}$ . Connector (1) replaces connector (2) essentially line for line, the reason connector (1) was used was to avoid changing the wire wrap lines on the DAU bottom plane.

Essentially two new boards were added to the DAU and controls were changed on several other boards. These changes will be presented sequentially.

## 2. Data and Control Lines

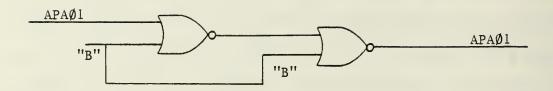

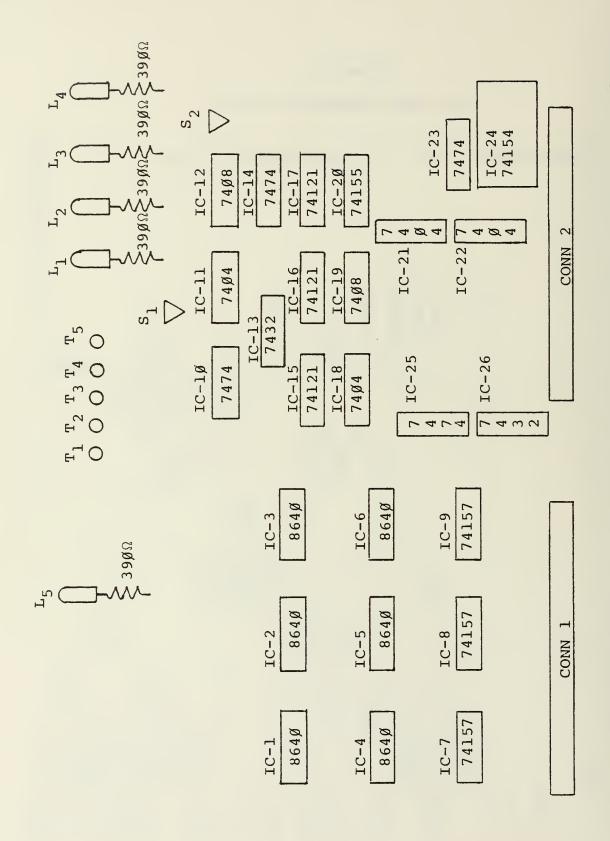

DAU Board three (3), Figure 11, consists of multiplexed data and control lines from the AP/IOP-16 and INTER-DATA 7/32. As explained in section III the IOP-16 data lines (16 each) enter IC's 5 through 12 which are 8640 line receivers. Note that each line enters two 8640 gates so as to invert it (see Figure 12). Within the concept of bi-directional data lines, "B" would be wired to BUSC so as to

AP OR 7/32 DATA AND CONTROL SELECTOR DAU BOARD ## 3

Figure 11

DAU BOARD

34

enable or disable the 8640 receiver appropriately. However, since the DAU "receives" data and addresses on these lines, "B" is wired to ground for simplicity. Should the DAU send data to the AP via these data lines, receiving the data here as it is sent has no effect. Each line must be inverted to be compatible with the 7/32 data lines that previously entered DAU board ten (10), Figure 10. Note that as the data lines enter board ten (10) they are buffered by 74Ø4 hex inverters. Thus to be compatible the IOP-16 data must be inverted prior to the 74Ø4 hex converters on board ten (10). As the IOP-16 data lines leave the 8640 line receivers they enter IC's (1) through (4) which are 74157 QUAD one of two Data Selectors. The 7/32 data lines from backplane connector (1) also enter IC's (1) through (4). Here a selection is made as to whether the AP or 7/32 will supply data to the DAU internal registers. The selection method will be discussed later. The output of IC's (1) through (4) will be referred to as Master Data Out lines, MDOTØØ-MDOT15 (most significant, MSB). These MDOTØØ through MDOT15 lines now enter board ten (10) as shown in Figure 10. To conform with INTERDATA 7/32 convention, MDOT15 (MSB) becomes MDOT $\emptyset\emptyset$  (MSB) on board ten (1 $\emptyset$ ).

Originally COT lines from the 7/32 were used to address the DAU internal registers. These COT lines now enter board three (3) at IC-13 at 74157 Quad one of two Data Selector. The AP must also supply four "COT" lines. It

does so in the form of address lines 12 through 15 (MSB). The AP/IOP-16 address lines enter through IC's (14) and (15) 864Ø line receivers. Note as with the data lines, each line enters two 864Ø gates so it is inverted to be compatible with logic on board eight (8), Figure 9. The 7/32 COT lines or AP address lines 12-15 are selected by IC-13. The selection logic will be discussed later. Note as the lines leave IC-13 they are Master Command Out lines (MCOT). Also note on board three (3) MCOT-3 (MSB) is MCOT Ø4Ø (MSB) on board eight (8) to conform with INTERDATA 7/32 convention.

There is a light  $(L_1)$  on board three (3) to indicate whether the 7/32 (on) or AP (off) is controlling the MDOT and MCOT lines respectively.

# 3. Control Signals and Address Lines

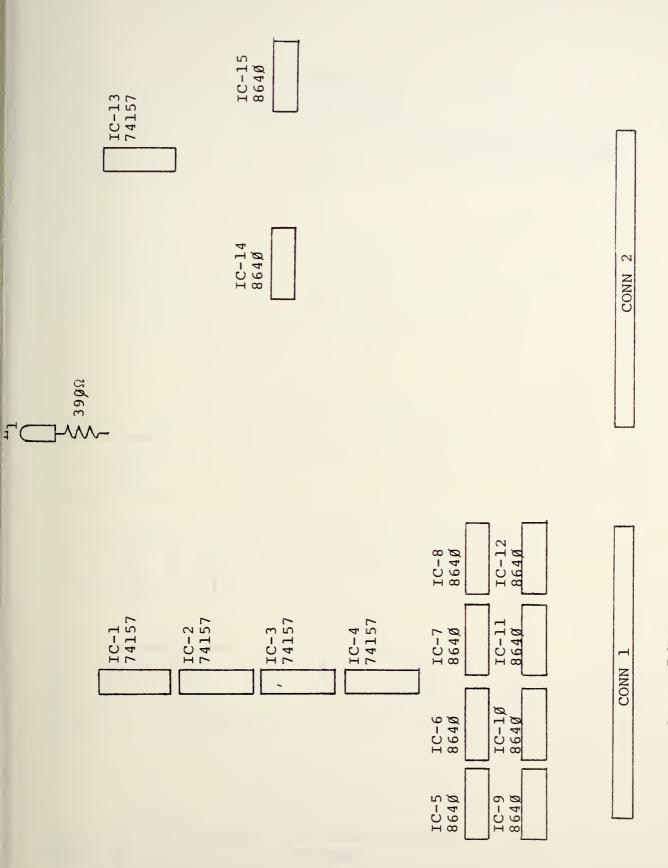

modifications. Originally the internal buffer memories were addressed by the internal Address Register (3) on board ten (10). Those internal DAU Address lines now come to board (15) to multiplex with AP/IOP-16 address lines. The AP Address lines APA00 through APA11 enter board (15) through 8640 line receivers, IC's 1 through 6. Note again each line runs through two 8640 gates for an inversion (see Figure 12). This results in the lines being compatible with the DAU address lines and the address line drivers on DAU board 12-1, see Figure 13. The AP address lines and DAU address lines meet at IC-9-12, 74154's, QUAD one of two Data Selectors.

Figure 12

TYPICAL COMBINATIONAL LOGIC FOR AP DATA

AND ADDRESS LINES THROUGH 8640 RECEIVERS ON DAU BOARD 15

Figure 13 DAU BOARD 12-1

The line then selected addresses the buffer memories through the line drivers on board (12-1). The select line logic will be discussed later.

Probably the most important IC in these new modifications is IC-24, a 74154 one of sixteen data selector. IC is the Master Controller, i.e. it selects which device of the AP and 7/32 will control the data lines, address lines, and control lines. Note that its five inputs are COT lines  $\emptyset 4\emptyset - \emptyset 7\emptyset$  and DAGØ from the 7/32. These are the same COT lines that are multiplexed with AP address lines on board three (3), however, these COT lines are not associated with MCOT lines. They are only used to address one of two locations on IC-24, i.e. outputs 6 or 7 (HEX Ø11Ø or Ø111). Due to an initial design deficiency the COT lines were not buffered by HEX inverters 7404's prior to entering IC-24 as required of 7/32 lines. Hence in reality output lines 9 and 8 (HEX 1001 and HEX 1000) are used. These perform the same function as if the COT lines had been inverted prior to IC-24. If output (6) is selected by the COT lines, it puts a direct clear signal on IC-23, a D- flip-flop. IC-23 is the Select flip-flop, see Figure 14. It selects either the AP or 7/32 for control. If output (6) is selected the direct clear puts a logic  $\emptyset$  at Q, pin 9. Pin 9 of IC-23 then goes to switch 2, a 4 pole double-throw switch. Switch one (1) and Switch two (2) were installed on board 15 to guarantee use of the DAU under 7/32 control while

Figure 14 DAU BOARD 15

Figure 15

POSITIONS OF CONTROL SWITCHES

1 AND 2 ON DAU BOARD 15

modifications were under static test of AP control (see Figure 15). This feature allows students to exercise the DAU as discussed in references  $\sqrt{2}$  and  $\sqrt{3}$  and enables testing of the AP controls if the switch is toggled. One output of switch  $S_2$  goes to pinout 15-2-31 and to light  $L_4$ . If in normal operation this output is from pin 9 of IC-23. If in 7/32 only guaranteed, the input to pinout 15-2-31 and light  $L_4$  is hardwired to ground. Note this lights  $L_4$  indicating 7/32 operational control. Pin 8 of IC-23 also goes to one of the poles of  $S_2$ . In the normal mode it outputs to  $L_1$ . If in the 7/32 only guaranteed mode, the output to  $L_1$  is hardwired to (+5) guaranteeing  $L_1$  will be off since  $L_4$  would be on indicating 7/32 control.

Should address 7 (HEX Ø111) be selected by the COT lines of IC-24 a clock pulse goes into pin 11 of IC-23 the Select flip-flop. This clocks a logic (1) through to pin 9. So if  $S_2$  is in the normal mode, a logic 1 (+5) at pin 9 turns off  $L_4$ . A logic 1 (+5) at pin 9 means a logic ( $\emptyset$ ) (ground) at pin 8. With  $S_2$  in normal mode this turns on  $L_1$  indicating the AP has control. Thus it can be seen that pinout 15-2-31 (see Figure 14) indicates which device has control. This line connects to pinout 3-2-3 on board (3) to put the MDOT and MCOT selectors under 7/32 or AP control as alluded to earlier.

Two of the most important signals used in the original DAU configuration were DAGØ, Data Available Gated (active low) as mentioned in \_\_1\_7 and \_\_2\_7. DAGØ from the 7/32 was used to setup the acquisition mode and DRGØ to read out acquired data. The only signal available with similar characteristics from the AP/IOP-16 is BUSMASTER (BUSM). Since the AP/IOP-16 has only one signal available, to be compatible with previous DAU operations it had to be capable of creating signals similar in characteristic to DAGØ and DRGØ. This imitation of DAGØ and DRGØ originates at IC-2Ø on board 15, see Figure 14. IC-2Ø is a 74155, Dual one-of-four data distributor.

BUSM enters at pin 1 and pin 15 and pin 1 of IC-20 as the data to be passed through the outputs to form signals representing DAGØ and DRGØ. BUSC and BUSM are used as address inputs at pins 3 and 13 respectively. If BUSC is high (+5) and BUSM is low (ground) BUSDAGØ is selected as the output at pin 5 where it is an inverted form of BUSM. If BUSC is low (ground) and BUSM is low (ground) BUSDRGØ is selected as the output at pin 7 where it is an inverted form of BUSM. The desired truth table is shown in Figure 16. With respect to BUSC and BUSM, these signals are inside the DAU after the line receivers and hence have the same logic state as internal to the AP/12ØB prior to the line drivers.

NOTE: If BUSM is low (ground) BUSDAGØ and BUSDRGØ are always high (+5). For BUSC and BUSM in Figure 16, Ø = ground and 1 = +5 volts.

| A <sub>1</sub><br>BUSC | A <sub>Ø</sub><br>BUSM | DATA | OUTPUT<br>1Y2<br>BUSDAGØ | OUTPUT<br>lyø<br>BUSDRGØ |

|------------------------|------------------------|------|--------------------------|--------------------------|

| Ø                      | Ø                      | 1    | 1                        | Ø                        |

| ø                      | 1                      | Ø    | 1                        | 1                        |

| 1                      | Ø                      | . 1  | ø                        | 1                        |

| 1                      | 1                      | ø    | 1                        | 1                        |

Figure 16

TRUTH TABLE FOR BUSDAGØ AND BUSDRGØ

The original 7/32 signal that was used to setup the DAU into an acquisition mode or to load diagnostic data was DAGØ. This signal can be represented by the AP/IOP-16 BUSM when it forms BUSDAGØ. BUSDAGØ is the output of pin 5 of IC-2Ø. BUSDAGØ (pin 5 of IC-2Ø) goes to pin 3 of IC-17, a one shot multivibrator. As BUSDAGØ transitions high to low (+5 to ground) it fires IC-17. This firing forms a negative pulse at output  $\overline{Q}$ , pin 1 of IC-17. This negative pulse goes as BDAGØ to IC-19 where it "ANDS" with 7/32 DAGØ to form MDAGØ (MASTER DAGØ). MDAGØ replaced 7/32 DAGØ internal to the DAU. Note if 7/32 is active vice AP, MDAGØ is formed by 7/32 DAGØ; if AP is active vice 7/32, MDAGØ is formed by BDAGØ.

The output pin 1 of IC-17 also goes as BUSYN(S) to pin 13 of IC-1 $\emptyset$ , the BUSYN flip-flop. The (S) is representative of "SETUP" mode. BUSYN(S) is a negative pulse that puts a direct clear signal at IC-1 $\emptyset$ . This direct clear puts a "1" at pin 8 of IC-1 $\emptyset$ , which sends an active low signal BUSYN back to the AP. When the AP/IOP-16 receives this BUSYN low, as discussed in section III, it removes BUSM, i.e. brings BUSM to (+5) on the bus. As BUSM is brought to (+5) it is inverted by its receiver. This inversion puts a " $\emptyset$ " at pin 1 $\emptyset$  of IC-1 $\emptyset$  which direct sets the BUSYN flip-flop, putting a " $\emptyset$ " at  $\overline{\mathbb{Q}}$ , pin 8 of IC-1 $\emptyset$ . This completes one cycle of the SETUP mode and the DAU is ready for another BUSDAG $\emptyset$  (BUSM) from the AP/IOP-16. Finally note that MDAG $\emptyset$

at pinout 15-2-20 of board (15), Figure 15, goes to pinout 8-1-15, Figure 9, to setup the internal DAU registers.

MDAGØ is routed on board 8, Figure 9, to DAGØ (1), DAGØ (2), DAGØ (3), etc., as appropriate.

BUSDRGØ is the other signal formed from BUSM at IC-2Ø pin 7, Figure 15. This signal is formed to be comparible with 7/32 DAGØ. BUSDRGØ leaves pin 7 of IC-2Ø and goes to pin 3 of IC-15 and pin 3 of IC-16, the Block Mode and Toggle Mode one shot multivibrators respectively.

## 4. Block Mode Read

The Block Mode, as alluded to earlier, is used for high sample rates (can be used for low also < 700 KHz) to transfer data (read) to the AP from the DAU by "blocks" after a block is acquired. The Toggle Mode is used for low sample rates only to DMA transfer data to the AP on a word by word basis as it is acquired. The Toggle Mode cannot be used above 700 KHz, theoretically, because of timing required in the DMA transfer compared with high speed conversion time of the A/D converters. These two modes will be explained separately.

Prior to commencing an acquisition mode, the user must determine how the data is to be read, i.e. Block Mode or Toggle Mode. These modes are selected at IC-23, the BM flip-flop. During the SETUP mode just prior to acquisition, the user sends out a DAG $\emptyset(9)$  pulse or a DAG $\emptyset(8)$  pulse from pinouts 8-1-34 or 8-1-36, Figure 9 respectively. If DAG $\emptyset(9)$

is sent pin 3 of IC-23 clocks a "1" at pin 5, Q, the Block Mode Point (BMP). Note this output goes to switch  $S_1$ . When in the 7/32 only guaranteed mode  $S_1$  outputs a (+5) to  $L_3$  to turn it off,  $L_3$  is the Toggle Mode;  $S_1$  outputs a (ground) to  $L_2$  to turn it on,  $L_2$  is the Block Mode light. The 7/32 "knows" only Block Mode and hence cannot use Toggle Mode  $(\overline{BMP})$ . If  $S_1$  is in the normal position, the AP/IOP-16 can select either BMP or  $\overline{BMP}$  by sending DAGØ(9) or DAGØ(8) respectively. Note when BMP is a "1"  $\overline{BMP}$  is a "Ø". This will be important in enabling and disabling IC-15 and IC-16.

In the Block Mode the AP/IOP-16 must wait to DMA transfer a "block" of data until the block is fully acquired. The signal that indicates completion of acquisition is WCØ at pinout 15-2-18, Figure 15. WCØ is a status signal from board 8 pinout 8-2-9, Figure 9. WCØ is high (+5) during acquisition and at completion goes low (ground). This high to low transition is inverted by IC-18 pins 1 and 2 on board 15, Figure 15. This inversion forms a low to high transition,  $\overline{WC\emptyset}$ .  $\overline{WC\emptyset}$  is used to clock pin 3 of IC-10, the WCØ flip-flop. Note prior to clocking IC-lØ had been direct cleared by the "AND" of DAGØ(5) with BUSC at IC-19. This "AND" creates an active low pulse at pin 3 of IC-19 to direct clear IC-23 whenever DAG $\emptyset$ (5) is active or BUSC is low at pin 13 of IC-20. The purpose of this clearing is to insure a "Ø" at  $\overline{\mathbb{Q}}$ , pin 5 of IC-23, prior to the end of an acquisition block, i.e. before WCØ goes low. A review of reference (2)

indicates that  $DAG\emptyset(5)$  is the last signal in the SETUP mode, appropriate for clearing IC-23 prior to reading. The importance of having a "Ø" at Q pin 5 of IC-23 prior to  $\overline{WCØ}$ clocking at pin 3 is to insure a "1" passes to Q, pin 5 after clocking. When Q, pin 5 of IC-23, goes to a "1" state it "ANDS" with BMP at IC-19. Note BMP was previously set to a "1", if not, pin 6 of IC-19 would be disabled. With a "1" at pin 5 of IC-19, pin 6 of IC-19 will follow the input at pin 4 of IC-19. Thus when Q, pin 5 of IC-10, goes to a "1" state it puts pin 6 of IC-19 to a "1" state and this fires IC-15 for the first time and data is read. Note pin 5 of IC-15 will stay in a "1" state until either BMP goes low or WCØ flip-flop is direct cleared. Also, as Q at pin 5 of IC-10 went high, a delayed high was placed on pin 4 of IC-15, a condition required for the initial triggering. Again if Q of WCØ flip-flop goes low, a delayed "Ø" will be placed on pin 4 of IC-15 enabling pin 5 of IC-15 to initiate the first trigger. Successive triggering is enabled by BUSDRGØ at pin 3 of IC-15. As IC-15 is fired, a negative pulse is sent at pin 1 of IC-15 (BDRGØ(B)) where (B) is associated with Block Mode. Pin 1 of IC-15 goes to pin 10 of IC-12 where  $BDRG\emptyset(B)$  (also BUSYN(B)) "ANDS" with  $BDRG\emptyset(T)$  (also BUSYN(T)). When BDRG $\emptyset$ (B) is active, BDRG $\emptyset$ (T) will always be in a "1" state and vice versa. Thus the output, pin 8 of IC-12 follows the active input. Pin 8 of IC-12 goes to pin 4 of IC-12 where it "ANDS" with 7/32 DRGØ to form MDRGØ.

MDRGØ follows the active input, i.e. if 7/32 is active, BDRGØ(B) and BDRGØ(T) are "1"; if AP is active, 7/32 DRGØ is a "1". Pin 8 of IC-12 is also inverted at pins 5 and 6 of IC-11 to form a signal BUSYN(A). BUSYN(A) is a clock signal to clock a "1" to  $\overline{\mathbb{Q}}$ , pin 8 of IC-10. This "1" goes to the AP as BUSYN and remains a "1" until the AP brings BUSM to (+5) which is inverted at its receiver to direct set pin 10 of IC-10 removing BUSYN in the "handshake" process and ready the AP and DAU for another cycle.

# 5. Toggle Mode Read

The Toggle Mode design is considerably more complex than the Block Mode. As in the Block Mode, selection of Toggle Mode must be made prior to commencement of an acquisition scheme. With the AP in control, a DAGØ(8) is sent out just prior to the DAGØ(5) that starts acquisition. DAGØ(8) comes from board eight (8) onto board (15) at pinout 15-2-27, where active low pulse proceeds to apply a direct clear signal at pin 1 of IC-23. This direct clear puts a "Ø" at Q, pin 5 of IC-23 and a "1" at  $\overline{Q}$ , pin 6 of IC-23. The "Ø" at Q and "1" at  $\overline{Q}$  turns on the Toggle Mode light,  $L_3$ , and turns off the Block Mode light,  $L_2$ , respectively (Figure 15). Note again, if hardwired to 7/32 only operation at  $S_1$  the Toggle Mode light is off and Block Mode on.

In the Toggle Mode, the design was for use under 700KHz since the DAU could acquire and not theoretically affect AP processing at this rate and slower rates.

The last signal sent to set up the DAU to acquire data is DAGØ(5). As seen on board 8, Figure 9, this signal sets the internal control register of the DAU, to acquire data. Now as the DAU acquires a word of data and stores it in Buffer Memory, in the Toggle Mode, the AP will read out that same word prior to the next word acquisition. Thus the AP and DAU "toggle" between an acquisition and a read versus acquiring a "block" and reading a "block". As mentioned earlier (Section III) the DMA timeout can be adjusted to suit the user's needs.

The theory behind the Toggle Mode design is that the AP/IOP will set up the DAU using BUSDAGØ signals and after  $DAG\emptyset(5)$  is generated the AP/IOP will immediately send out a BUSDRGØ signal waiting to read the first acquired word. BUSDRGØ goes to a low level, it puts a "Ø" on pin 3 of IC-16, the Toggle Mode one shot multivibrator. Note for the one shot, IC-16, to fire in this configuration, pin 4 must also be low, a " $\emptyset$ ", and pin 5 must be brought from ground (" $\emptyset$ ") to positive (+5). A " $\emptyset$ " is put at pin 4 by the Toggle Mode flip-flop, IC-14. As a word is acquired, the write timer IC-12 on board 16 fires, putting a positive pulse at Q, pin 6 of IC-12 board 16, and a negative pulse at  $\overline{Q}$ , pin 1 of IC-12 board 16 (see Figure 17). This negative pulse enters board 15 at pinout 15-2-22 and goes to three different IC gates, i.e. IC-12, IC-13, IC-14. At IC-14  $\overline{Q}$  of the Write Timer is a negative pulse that is used to direct clear, i.e.

put a " $\emptyset$ " at Q pin 9 of IC-14. This effectively puts a " $\emptyset$ " at pin 4 of IC-16 board 15.

The Toggle Mode one-shot, IC-16, is now set up for a trigger. With pin 3 low and pin 4 low, a ground to positive transition at pin 5 will fire IC-16. This ground to positive transition is enabled by the signal SSYNCBØ(1) / 2/.

SSYNCBØ(1) is a negative pulse that enters board 15 at pinout 15-2-17. The trailing edge of the pulse clocks IC-14 at pin 3 and the high to low to high transition brings the output pin 11 of IC-19 from high to low to high. This latter transition fires the Toggle Mode one-shot. Conveniently, SSYNCBØ(1) also clocks pin 11 of IC-14 which puts a "1" at Q, pin 9 of IC-14 and effectively at pin 4 of IC-16 to put it in the proper state for the next triggering. Note the propagation delay through IC-14 is sufficiently greater than that through IC-19 to allow the initial firing above.

Since DAU loads its buffer memory in parallel, but the AP/IOP is capable of reading only one channel of data at a time  $\sqrt{1}$  and  $\sqrt{2}$ , the Toggle Mode design must insure there are two read (BDRGØ) pulses before the next acquisition write pulse. Note from the above discussion the SSYNCHBØ(1) pulse has created a "1" at pins 4 and 5 of IC-16. Thus to obtain a pulse at  $\overline{Q}$ , pin 1 of IC-16, there must be a positive to ground transition at pin 3 of IC-16. This positive to ground transition results from the BUSDRG signal. Note that the BDRGØ(T) pulse creates a BUSYN signal to handshake with

O TEST POINT

the AP/IOP in a similar fashion to that of BDRGØ(B) in the block mode.

There are two more important points to discuss before leaving the Toggle Mode design: 1) How to obtain two and only two read pulses from the AP/IOP between word acquisitions; 2) How to avoid a read pulse at an inappropriate time.

The user will always want at least two read pulses after a word acquisition, so the real problem is to insure not more than two read pulses occur after a word acquisition. This problem is handled by the limit flip-flop, IC-14. From /1 / and /2 / and analysis of DAU board 16, Figure 17, it is seen that two read pulses, i.e. MDRGØ, create one SSYNCBØ pulse. A SSYNCBØ pulse is also created upon word acquisition. The SSYNCBØ pulse comes on to board 15 at pin out 15-2-10 and goes to pin 3 of IC-25. This SSYNCBØ signal is divided by two at Q, pin 5 of IC-25. Thus every other SSYNCBØ creates a level change at Q, pin 5 of IC-25. To insure IC-25 starts in the proper state it is preset by a DAG $\emptyset$ (5) pulse at pin 4 of IC-25. The ground to positive level change created by IC-25 is used to clock pin 3 of IC-14, the LIMIT flip-flop. This clocking puts a "1" at Q, pin 5 of IC-14. Note previously Q, pin 5 of IC-14, was at a " $\emptyset$ " being direct cleared by the DAGØ(5) pulse or the pulse from Q of the WRITE TIMER, IC-12 on board 16. Thus Q, pin 5 of IC-14, was in a "Ø" state while the two read pulses were

active. When pin 3 of IC-14 is clocked a "1" is put at Q, pin 5. This "1" "ORS" with the signal from the Toggle Mode one shot at IC-13. Since pin 5 of IC-13 is a "1", the user is guaranteed a "1" at pin 6 of IC-13. This insures a "1" at pin 9 of IC-12 (note pin 10 of IC-12 is a "1" because Block Mode is not is use). Thus no more MDRG0 pulses can be created and the user has only two read pulses for each word acquisition.

The second problem was to avoid a read pulse at an inappropriate time. In the Toggle Mode the only appropriate time to read a word is immediately after the word has been written into memory. This time occurs immediately after the write enable pulse (WE) on IC-13 board 16 Figure 17. From /1 7 and /2 7 it should be noted that a  $\overline{WE}$  pulse also occurs after every second read pulse (DRGØB2). It is specifically this WE pulse that must be disabled so as not to affect the Toggle Mode. This WE pulse is eliminated as follows. The WE pulse is disabled through pinout 15-2-9 by many possible signals through IC-13 as can be seen on board 15 Figure 15. One input to IC-13 at pin 12 is a signal through  $S_2$  from pin 3 of IC-12. When  $\overline{BMP}$  is a "1" pin 3 of IC-12 follows the input at pin 1. The input at pin 1 to IC-12 is pin 8,  $\overline{Q}$ , from IC-25. IC-25 is clocked at pin 11 by a delayed version of DRGØB2. Thus while pin 8 of IC-25,  $\overline{Q}$ , is in a "1" state, the disable  $\overline{WE}$  line at pinout 15-2-9 is high and the buffer memories cannot be written.  $\overline{\mathbb{Q}}$ , pin 8

of IC-25, stays in a "1" state until clocked by the delayed version of DRG $\emptyset$ B2, so the  $\overline{WE}$  pulse is eliminated. Note that  $\overline{\mathbb{Q}}$ , pin 8 of IC-25, was put in a "1" state by the signal  $\overline{\mathbb{Q}}$  of the write times. It was this signal that originally wrote good data into memory during acquisition.

Another signal of interest in the Toggle Mode occurs at pinout 15-2-13. Again, from /1/7 and /2/7, it is the SSYNCB(2) signal on board 8 that updates the DAU word count and address registers. This updating must be eliminated until after the acquired word has been read. In the Block Mode these registers are updated after each word acquisition so data is stored in appropriate addresses and the word count is decremented. However, in the Toggle Mode if the address and word count are updated prior to the read cycle, undesireable data will be read. The word count and address registers are disabled via pinout 15-2-13. This connection goes onto board 8 at pinout 8-2-11, to two NAND gates, 7438 drivers. The word count and address registers are enabled if output pins 3 and 6 of IC-1 $\emptyset$  are in a " $\emptyset$ " state. For this to occur inputs 1, 2, 4 and 5 must all be in a "l" state. Note that in the "7/32 only mode",  $S_1$  hardwires 8-2-11 and hence inputs 1 and 4 to a 1. In the "normal" mode, S1 allows the output pin 3 of IC-26 to pass to pinout 8-2-11. The output, pin 3 of IC-26 is fed by inputs 1 and 2, BMP and Q, pin 9 of IC-25 respectively. In the Toggle Mode, BMP is a " $\emptyset$ " thus pin 3 of IC-26 fo-lows pin 1 input. So when Q, pin 9

of IC-25 is a "Ø" SSYNCB(2) cannot update the word count and address registers. This output Q, pin 9 of IC-25 is a "Ø" when cleared by  $\overline{Q}$  of the WRITE TIMER, IC-12 on board 16. Thus immediately after a word is written into buffer memory, the address and word count cannot change until the word is read out, i.e. after the second read DRGØB(2) pulse. This is important because now the AP/IOP need not generate address to read data from buffer memory, it need merely follow the address the DAU writes.

For the convenience of monitoring signals and status there are five test points and five lights on board 15. The test points monitor the following signals:  $T_1 \rightarrow BUSM$ ,  $T_2 \rightarrow BUSYN$ ,  $T_3 \rightarrow BUSC$ ,  $T_4 \rightarrow MDRG\emptyset$ ,  $T_5 \rightarrow MDAG\emptyset$ . The lights indicate status as follows:  $L_1 \rightarrow AP/IOP$  in control,  $L_2 \rightarrow Block$  Mode,  $L_3 \rightarrow Toggle$  Mode,  $L_4 \rightarrow 7/32$  in control,  $L_5 \rightarrow 7/32$ (on) or AP/IOP(off) addressing buffer memory. On board 3,  $L_1$ , indicates which device controls the data lines, i.e. 7/32(on) or AP/IOP(off) (see Table 3).

The control (BUSC, BUSM, BUSYN) signals enter the DAU on board 12-2 in a configuration the same as Figure 18. BUSM and BUSYN transit the usual driver/receiver logic compatible with interface design. BUSC must drive many more gates. To increase its fanout, BUSC was sent separately to various locations as shown in Figure 18. The BUSC lines are also driven by standard drivers as shown in Figure 18.

TABLE III

TEST POINTS AND LIGHTS ON DAU BOARD 15

| TEST POINTS            | <u>LIGHTS</u>                                                  |

|------------------------|----------------------------------------------------------------|

| T <sub>1</sub> → BUSM  | L <sub>1</sub> → ON → AP IN CONTROL                            |

| T <sub>2</sub> → BUSYN | L <sub>2</sub> → ON → BLOCK MODE                               |

| T <sub>3</sub> → BUSC  | L <sub>3</sub> → ON → TOGGLE MODE                              |

| T <sub>4</sub> → MDRGØ | $L_4 \rightarrow ON \rightarrow 7/32$ IN CONTROL               |

| T <sub>5</sub> → MDAGØ | $L_5 \rightarrow ON \rightarrow 7/32$ ADDRESSING BUFFER MEMORY |

|                        | L <sub>5</sub> → OFF → AP ADDRESSING BUFFER MEMORY             |

NOTE:  $L_1$  and  $L_4$  cannot be on simultaneously  $L_2$  and  $L_3$  cannot be on simultaneously

Figure 18 DAU BOARD 12-2

Figures 19 and 20 show the Block Mode and Toggle Mode timing diagrams respectively.

Figure 19

BLOCK MODE READ TIMING DIAGRAM

TOGGLE MODE READ TIMING DIAGRAM

Figure 20

## V. FLOATING POINT SYSTEMS AP-120B (AP) SIMULATOR

#### A. INTRODUCTION

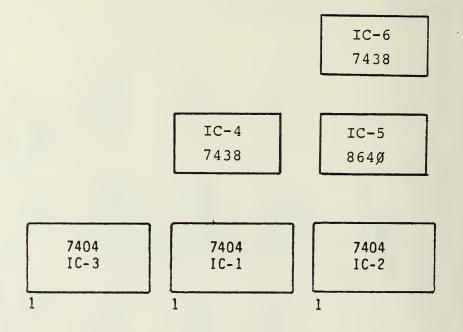

As with any device designed to operate at computer speeds, action takes place in the DAU/IOP interface at speeds which make direct observations nearly impossible. To initially test and design, it is desirable to make essentially "static" tests at speeds observable to the human eye. To this end, and to simulate AP control of the DAU the AP simulator was constructed. When connected to the DAU in place of the AP the simulator effectively represents the AP.

### B. AP SIMULATOR OPERATION

The AP Simulator circuit shown in Figure 21 consists of control signals, bidirectional data lines, and address lines to represent the AP. The control signal BUSC is represented by a single pole double throw switch. One side of the switch is tied to +5 volts the other to ground. The output goes to the data line IC's in the simulator, the BUSC light and to the backplane for transfer to the DAU. The control signal BUSM is represented by a 3 pole double throw switch. Two poles go to debounce Logic as shown in Figure 21. The third pole goes to the BUSM light. The output of the debounce logic goes to the DAU via the ribbon cable. The control signal BUSYN is represented by a light, there is no need for a switch since all transfers will be under AP

AP SIMULATOR CIRCUIT SCHEMATIC

63

control the DAU will always be sending back BUSYN. The data lines are represented by single pole double throw switches and 7400 Nand gates. One side of the switch is ties to +5 volts and the other is tied to ground. The output of the data switch is one input to a 7400 nand gate; the other input is a line from BUSC. The output of the nand gate goes to the respective data line at the backplane and the respective light on the front panel. The lights (LED's) have internal current limiting resistors. Note when BUSC switch is up a +5 is applied to one input of each nand gate. Thus the output will follow the other input, i.e. the data line. Note the output in this case can source approximately 400 microamperes. When BUSC switch is down one input to each gate is at ground, meaning the output will always be a Logical "1". In this case the output can sink 16 miliamperes. The result is a representation of bidirectional data lines, direction dependent on BUSC. The address lines are represented by single pole double throw switches. One input is tied to +5 the other is ties to ground. The output goes directly to the back plane of the simulator. All these lines are summarized in Table IV.

### C. USE OF AP SIMULATOR

The AP Simulator can be used independent of or in conjunction with the DAU Tester /2/ to control the DAU. If control is passed to the AP Simulator (see Section IV-C) then it can set up the DAU to acquire data and ultimately read that data as if the AP were actually reading data.

### TABLE IV

#### AP SIMULATOR SUMMARY

- I. BUSC Controls Flow of Data

HI (Light On) at Simulator → Send Mode BUSC

will be HI in DAU

LO (Light Off) at Simulator → Receive Mode

BUSC will be LO in DAU

- II. BUSM HI (Light On) at Simulator → Transition ↑ → Transition ↑ in DAU Signal Active HI to DAU

- III. BUSYN HI (Light On) at Simulator → Transition ↓ in DAU Signal Active HI in DAU

- IV. DATA LINES HI (Light On)  $\rightarrow$  1 Sent or Received LO (Light Off)  $\rightarrow$   $\emptyset$  Sent or Received

- V. ADDRESS LINES UP  $\uparrow$   $\rightarrow$  1 Sent to DAU Register DN  $\downarrow$   $\rightarrow$   $\emptyset$  Sent to DAU Register

- NOTE: (1) AP-12 $\emptyset$ B Address Line  $\emptyset$  is Always <u>LO</u>

- (2) AP Simulator Lines 18, 19 N/A

|         | SWITCH | LIGHT | CABLE | AFTER LINE<br>RCVR IN DAU |

|---------|--------|-------|-------|---------------------------|

| BUSC    | UP     | ON    | LO    | HI                        |

|         | DN     | OFF   | HI    | LO                        |

| BUSM    | UP     | ON    | LO    | HI                        |

|         | DN     | OFF   | HI    | LO                        |

| BUSYN   | N/A    | ON    | LO    | HI                        |

|         |        | OFF   | HI    | LO                        |

| DATA    | UP     | ON    | LO    | HI                        |

|         | DN     | OFF   | HI    | LO                        |

| ADDRESS | UP     | N/A   | LO    | HI                        |

|         | DN     |       | HI    | LO                        |

For example, to set up the registers in the DAU use address lines 12-15 to address the appropriate DAU registers, i.e. range register #1 is addressed by putting line 12 high (HEX 1). Frequency register #2 is addressed by putting address line 13 high (HEX 2). Word count #3 is addressed by putting address lines 12 and 13 high (HEX 3). Word count data is passed over the 16 data lines in conjunction with addressing register 3. Address register #4 in the DAU is addressed by setting AP address line 14 high (HEX 4). Simultaneously the starting address is loaded from the data lines. The control register, #5, is addressed by setting AP address lines 14 and 12 high (HEX 5). Simultaneously the control function is set by appropriate data on the data lines, i.e. high speed analog to digital conversion, low speed analog to digital conversion, diagnostic write, etc. Note also the AP simulator uses a block mode and toggle mode with respect to reading (see Section IV-C). These mode are set by putting AP address lines 15 and 12 (HEX 9) or 15 along (HEX 8) high respectively. In all cases the appropriate register is addressed and data strobed into the DAU by first addressing the register, setting the data, put BUSC switch up (send mode) and enabling BUSM (bring switch down). Note that the data is latched into the DAU at the proper register when the BUSYN light goes on at the AP Simulator panel. To remove the BUSYN light, bring the BUSM switch up again. This process is continued until the appropriate registers are loaded with the desired data.

The AP simulator can be used with the DAU tester to statically check an acquisition of data and a block mode read as follows. Initially use the DAU Tester. Set the DAU word count register to  $\emptyset\emptyset\emptyset8$  HEX. This implies we will load in eight words (note one word goes into Channel I and Channel II by pushing the DAGØ switch twice). Set the DAU address register to 9999 HEX. Set the DAU control register to 7/32 WR ØØØ8 HEX and the DAU is set up to receive diagnostic data. Now load the eight desired words by appropriately selecting the data lines. As the word count register counts down and hits ØØØØ, a signal is set to transfer control of the buffer memory address lines from the DAU tester to the AP simulator. This can be noted by observing light (5) on DAU Board #15, it should be on when the 7/32 is addressing buffer memory and off when the AP is addressing buffer memory. The word count equals zero status can also be observed by monitoring the status in line (7).

When control of the buffer memory address lines switches from 7/32 to the AP the data previously written in can be read out as follows. Set the BUSC switch down for receive mode. Next set the desired location in memory to read with the address lines. In this example start at  $\emptyset\emptyset\emptyset\emptyset$  and work to address  $\emptyset\emptyset\emptyset\emptyset$  using address lines  $\emptyset$  through ll. The data read will show on the data lines and should correspond to what was loaded by the DAU tester. To read a word from

channel one drive the BUSM switch down, the data will then appear and the BUSYN light should come on. Repeat without changing address to read from channel two. This process is summarized in Table V.

TABLE V

AP SIMULATOR OPERATION

Address Data

| Mode                  |   | Lines<br>Switches   | Lines<br>Switches | BUSC<br>Switch | BUSM<br>Switch | Comments                                                             |

|-----------------------|---|---------------------|-------------------|----------------|----------------|----------------------------------------------------------------------|

| SETUP<br>DAU          | 1 | 12 UP               | ØØØ6 НЕХ          | UP             | DN             | When BUSYN lights data set in DAU, bring BUSM up to remove BUSYN     |

|                       | 2 | 13 UP               | 2000 HEX          | UP             | Dμ             | "<br>Sets in<br>2ØØKHz                                               |

|                       | 3 | 12,13 UP            | Ø4ØØ HEX          | UP             | DN             | " Sets WC to 1Ø24                                                    |

|                       | 4 | 14 UP               | <b>д</b> ддд нех  | UP             | DN             | Sets ADD to                                                          |

|                       | 5 | 14,15 UP            | ØØ22 HEX          | UP             | DN             | High Speed<br>ACQ                                                    |

|                       |   |                     | ØØ11 HEX          | UP             | DN             | Lo Speed<br>ACQ                                                      |

|                       |   |                     |                   |                |                |                                                                      |

| BLOCK<br>MODE<br>READ | 1 | Load data reference | with DAU Test     | er as de       | scribed        | l in text and                                                        |

| KEAD                  | 2 | To desired location | observe           | DN             |                | When BUSYN lights a word is read to re- move BUSYN, bring BUSM high. |

## VI. AP SOFTWARE

Programming the AP-12ØB in Array Processor Assembly

Language (APAL) is discussed in references \( \frac{4}{7} - \frac{7}{7} \).

In particular references \( \frac{4}{7} \) and \( \frac{5}{5} \), offer examples of programming techniques. The programmer inexperienced in assembly language will find a great deal of time required to diagnose and understand these manuals. References \( \frac{6}{7} \) and \( \frac{7}{7} \) list the language commands used by the AP-12ØB assembler. However, few examples are noted and again the uniniated programmer will find initial efforts very cumbersome but not impossible.

A sample program that can be used to set up the DAU in an acquisition mode is listed in Appendix A.

## VII. CONCLUSION

The interface between the Data Acquisition Unit and the AP-120B Array Processor has been designed and constructed for digital control. The interface has passed static testing satisfactorily. The interface has demonstrated the ability to command the DAU to acquire data under software program control. Implementation of this interface will enable further increases in efficiency in digital spectrum analysis performed by the SATCOM Signal Analyzer.

### APPENDIX A SOFTWARE PROGRAM

```

C

Ċ

SIMUL1

Ċ

Ċ

C

PROGRAM TO TEST AP/IOP DATA XFER TO DAU

Ċ

С

INTEGER WC2V, APMA2V, HMA2V, CLT2V

INTEGER*2 IVAL, IREG, DAUTO

C

C

С

SET UP DAU FOR AP CONTROL

C

C

WRITE (6,600)

600

FORMAT(/, 'INPUT D; INPUT REG NR; 6=7/32, 7=AP,

FORMAT(I1,1X,I1)')

READ (5,500) IVAL, IREG

500

FORMAT(I1,1X,I1)

CALL DAUREG (IVAL, IREG)

C

C

С

CLEAR AP

С

C

CALL APCLR

С

С

C

PUT DATA INTO AP MAIN MEMORY

С

C

2

WRITE (6,602)

FORMAT(/,'INPUT DATA TO SETUP DAU INTERNAL REG (Z4)')

602

READ (5,501) DAUTO

501

FORMAT (Z4)

CALL APPUT (DAUTO, 0, 1, 1)

CALL APWD

C

C

С

SET UP IOP FOR XFER

C

C

3

WRITE (6,603)

603

FORMAT(/,'INPUT DATA TO SETUP IOP XFER, (4(Z4,1X)')

READ(5,502) WC2V, APMA2V, HMA2V, CTL2V

FORMAT(4(z4,1X))

502

1

CALL TAP2A(8,WC2V,11,APMA2V,9,HMA2V,10,CTL2V)

CALL APWR

GO TO 2

END

```

### APPENDIX A (con't)

STITLE TAP2A \$ENTRY TAP2A,8 WC2 = 0WC2V = 1APMA2 = 2APMA2V = 3HMA2 = 4HMA2V = 5CTL2 = 6CTL2V = 7"POINT TO WC2 REGISTER TAP2A: MOV WC2, WC2; DB=SPFN; LDDA MOV WC2V, WC2V; DB=SPFN; OUT "SET WC2 TO ØØØ1 NOP "POINT TO APMA2 REGISTER MOV APMA2, APMA2; DB=SPFN; LDDA NOP MOV APMA2V, APMA2V; DB=SPFN; OUT "SET APMA2 TO DESIRED LOCA-NOP TION "POINT TO HMA2 REGISTER MOV HMA2, HMA2; DB=SPFN; LDDA NOP MOV HMA2V, HMA2v; DB=SPFN; OUT "SET HMA2 TO DESIRED LOCA-NOP ·TION "POINT TO CTL2 REGISTER MOV CTL2, CTL2; DB=SPFN; LDDA NOP "SET CTL2 TO DMA WRITE MOV CTL2V, CTL2V; DB=SPFN; OUT NOP RETURN \$END

### APPENDIX B

### DAU CIRCUIT BOARD SCHEMATICS

These must be used in conjunction with those in  $\sqrt{2}$ .

AP OR 7/32 DATA AND CONTROL SELECTOR DAU BOARD # 3

O TEST POINT

81

### APPENDIX C

### DAU BOARD COMPONENT LAYOUTS

These must be used in conjunction with those in  $\sqrt{2}$ .

AP Or 7/32 Address Line Selector And AP Interface Signals

AP Or 7/32 Data And Control Selector Component Layout

### DAU AUXILIARY BOARD 2

**BOTTOM**

FRONT

CONNECTOR 1

### APPENDIX D

### DAU WIRING LISTS

These must be used in conjunction with those in  $\sqrt{2}$ .

B-1-48

B-1-46

AP DATA 14 AP DATA 12 DATA 13 DATA 11

AP

3-1-12

3-1-10

3-1-8

3-1-6

3 - 1 - 2

3 - 1 - 4

FROM

AP DATA 1Ø

AP

3-1-14

3-1-16

DATA 8

AP

AP DATA 9 AP DATA 7 DATA 6

AP

3 - 1 - 243-1-26

3-1-22

AP DATA 4 AP DATA 5

B-1-42

B-1-34 B-1-36

B-1-38

B-1-44 B-1-40

B-1-17

B-1-14

B-1-16

B-1-15

B-1-13

B-1-12

B-1-1Ø

(ISB)

DATA Ø

DATA 1

3 - 1 - 363 - 1 - 34

DATA 3 DATA 2

AP

$3-1-3\beta$

3-1-28

3-1-32

B-1-11

3-1-18  $3-1-2\emptyset$

## WIRING LIST BOARD

|                     |          |        |        | -5                | 5.                | 33                | 7                              | 7                | 33                | 11                | 5                 | 35                         | 11                | 6                          | 33                | 22                              | 6                   | 27                  | 11                  |  |

|---------------------|----------|--------|--------|-------------------|-------------------|-------------------|--------------------------------|------------------|-------------------|-------------------|-------------------|----------------------------|-------------------|----------------------------|-------------------|---------------------------------|---------------------|---------------------|---------------------|--|

|                     | TO       | Ŋ      | Ŋ      | 12-2-15           | $1\beta - 1 - 15$ | $1\beta - 1 - 13$ | 1 <i>\theta</i> -1-17          | 1Ø-1-27          | 19-1-23           | $1\beta - 1 - 21$ | $1\beta - 1 - 25$ | 1Ø-1-3                     | 10-1-31           | 1 <b>ø</b> -1-29           | $1\beta - 1 - 33$ | 12-1-35                         | 12-1-29             | 12-1-2              | 12-1-21             |  |

| CONNECTOR #1 BOTTOM | FUNCTION | GND    | GND    | "B" TO 8640 RCVRS | DAU ADDR LINES 6  | DAU ADDR LINES 7  | DAU ADDR LINES (MSB)<br>(CS) 5 | DAU ADDR LINES 8 | DAU ADDR LINES 10 | DAU ADDR LINES 11 | DAU ADDR LINES 9  | DAU ADDR LINES 12          | DAU ADDR LINES 14 | DAU ADDR LINES (LSB)<br>15 | DAU ADDR LINES 13 | MASTER ADDR OUT (LSB) MAI $eta$ | MASTER ADDR OUT MA7 | MASTER ADDR OUT MA6 | MASTER ADDR OUT MA3 |  |

|                     | FROM     | 15-1-1 | 15-1-3 | 15-1-5            | 15-1-7            | 15-1-9            | 15-1-11                        | 15-1-13          | 15-1-15           | 15-1-17           | 15-1-19           | 15-1-21                    | 15-1-23           | 15-1-25                    | 15-1-27           | 15-1-29                         | 15-1-31             | 15-1-33             | 15-1-35             |  |

|                     | 인        | +5     | +5     | $B-4-6\beta$      | NC                | B-4-59            | B-4-58                         | B-4-64           | B-4-61            | B-4-63            | B-4-62            | B-4-68                     | B-4-65            | B-4-67                     | B-4-66            | 12-1-17                         | 12-1-15             | 12-1-25             | 12-1-23             |  |

| CONNECTOR #1 TOP    | FUNCTION | +5     | +5     | AP ADDR LINE 3    | AP ADDR LINE Ø    | AP ADDR LINE 2    | AP ADDR LINE (LSB) 1           | AP ADDR LINE 7   | AP ADDR LINE 4    | AP ADDR LINE 6    | AP ADDR LINE 5    | AP ADDR LINE (MSB) (CS) 11 | AP ADDR LINE 8    | AP ADDR LINE 1Ø            | AP ADDR LINE 9    | MADDR OUT MAI                   | MADDR OUT (MSB) MAØ | MADDR OUT MAS       | MADDR OUT MA4       |  |

|                     | FROM     | 15-1-2 | 15-1-4 | 15-1-6            | 15-1-8            | 15-1-10           | 15-1-12                        | 15-1-14          | 15-1-16           | 15-1-18           | $15-1-2\beta$     | 15-1-22                    | 15-1-24           | 15-1-26                    | 15-1-28           | 15-1-3Ø                         | 15-1-32             | 15-1-34             | 15-1-36             |  |

16-1-15 12-1-6 16-1-35  $1\beta - 2 - 26$ 12-2-24 12-2-28 15-2-24  $12 - 2 - 2\emptyset$ 12-2-25 15-2-8 16 - 2 - 38-2-11 8 - 1 - 368 - 1 - 343 - 2 - 3NC NC G G "SELECT" 732 OR IOP DAGØ(9)OUT DAGØ(8)OUT DRGØB 2 732 DAGØ Ø BUSC BUSM GND GND SSYNCH B1 15 - 2 - 3515-2-17 15-2-19 15-2-23 15-2-24 15-2-27 15 - 2 - 2915 - 2 - 3115 - 2 - 3315 - 2 - 218-1-15 16-2-7 8-2-9 B-1-9 B-1-5B-1-8 B-1-7 B-1-6 732 DAG Ø (BACKPLANE) O OF WRITE TIMER WC Ø MDAG Ø OUT +5 Ø10 COT Ø4Ø COT Ø5Ø COT Ø6Ø COT  $15 - 2 - 2\beta$ 15-2-22 15-2-24 15-2-26 15-2-28  $15 - 2 - 3\beta$ 15-2-32 15 - 2 - 3615-2-34

# WIRING LIST BOARD #15

CONNECTOR (1)

| TO       | Gnd   | Gnd   | 16-1-11       | 3-2-7       | 3-2-9       | 3-2-11      | 3-2-13        | 15-2-20   | 16-1-13                      | 10-2-12              | 10-2-14              | 10-2-10              | 10-2-6               | 10-2-24              | B-3-5       | B-1-3     | B-3-4           | 12-2-27    |

|----------|-------|-------|---------------|-------------|-------------|-------------|---------------|-----------|------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|-------------|-----------|-----------------|------------|

| FUNCTION | Gnd   | Gnd   | DAGØ(5) B Out | MCOT Ø4Ø In | MCOT Ø5Ø In | MCOT Ø6Ø In | MCOT \$7\$ In | MDAG Ø In | DAG $\beta$ -( $\beta$ ) Out | DAG $\beta$ -(1) Out | DAG $\beta$ -(2) Out | DAG $\beta$ -(3) Out | DAG $\beta$ -(4) Out | DAG $\beta$ -(5) Out | SIN Ø4Ø Out | SATNO Out | OVØ SIN Ø5Ø Out | SSYNØBØ In |