# CMOS Transistor Sizing (3G)

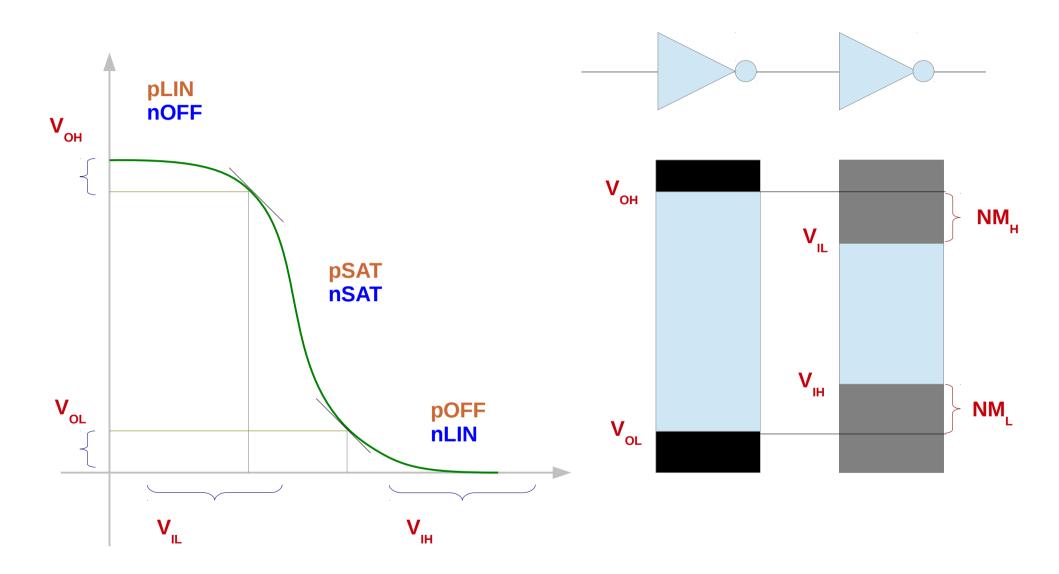

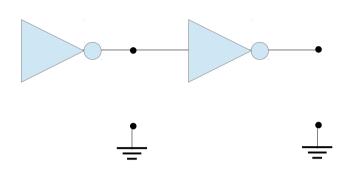

# Noise Margin

### Transconductance Parameter (1)

When

$$V_{GS} > V_{t}$$

and  $V_{DS} < (V_{GS} - V_{t})$

$$I_d = \frac{k' \frac{W}{L}}{L} \left[ (v_{gs} - v_t) v_{ds} - \frac{1}{2} v_{ds}^2 \right]$$

When

$$V_{GS} > V_{t}$$

and  $V_{DS} \ge (V_{GS} - V_{t})$

$$I_d = \frac{1}{2} \frac{k' \frac{W}{L}}{L} (v_{gs} - v_t)^2$$

$$\beta_{p} = k'_{p} \left(\frac{W}{L}\right)_{p}$$

$$\beta_{n} = k'_{n} \left(\frac{W}{L}\right)_{n}$$

### Transconductance Parameter (2)

When  $V_{GS} > V_{t}$  and  $V_{DS} < (V_{GS} - V_{t})$

$$I_d = \left[ \beta \left[ (v_{gs} - v_t) v_{ds} - \frac{1}{2} v_{ds}^2 \right] \right]$$

When  $V_{GS} > V_{t}$  and  $V_{DS} \ge (V_{GS} - V_{t})$

$$I_d = \frac{1}{2} \beta \left( v_{gs} - v_t \right)^2$$

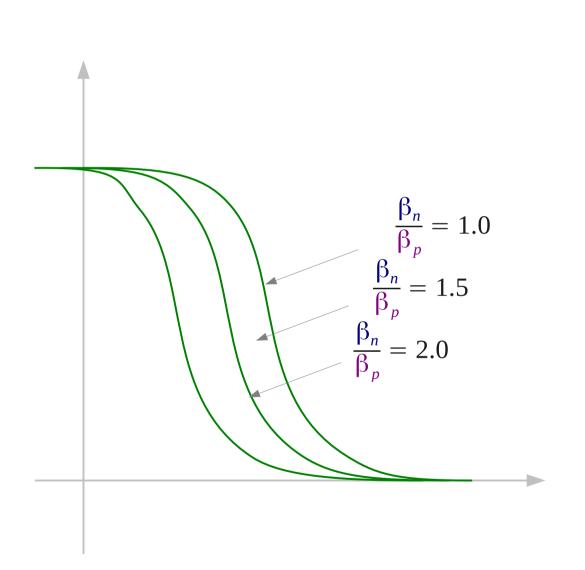

### Transconductance Parameter (3)

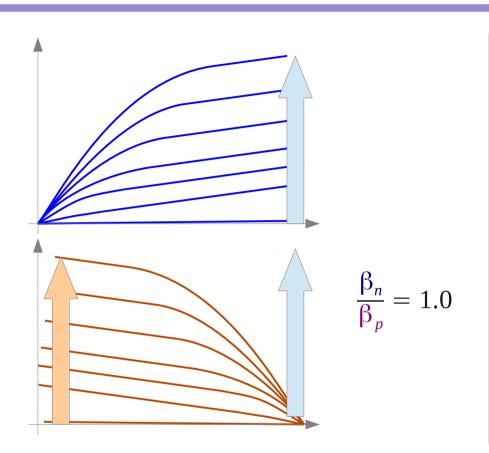

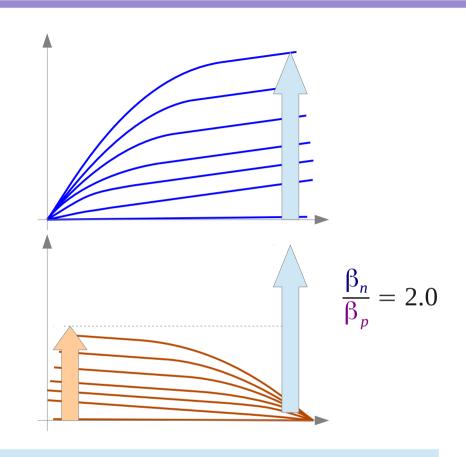

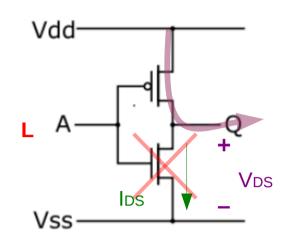

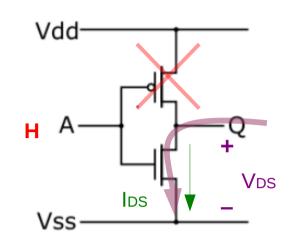

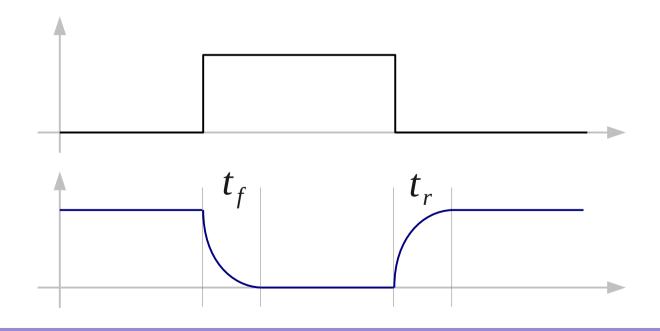

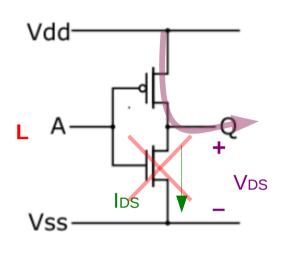

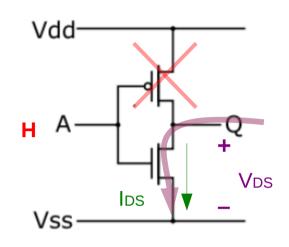

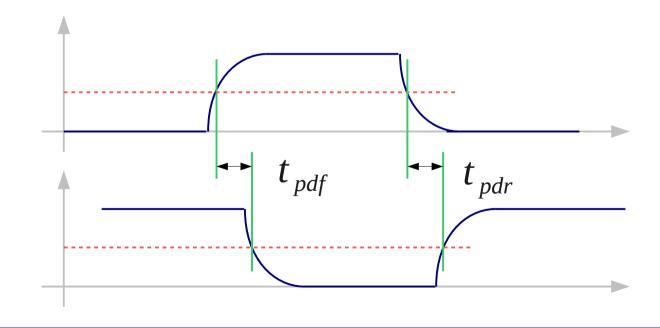

# Rising and Falling Time (1)

### Rising and Falling Time (2)

$$\frac{\beta_n}{\beta_p} = 1.0$$

$$R_n = R_p$$

$$\frac{\beta_n}{\beta_p} = 2.0$$

$$R_n < R_p$$

#### **Rise Time**

$$t_r = R_p C_L$$

#### **Fall Time**

$$t_f = R_n C_L$$

# **Propagation Delay**

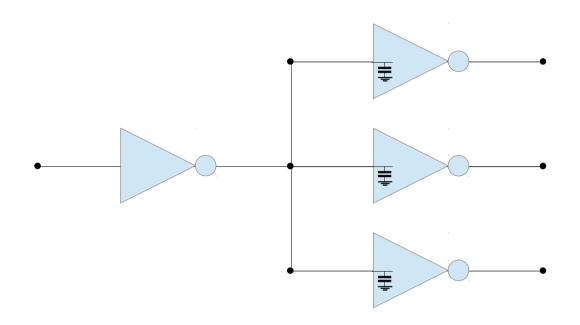

# **Load Capacitance**

$$C_{in} = 3C_g$$

#### Big Capacitance

- A signal connected off-chip

- A signal with very long wire

- A clock signal driving many flip-flops

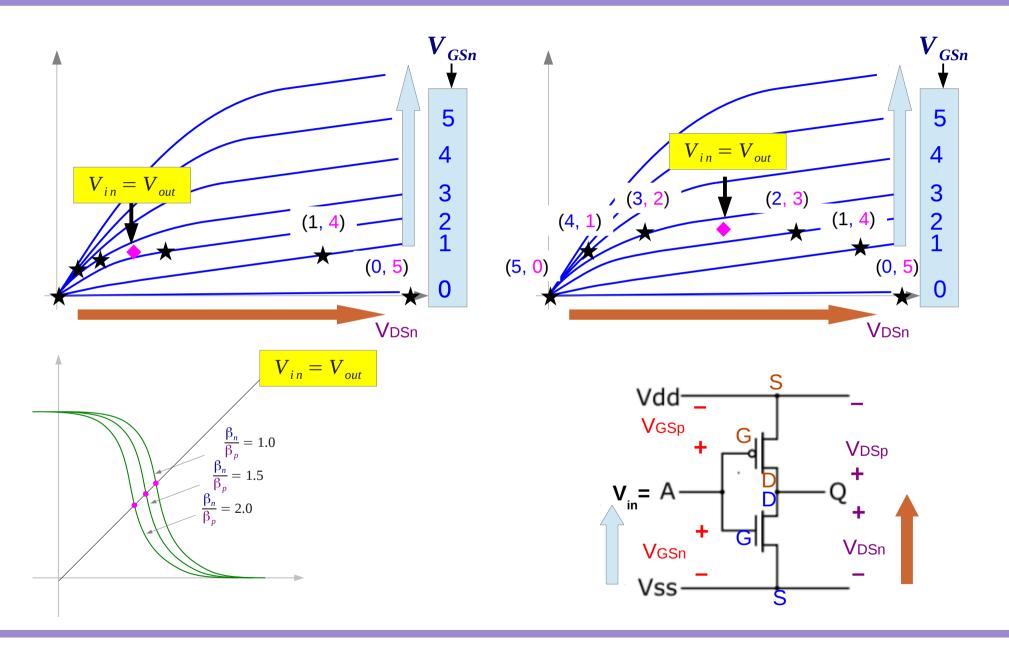

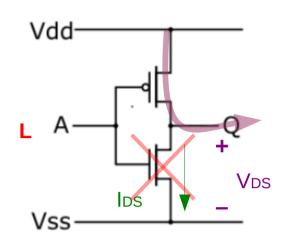

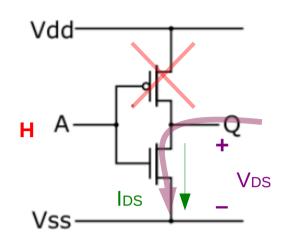

### **Characteristic Curve**

#### References

- [1] http://en.wikipedia.org/

- [2] http://www.allaboutcircuits.com/

- [3] W. Wolf, "Modern VLSI Design: Systems on Silicon

- [4] N. Weste, D. Harris, "CMOS VLSI Design: A Circuits and Systems Perspective"

- [5] J. P. Uyemura, "Introduction to VLSI Circuits and Systems"