**Calhoun: The NPS Institutional Archive**

**DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2018-06

# FIELD PROGRAMMABLE GATE ARRAY HIGH CAPACITY TECHNOLOGY FOR RADAR AND COUNTER-RADAR DRFM SIGNAL PROCESSING

Grubbs, Hawken L.

Monterey, CA; Naval Postgraduate School

http://hdl.handle.net/10945/59670

Downloaded from NPS Archive: Calhoun

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

# NAVAL POSTGRADUATE SCHOOL

MONTEREY, CALIFORNIA

# **THESIS**

FIELD PROGRAMMABLE GATE ARRAY HIGH CAPACITY TECHNOLOGY FOR RADAR AND COUNTER-RADAR DRFM SIGNAL PROCESSING

by

Hawken L. Grubbs

June 2018

Thesis Advisor: Co-Advisor: Phillip E. Pace Steven J. Iatrou

Approved for public release. Distribution is unlimited.

#### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington, DC 20503.

| 1. AGENCY USE ONLY (Leave blank)                                                                                                                   | 2. REPORT DATE June 2018 | 3. REPORT TY                                   | PORT TYPE AND DATES COVERED  Master's thesis           |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------|--------------------------------------------------------|--|

| 4. TITLE AND SUBTITLE FIELD PROGRAMMABLE GAT TECHNOLOGY FOR RADAR A  6. AUTHOR(S) Hawken L. Grub                                                   | ND COUNTER-RADAR DRF     | M SIGNAL                                       | 5. FUNDING NUMBERS                                     |  |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) CENTER FOR JOINT SERVICES ELECTRONIC WARFARE Naval Postgraduate School, Monterey, CA 93943-5000 |                          | 8. PERFORMING<br>ORGANIZATION REPORT<br>NUMBER |                                                        |  |

| 9. SPONSORING / MONITORI<br>ADDRESS(ES)<br>CRUSER, Monterey, CA 93943                                                                              |                          |                                                | 10. SPONSORING /<br>MONITORING AGENCY<br>REPORT NUMBER |  |

11. SUPPLEMENTARY NOTES The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government.

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT              |

|---------------------------------------------------------|

| Approved for public release. Distribution is unlimited. |

12b. DISTRIBUTION CODE

Α

#### 13. ABSTRACT (maximum 200 words)

Radar systems often use low power, continuous waveform radio frequency (RF) modulations and require high-speed adaptive signal processors to provide the necessary processing gain to detect small radar cross-section targets in clutter on range-Doppler maps. Counter-radar technologies include digital RF memories (DRFMs) that attempt to provide multiple, structured false targets with clutter, for example, using a pipelined, finite impulse response arrangement of complex range bin processors. This thesis investigates high-capacity field-programmable gate array (FPGA) technology to enable on-the-fly flexibility and reconfigurability for both radar signal processing and DRFM electronic attack using a Xilinx Virtex Ultrascale+. A three-stage range, Doppler, post-detection integration radar modulation compression circuit is designed and quantified. A range compression circuit with a peak power consumption of 6.100W and a post-implementation utilization of 11% was designed. The Doppler filter bank was designed at 400 MHz with a peak power consumption of 2.688W and a post-implementation utilization of 9%. A coherent integration processor at 400 MHz had a peak power consumption of 2.517W and a post-implementation utilization of 9%. In addition, a DRFM complex range bin processor was designed and quantified at 500 MHz and had a peak power 2.543W with a post-implementation utilization of 11%.

| 14. SUBJECT TERMS LPI radar, low probability of intercept radar, FPGA, field programmable gate array, Virtex Ultrascale+, Vivado, Simulink, DSP, digital signal processing, DRFM, Xilinx  15. NUMBER OF PAGES 149 |                                                |                                               |                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------|-------------------------------|

|                                                                                                                                                                                                                   |                                                |                                               | 16. PRICE CODE                |

| 17. SECURITY<br>CLASSIFICATION OF<br>REPORT                                                                                                                                                                       | 18. SECURITY<br>CLASSIFICATION OF THIS<br>PAGE | 19. SECURITY<br>CLASSIFICATION OF<br>ABSTRACT | 20. LIMITATION OF<br>ABSTRACT |

| Unclassified                                                                                                                                                                                                      | Unclassified                                   | Unclassified                                  | UU                            |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

#### Approved for public release. Distribution is unlimited.

# FIELD PROGRAMMABLE GATE ARRAY HIGH CAPACITY TECHNOLOGY FOR RADAR AND COUNTER-RADAR DRFM SIGNAL PROCESSING

Hawken L. Grubbs Captain, United States Marine Corps BS, University of Oklahoma, 2008

Submitted in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE IN INFORMATION WARFARE SYSTEMS ENGINEERING

from the

## NAVAL POSTGRADUATE SCHOOL June 2018

Approved by: Phillip E. Pace Advisor

Steven J. Iatrou Co-Advisor

Dan C. Boger

Chair, Department of Information Sciences

#### **ABSTRACT**

Radar systems often use low power, continuous waveform radio frequency (RF) modulations and require high-speed adaptive signal processors to provide the necessary processing gain to detect small radar cross-section targets in clutter on range-Doppler maps. Counter-radar technologies include digital RF memories (DRFMs) that attempt to provide multiple, structured false targets with clutter, for example, using a pipelined, finite impulse response arrangement of complex range bin processors. This thesis investigates high-capacity field-programmable gate array (FPGA) technology to enable on-the-fly flexibility and reconfigurability for both radar signal processing and DRFM electronic attack using a Xilinx Virtex Ultrascale+. A three-stage range, Doppler, post-detection integration radar modulation compression circuit is designed and quantified. A range compression circuit with a peak power consumption of 6.100W and a post-implementation utilization of 11% was designed. The Doppler filter bank was designed at 400 MHz with a peak power consumption of 2.688W and a post-implementation utilization of 9%. A coherent integration processor at 400 MHz had a peak power consumption of 2.517W and a post-implementation utilization of 9%. In addition, a DRFM complex range bin processor was designed and quantified at 500 MHz and had a peak power 2.543W with a post-implementation utilization of 11%.

# TABLE OF CONTENTS

| I.    | INT  | RODUCTION                                        | 1       |

|-------|------|--------------------------------------------------|---------|

|       | A.   | RADAR SYSTEMS AND COUNTER-RADAR DIGITAL RF       |         |

|       |      | MEMORIES: THE NEED FOR HIGH CAPACITY             |         |

|       |      | EMBEDDED PROCESSORS                              | 1       |

|       | В.   | PRINCIPAL CONTRIBUTIONS                          | 3       |

|       | C.   | THESIS OUTLINE                                   | 4       |

| II.   | LOV  | W PROBABILITY OF INTERCEPT RADAR                 | 7       |

|       | A.   | REQUIREMENTS                                     | 7       |

|       | В.   | GENERATING LPI WAVEFORMS                         | 8       |

|       |      | 1. Polyphase Modulation (Polyphase Shift Keying) | 9       |

|       |      | 2. Robust Symmetrical Number System (RSNS)       |         |

|       | C.   | RSNS-P4 THREE-STAGE COMPRESSION                  |         |

|       |      | 1. Range Compression                             |         |

|       |      | 2. Doppler Filtering                             |         |

|       |      | 3. Integration                                   |         |

|       | D.   | CHAPTER SUMMARY                                  |         |

| III.  | DRI  | FM                                               | 17      |

| 111.  | A.   | DRFM ARCHITECTURE                                |         |

|       | В.   | NEED FOR AUGMENTATION IN ELECTRONIC ATTACK       | ••••••1 |

|       | Д,   | SYSTEMSSYSTEMS                                   | 19      |

|       | C.   | CHAPTER SUMMARY                                  |         |

| IV.   | ומומ | LD PROGRAMMABLE GATE ARRAY                       | 23      |

| 1 V . | A.   | OVERVIEW OF THE FPGA                             |         |

|       | Α.   |                                                  |         |

|       |      | ·                                                |         |

|       | n    | 2. Current Uses                                  |         |

|       | В.   | DIGITAL SIGNAL PROCESSING ON A FPGA              |         |

|       |      | 1. Introduction to DSP                           |         |

|       |      | 2. Introduction to DSP for FPGAs                 |         |

|       | ~    | 3. DSP-FPGA Design Fundamentals                  |         |

|       | С.   | XILINX VIRTEX ULTRASCALE+                        |         |

|       |      | 1. Overview                                      |         |

|       |      | 2. Hardware                                      |         |

|       | D.   | SIMULATION PROCESS                               |         |

|       | Е.   | CHAPTER SUMMARY                                  | 52      |

| V.   | MOl       | DELING, SYNTHESIS, AND IMPLEMENTATION RESULTS | 53  |

|------|-----------|-----------------------------------------------|-----|

|      | A.        | DIGITAL RADIO FREQUENCY MEMORY (DRFM)         | 55  |

|      |           | 1. Model                                      | 55  |

|      |           | 2. Synthesis / Implementation                 | 59  |

|      | В.        | RANGE COMPRESSION                             | 64  |

|      |           | 1. Model                                      | 64  |

|      |           | 2. Synthesis / Implementation                 | 66  |

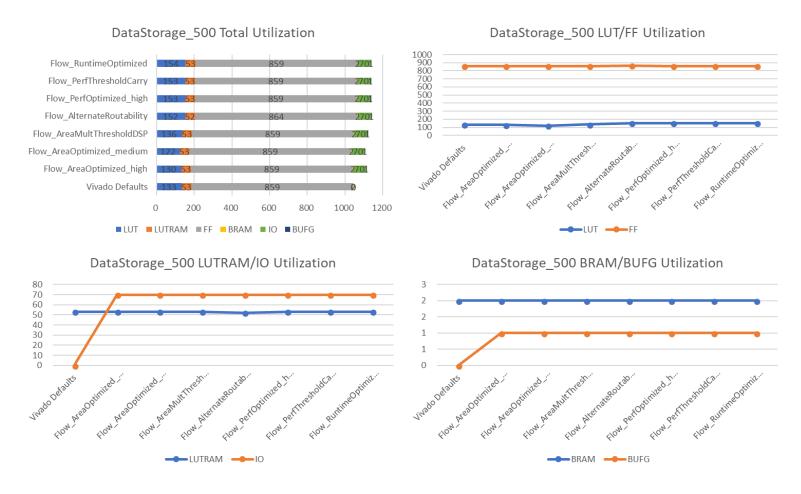

|      | C.        | DATA STORAGE                                  | 71  |

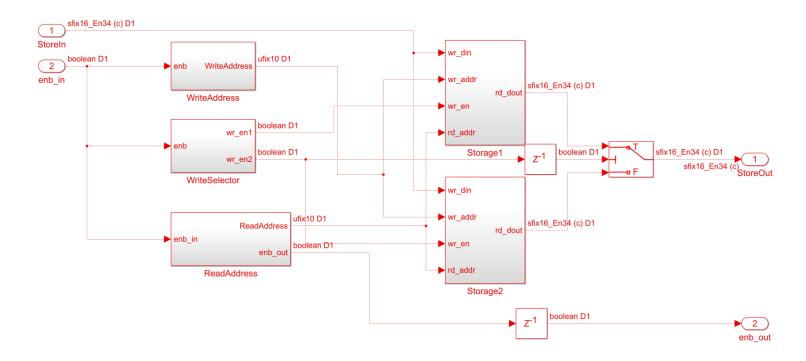

|      |           | 1. Model                                      | 71  |

|      |           | 2. Synthesis / Implementation                 | 73  |

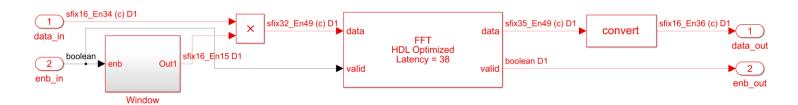

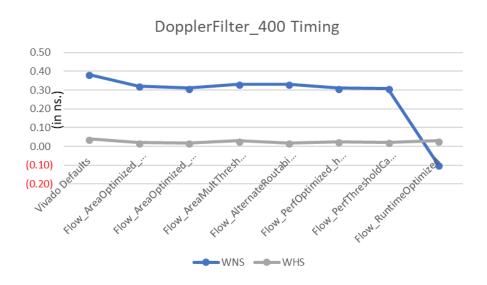

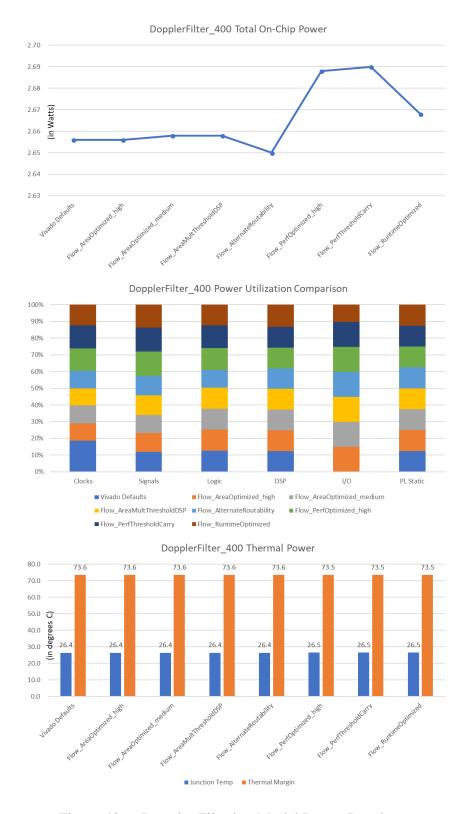

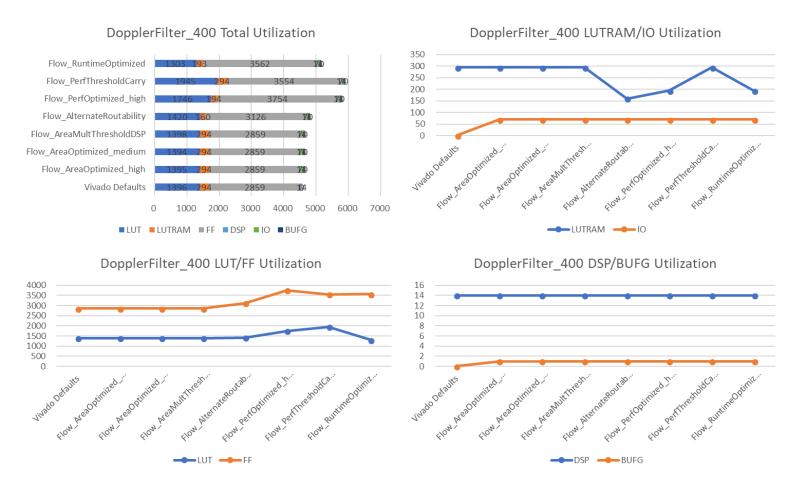

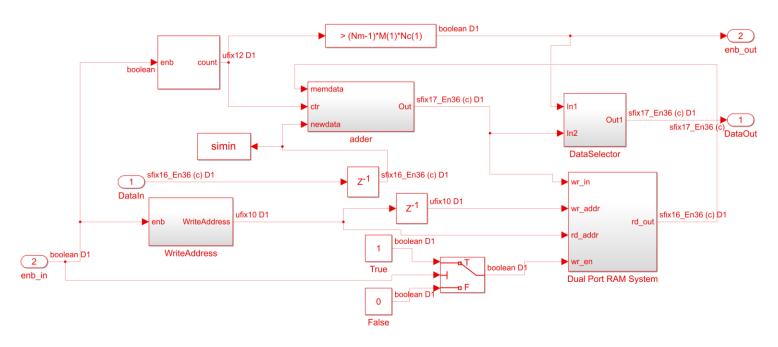

|      | D.        | DOPPLER FILTERING                             | 77  |

|      |           | 1. Model                                      | 77  |

|      |           | 2. Synthesis / Implementation                 | 79  |

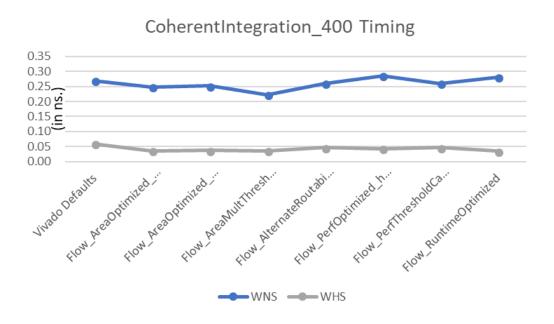

|      | <b>E.</b> | COHERENT INTEGRATION                          | 84  |

|      |           | 1. Model                                      | 84  |

|      |           | 2. Synthesis / Implementation                 | 86  |

|      | F.        | THREE-STAGE COMPRESSION                       | 91  |

|      |           | 1. Model                                      | 91  |

|      |           | 2. Synthesis / Implementation                 | 93  |

|      | G.        | CHAPTER SUMMARY                               | 98  |

| VI.  | CON       | NCLUSION AND RECOMMENDATIONS                  | 99  |

| APP  | ENDIX     | X. VIVADO DATA CAPTURES                       | 101 |

|      | A.        | DRFM MODEL DATA                               | 101 |

|      | В.        | RANGE COMPRESSION MODEL DATA                  | 104 |

|      | C.        | DATA STORAGE MODEL DATA                       | 108 |

|      | D.        | DOPPLER FILTERING MODEL DATA                  | 112 |

|      | <b>E.</b> | COHERENT INTEGRATION MODEL DATA               | 116 |

|      | F.        | THREE-STAGE COMPRESSION MODEL DATA            | 120 |

| LIST | OF R      | EFERENCES                                     | 125 |

| INIT | TAL D     | ISTRIBUTION LIST                              | 127 |

# LIST OF FIGURES

| Figure 1.  | Multifunction Sensor System. Source: [2]                                                                                                               | .3         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

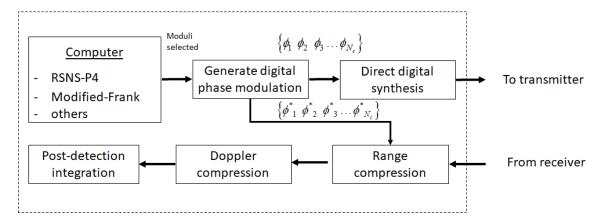

| Figure 2.  | LPI Waveform Generation and Compression.                                                                                                               | .9         |

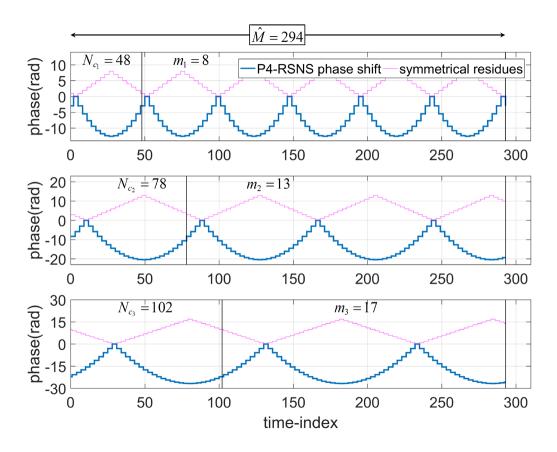

| Figure 3.  | "P4-RSNS Channels and Symmetrical Residues." Source: [1]                                                                                               | 1          |

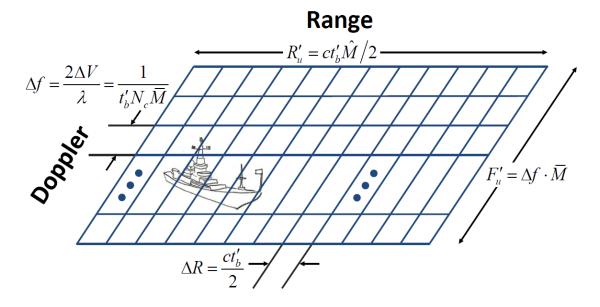

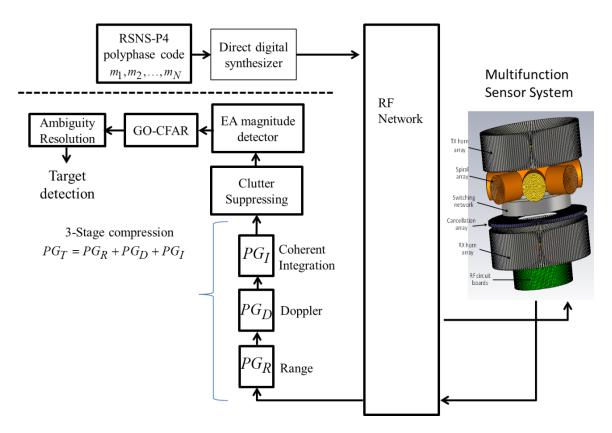

| Figure 4.  | "RSNS-P4 CW Radar - Block Diagram Indicating the Processing Gain Steps." Source: [1].                                                                  | 12         |

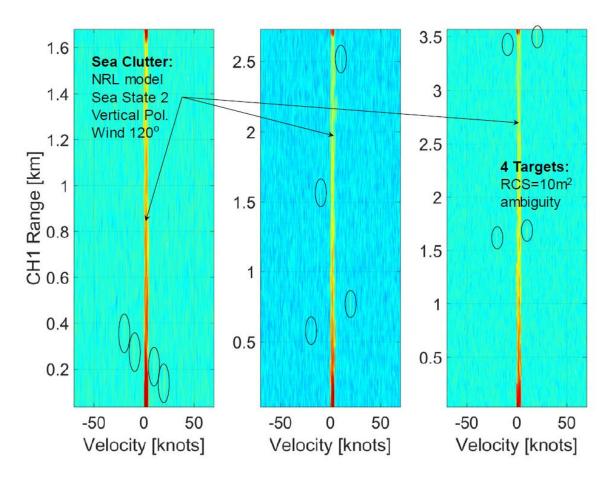

| Figure 5.  | "RSNS-P4 CW Radar - Range-Doppler Detection Map." Source: [1]1                                                                                         | 3          |

| Figure 6.  | "Range-Velocity Maps for Each of the Three Channels. Target Moves at Relative Speeds Sufficiently Different from the Sea Clutter Spectra." Source: [1] | 15         |

| Figure 7.  | LPI Signaling Environment and Integration with the Multifunction Sensor System                                                                         | 6          |

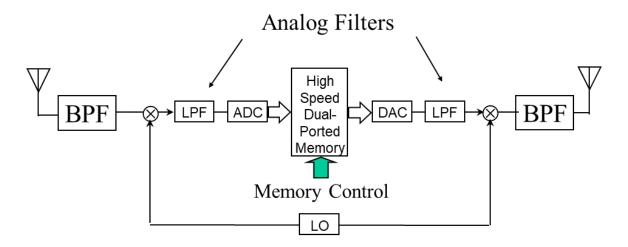

| Figure 8.  | Block Diagram of a Single Sideband DRFM. Source: [5]                                                                                                   | 8          |

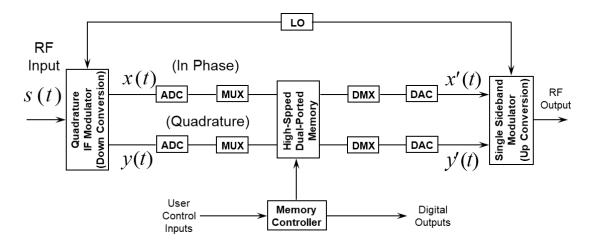

| Figure 9.  | Block Diagram of a Double Sideband DRFM. Source: [5]                                                                                                   | 9          |

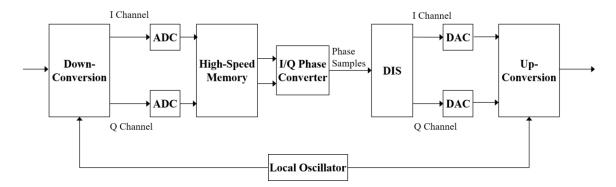

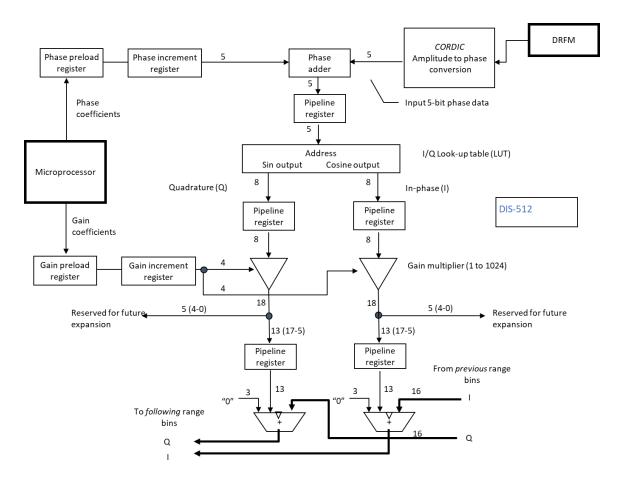

| Figure 10. | Simplified Block Diagram of the DRFM Integrated with the I/Q Phase Converter and DIS. Source: [7].                                                     | 20         |

| Figure 11. | "A Xilinx Zynq-7000 All Programmable System on a Chip." Source: [19]                                                                                   | 27         |

| Figure 12. | Model-Design Environment that Provides an Integrated Workflow for Faster Waveform Engineering.                                                         | 34         |

| Figure 13. | Virtex UltraScale+ VCU 118 Evaluation Board. Source: [21]                                                                                              | 13         |

| Figure 14. | MATLAB / Vivado Sync Command                                                                                                                           | <b>!</b> 7 |

| Figure 15. | Successful MATLAB / Vivado Sync Return                                                                                                                 | <b>!</b> 7 |

| Figure 16. | HDL Workflow Advisor Selection.                                                                                                                        | <b>1</b> 7 |

| Figure 17. | System Selector Pop-up.                                                                                                                                | 18         |

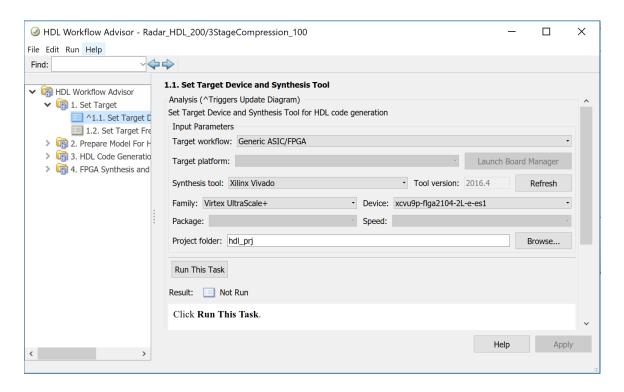

| Figure 18. | Section 1.1: Set Target Device and Synthesis Tool Window                                                                                               | 18         |

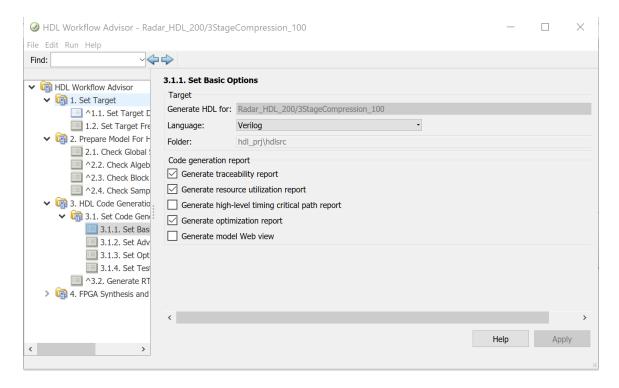

| Figure 19. | Section 3.1.1: Set Basic Options Window                                                                                                                | 19         |

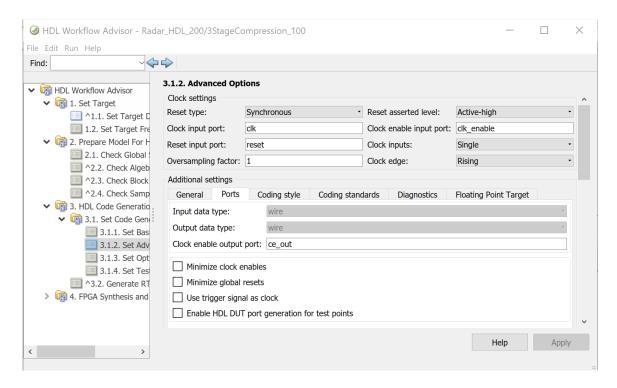

| Figure 20. | Section 3.1.2: Advanced Options Window               | 50 |

|------------|------------------------------------------------------|----|

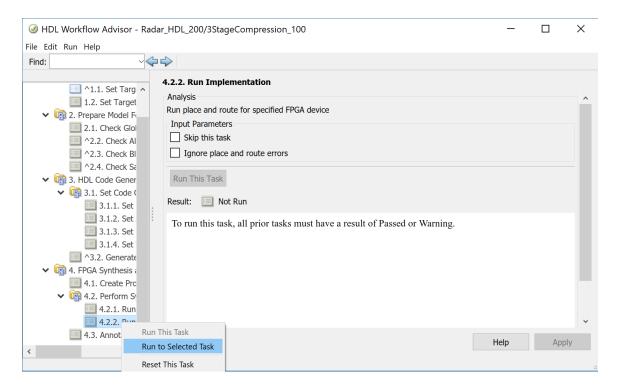

| Figure 21. | Section 4.2.2: Run Implementation Window             | 51 |

| Figure 22. | Create Runs button                                   | 52 |

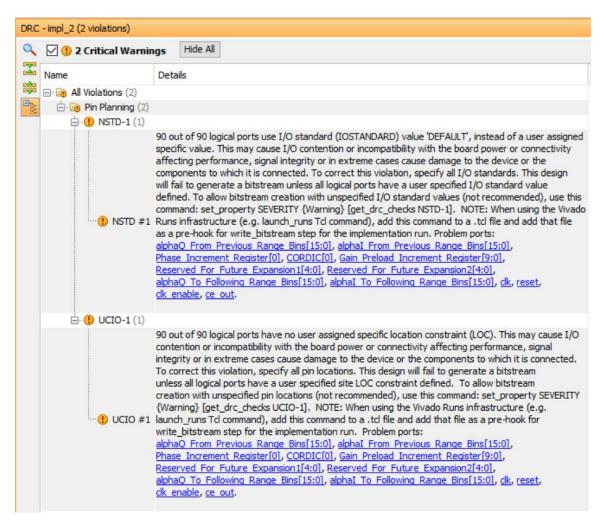

| Figure 23. | Implementation Critical Warnings.                    | 54 |

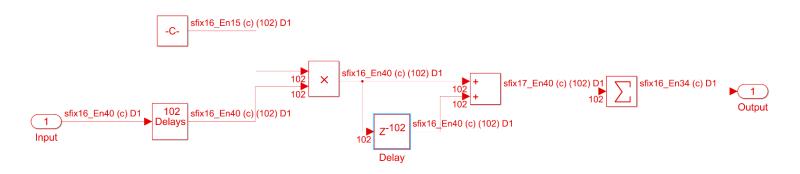

| Figure 24. | DIS-512 DRFM Block Diagram.                          | 57 |

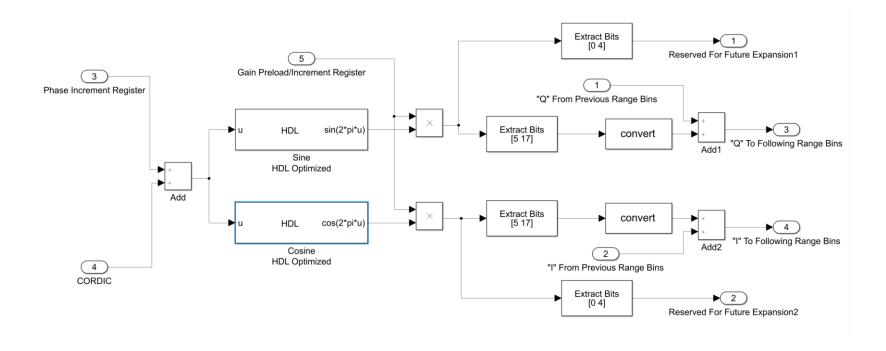

| Figure 25. | DIS-512 DRFM Block Diagram Built in Simulink.        | 58 |

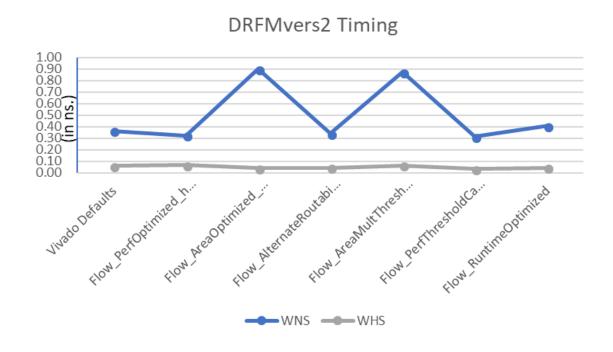

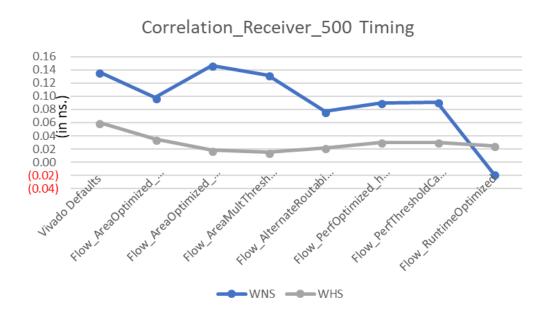

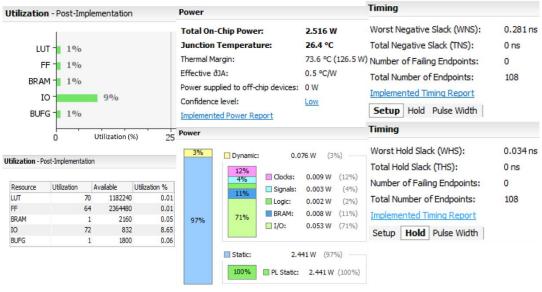

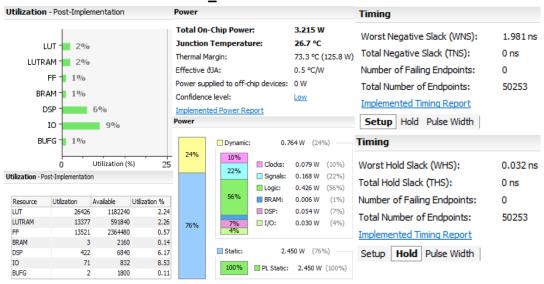

| Figure 26. | DRFM Model Timing Results.                           | 59 |

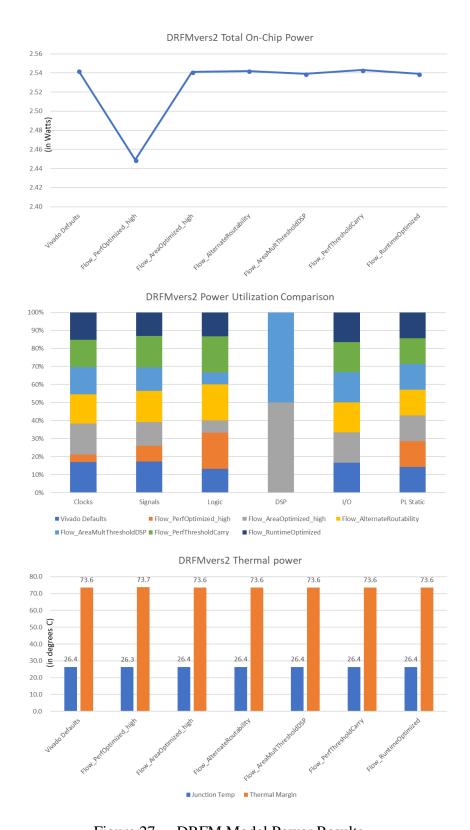

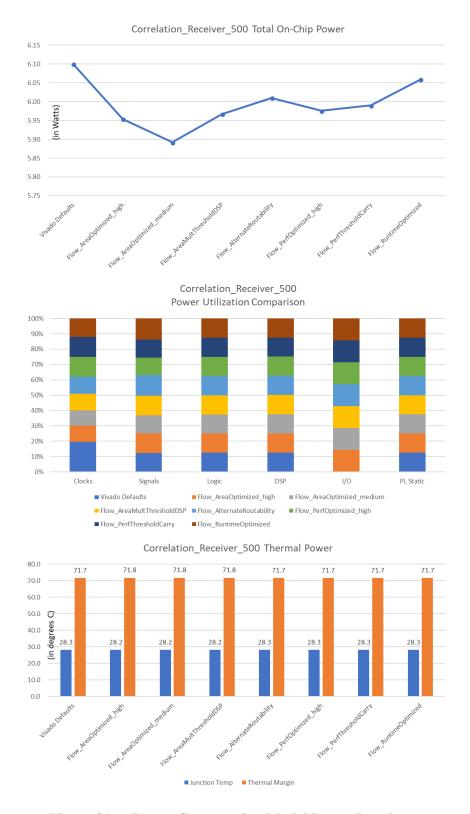

| Figure 27. | DRFM Model Power Results.                            | 61 |

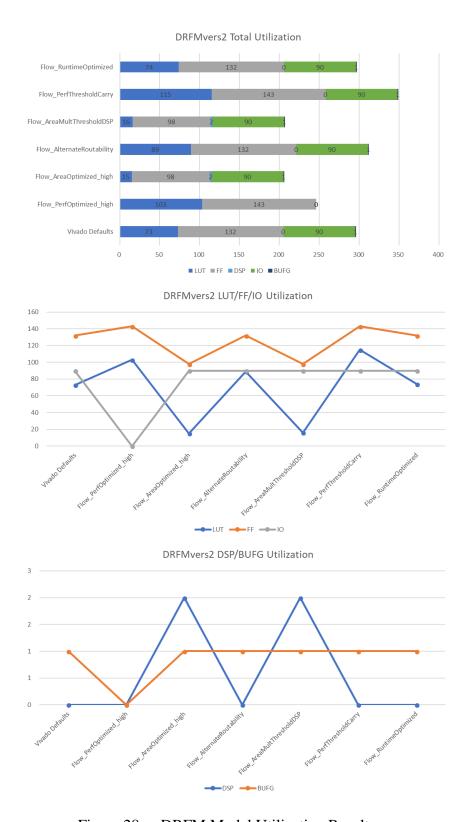

| Figure 28. | DRFM Model Utilization Results.                      | 63 |

| Figure 29. | Range Compression Block Diagram Built in Simulink    | 65 |

| Figure 30. | Range Compression Model Timing Results.              | 66 |

| Figure 31. | Range Compression Model Power Results                | 67 |

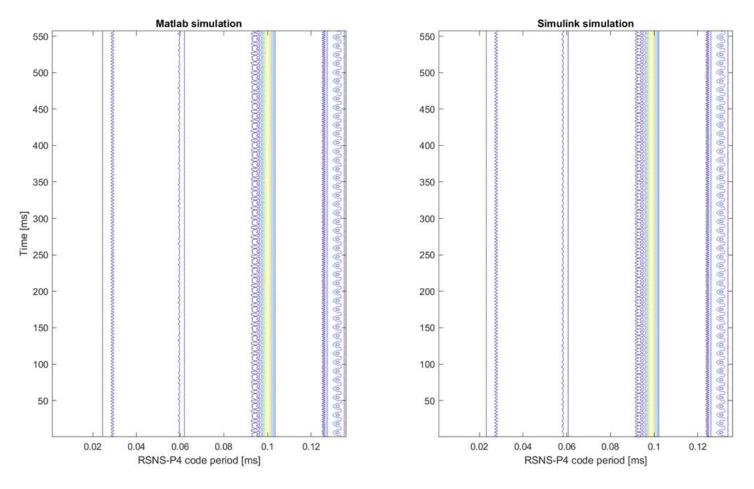

| Figure 32. | Range Compression Model MATLAB and Simulink Results  | 69 |

| Figure 33. | Range Compression Model MATLAB and Simulink Results  | 70 |

| Figure 34. | Data Storage Block Diagram Built in Simulink.        | 72 |

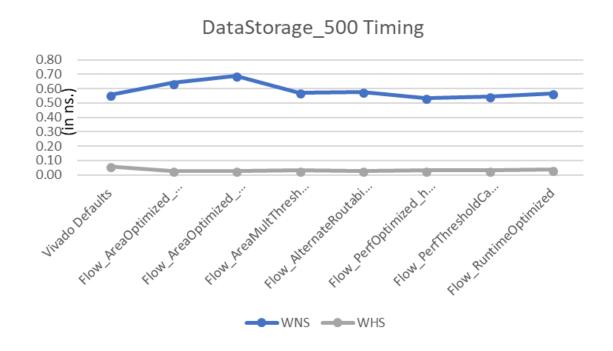

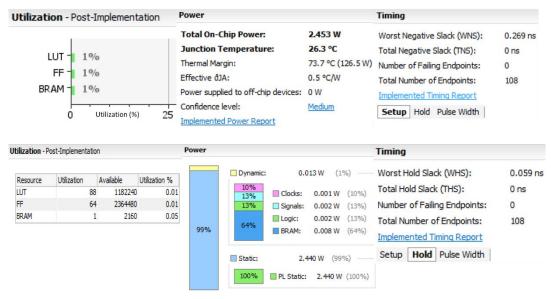

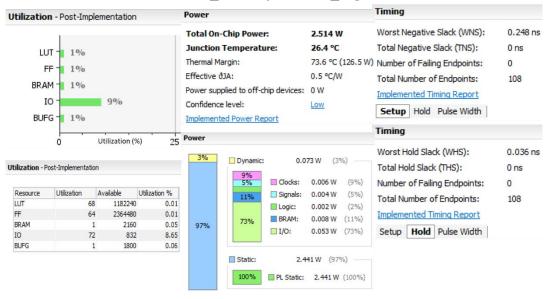

| Figure 35. | Data Storage Model Timing Results                    | 73 |

| Figure 36. | Data Storage Model Power Results.                    | 74 |

| Figure 37. | Data Storage Model Utilization Results.              | 76 |

| Figure 38. | Doppler Filtering Block Diagram Built in Simulink.   | 78 |

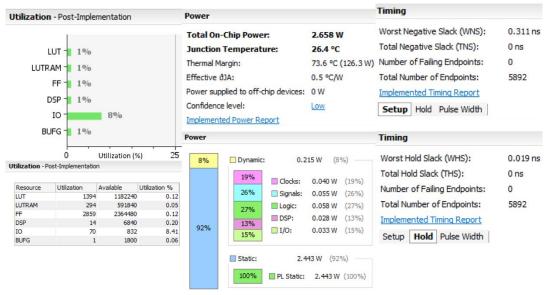

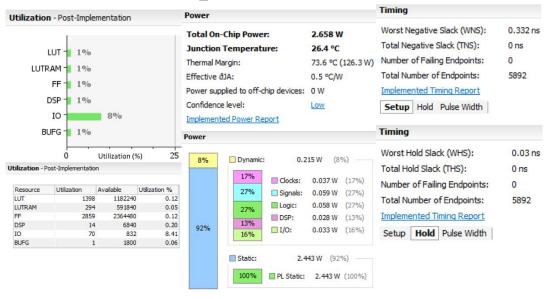

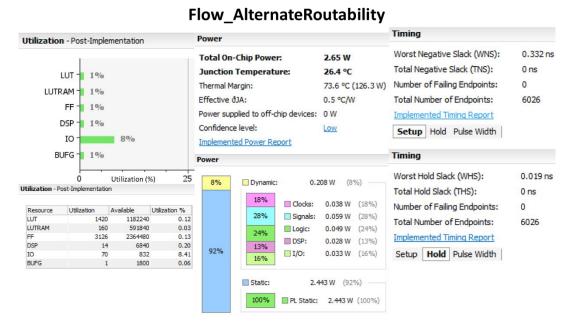

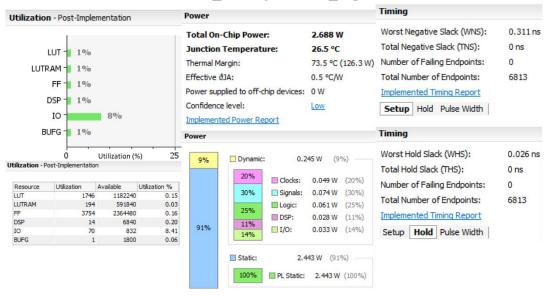

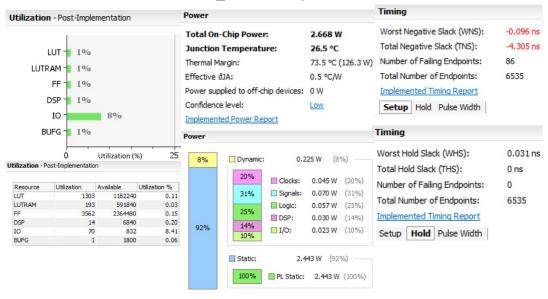

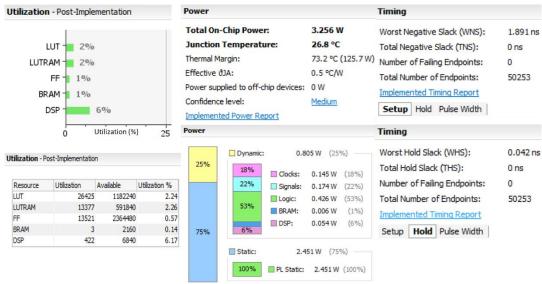

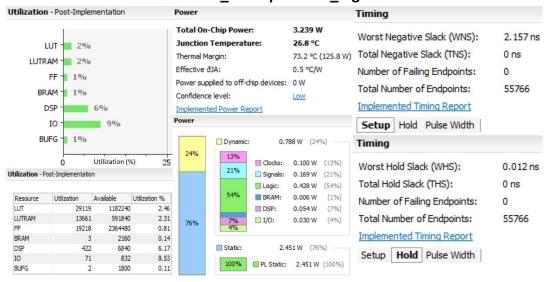

| Figure 39. | Doppler Filtering Model Timing Results               | 79 |

| Figure 40. | Doppler Filtering Model Power Results.               | 80 |

| Figure 41. | Doppler Filtering Model Utilization Results.         | 82 |

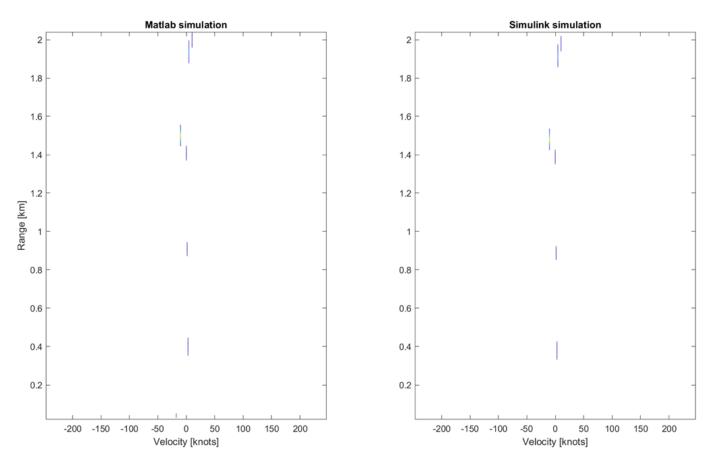

| Figure 42. | Doppler Filtering Model MATLAB and Simulink Results  | 83 |

| Figure 43. | Coherent Integration Block Diagram Built in Simulink | 85 |

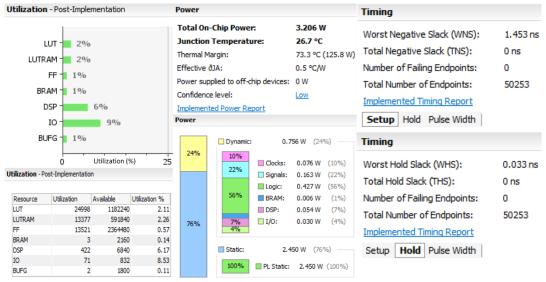

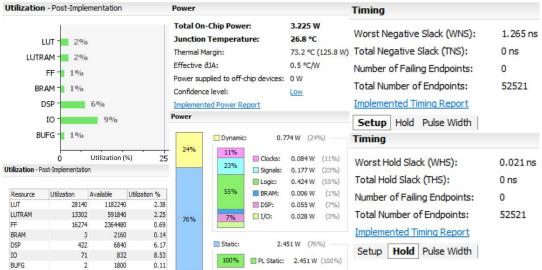

| Figure 44. | Coherent Integration Model Timing Results.           | 86 |

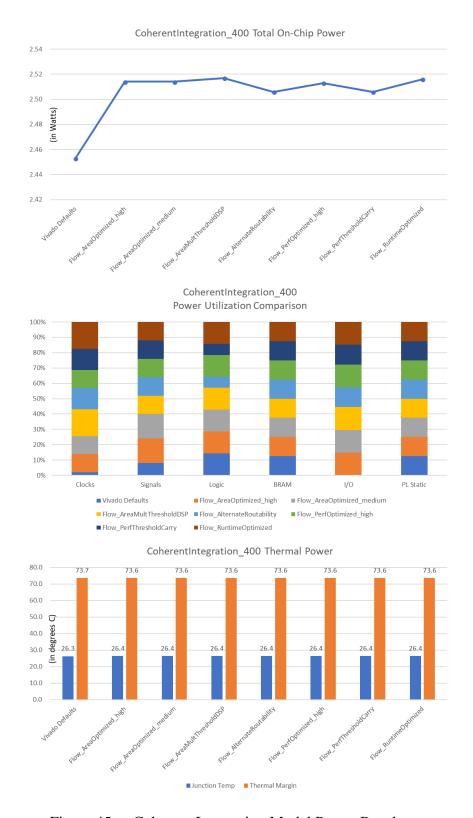

| Figure 45. | Coherent Integration Model Power Results.                                                | 87  |

|------------|------------------------------------------------------------------------------------------|-----|

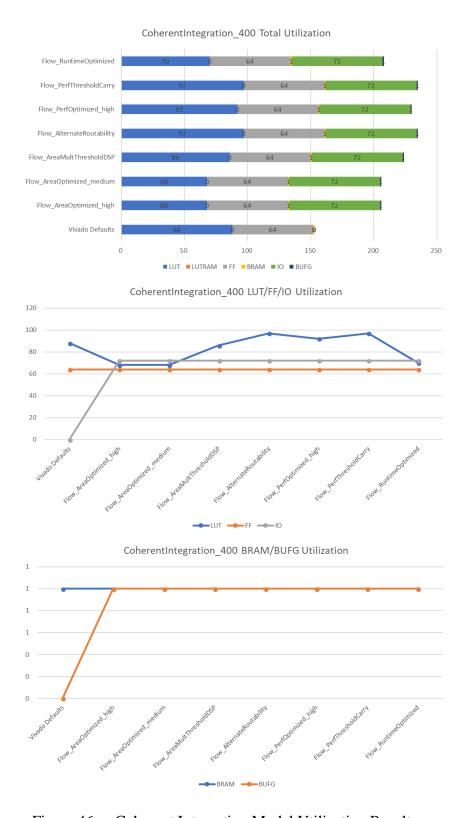

| Figure 46. | Coherent Integration Model Utilization Results.                                          | 89  |

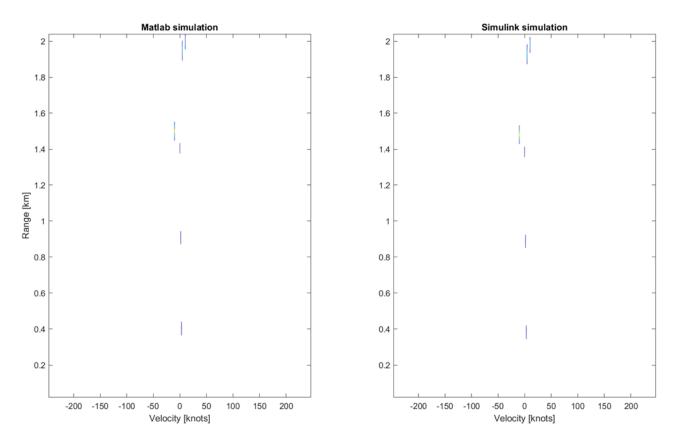

| Figure 47. | Coherent Integration Model MATLAB and Simulink Results                                   | 90  |

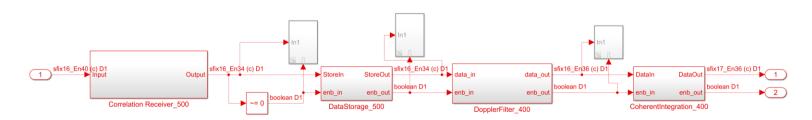

| Figure 48. | Top Level Block Diagram of Three-stage Compression Built in Simulink.                    | 92  |

| Figure 49. | Three-stage Compression Block Diagram Built in Simulink                                  | 92  |

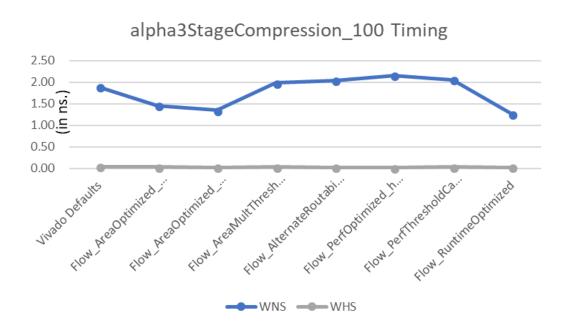

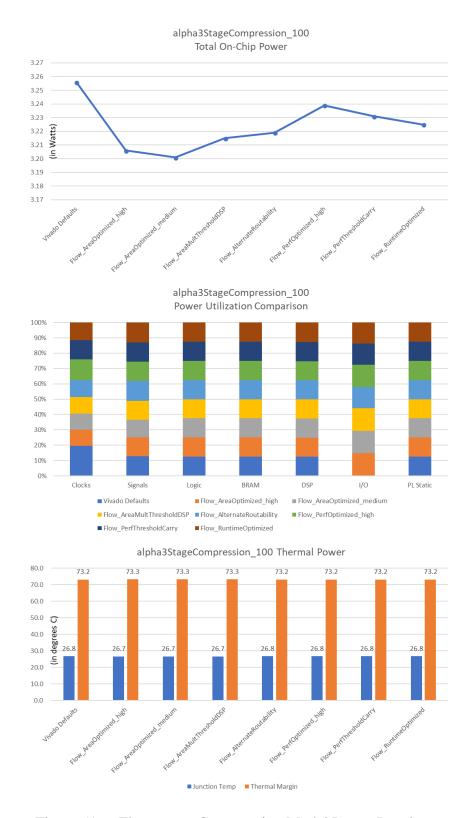

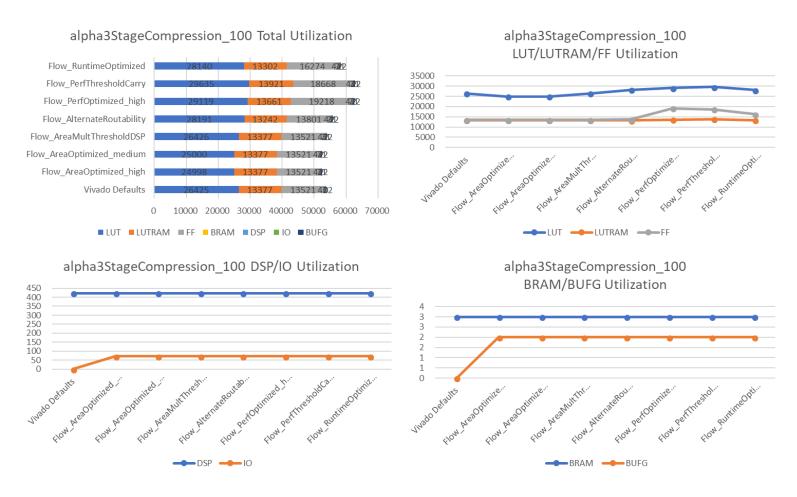

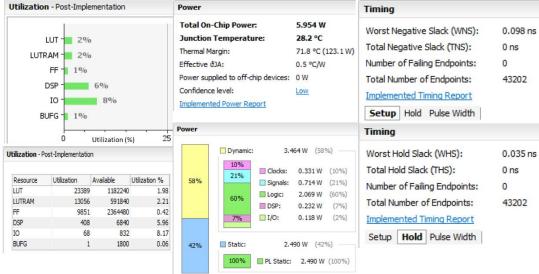

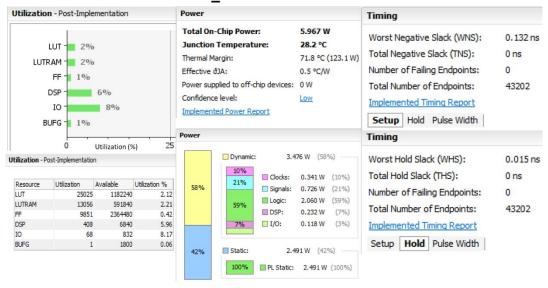

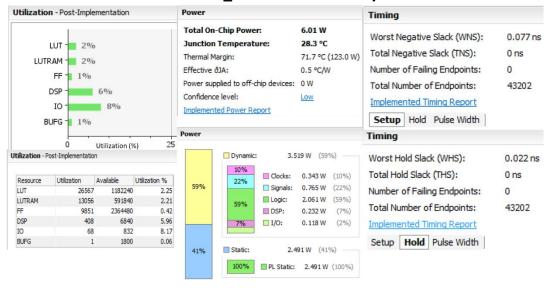

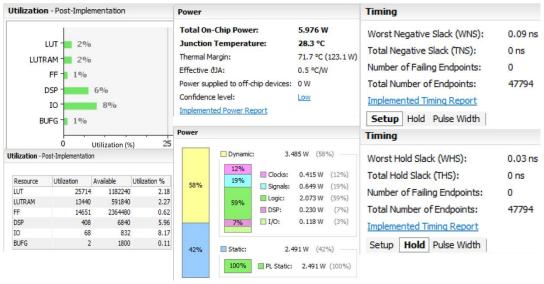

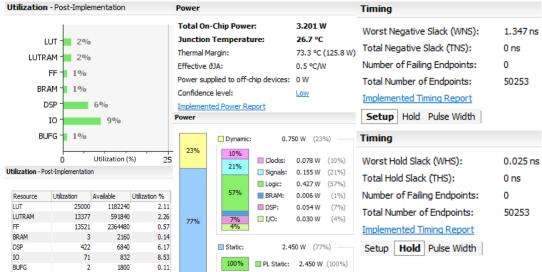

| Figure 50. | Three-stage Compression Model Timing Results                                             | 93  |

| Figure 51. | Three-stage Compression Model Power Results.                                             | 94  |

| Figure 52. | Three-stage Compression Model Utilization Results.                                       | 96  |

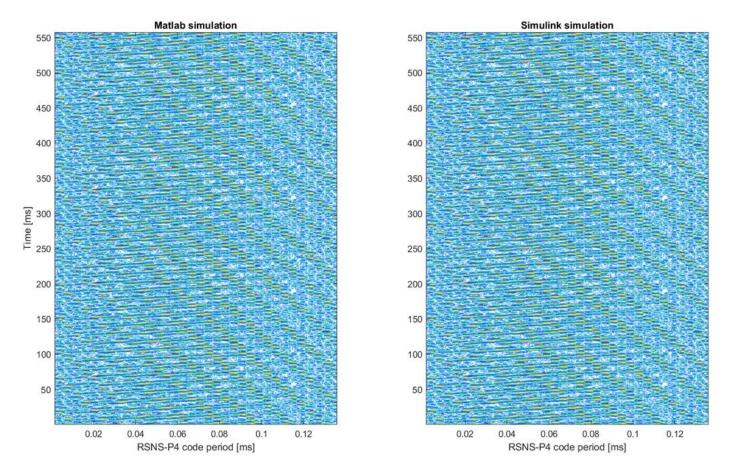

| Figure 53. | Input RSNS-P4 Test Signal through the MATLAB and Simulink Three-Stage Compression Model. | 97  |

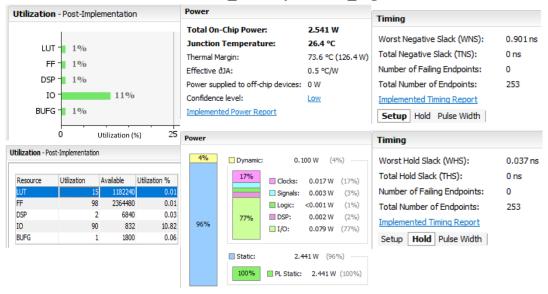

| Figure 54. | Vivado Default Results for DRFM Model                                                    | 101 |

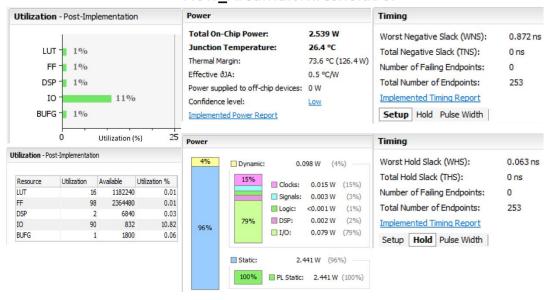

| Figure 55. | Vivado Flow_PerfOptimized_high Results for DRFM Model                                    | 101 |

| Figure 56. | Vivado Flow_AreaOptimized_high Results for DRFM Model                                    | 102 |

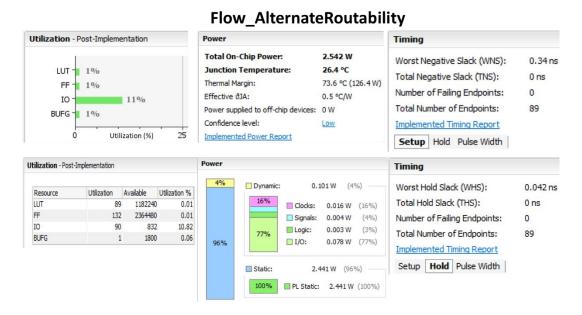

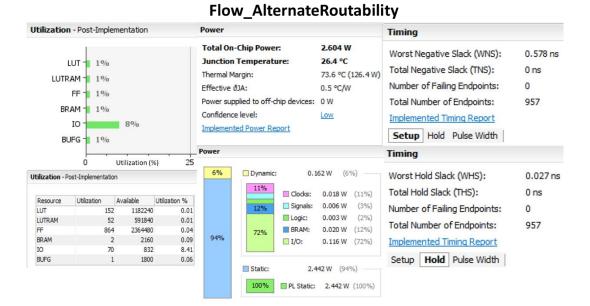

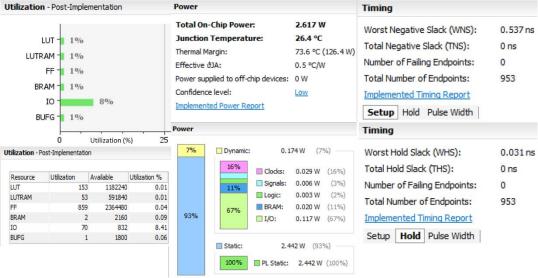

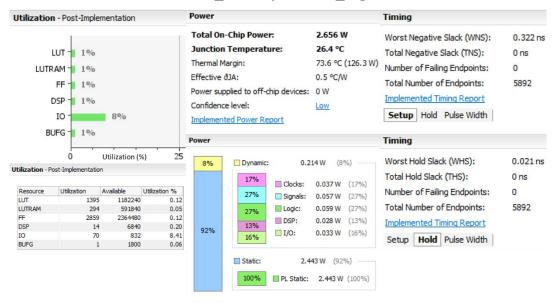

| Figure 57. | Vivado Flow_AlternateRoutability Results for DRFM Model                                  | 102 |

| Figure 58. | Vivado Flow_AreaMultThresholdDSP Results for DRFM Model                                  | 103 |

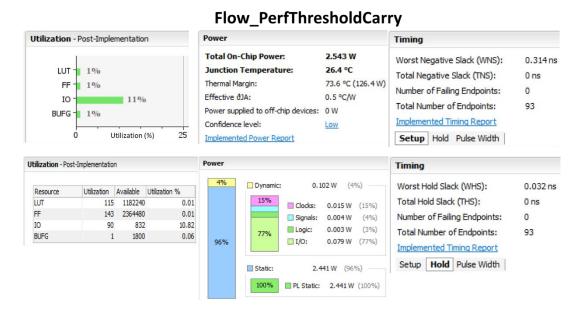

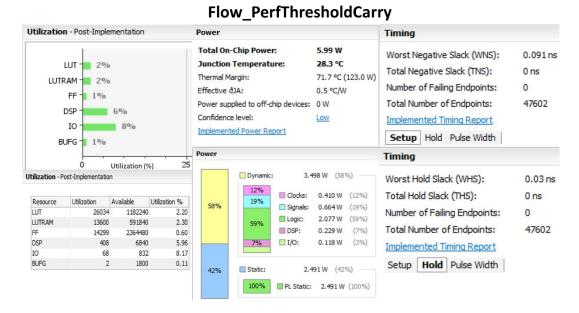

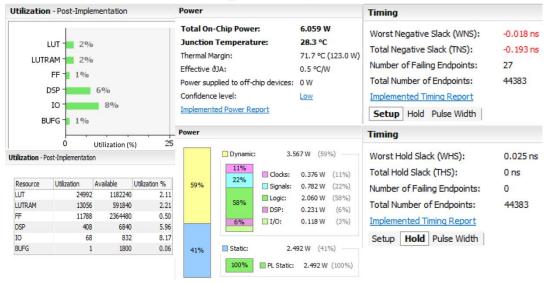

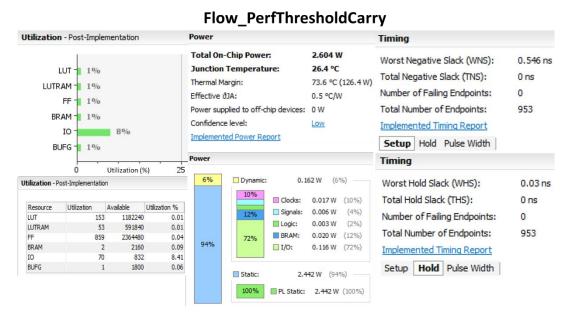

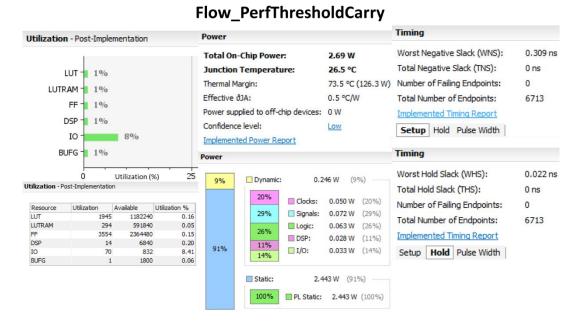

| Figure 59. | Vivado Flow_PerfThresholdCarry Results for DRFM Model                                    | 103 |

| Figure 60. | Vivado Flow_RuntimeOptimized Results for DRFM Model                                      | 104 |

| Figure 61. | Vivado Default Results for Range Compression Model                                       | 104 |

| Figure 62. | Vivado Flow_AreaOptimized_high Results for Range Compression Model.                      | 105 |

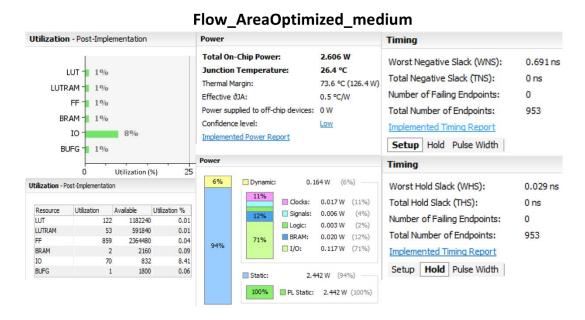

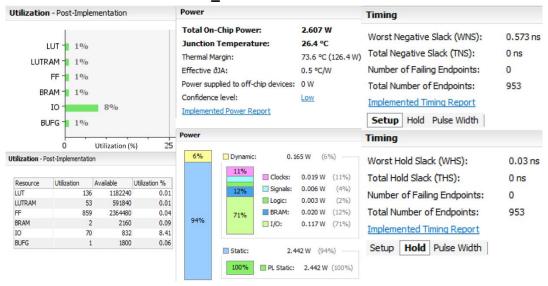

| Figure 63. | Vivado Flow_AreaOptimized_medium Results for Range<br>Compression Model                  | 105 |

| Figure 64. | Vivado Flow_AreaMultThresholdDSP Results for Range<br>Compression Model                  | 106 |

| Figure 65. | Vivado Flow_AlternateRoutability Results for Range Compression Model.                    | 106 |

| Figure 66. | Vivado Flow_PerfOptimized_high Results for Range Compression  Model107  |

|------------|-------------------------------------------------------------------------|

| Figure 67. | Vivado Flow_PerfThresholdCarry Results for Range Compression  Model     |

| Figure 68. | Vivado Flow_RuntimeOptimized Results for Range Compression Model        |

| Figure 69. | Vivado Default Results for Data Storage Model                           |

| Figure 70. | Vivado Flow_AreaOptimized_high Results for Data Storage Model109        |

| Figure 71. | Vivado Flow_AreaOptimized_medium Results for Data Storage Model         |

| Figure 72. | Vivado Flow_AreaMultThresholdDSP Results for Data Storage Model110      |

| Figure 73. | Vivado Flow_AlternateRoutability Results for Data Storage Model110      |

| Figure 74. | Vivado Flow_PerfOptimized_high Results for Data Storage Model111        |

| Figure 75. | Vivado Flow_PerfThresholdCarry Results for Data Storage Model111        |

| Figure 76. | Vivado Flow_RuntimeOptimized Results for Data Storage Model112          |

| Figure 77. | Vivado Default Results for Doppler Filtering Model112                   |

| Figure 78. | Vivado Flow_AreaOptimized_high Results for Doppler Filtering Model113   |

| Figure 79. | Vivado Flow_AreaOptimized_medium Results for Doppler Filtering Model    |

| Figure 80. | Vivado Flow_AreaMultThresholdDSP Results for Doppler Filtering Model    |

| Figure 81. | Vivado Flow_AlternateRoutability Results for Doppler Filtering Model114 |

| Figure 82. | Vivado Flow_PerfOptimized_high Results for Doppler Filtering Model      |

| Figure 83. | Vivado Flow_PerfThresholdCarry Results for Doppler Filtering Model115   |

| Figure 84.  | Vivado Flow_RuntimeOptimized Results for Doppler Filtering Model.              | 116 |

|-------------|--------------------------------------------------------------------------------|-----|

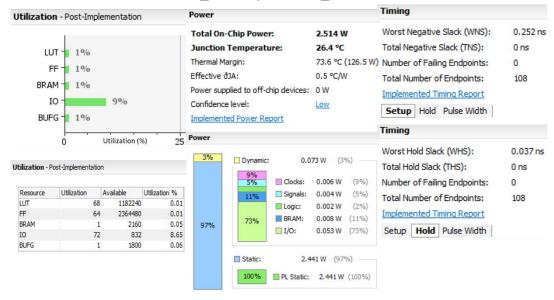

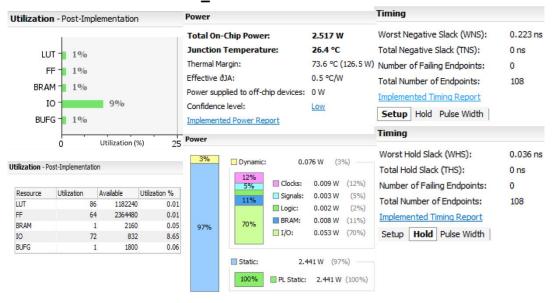

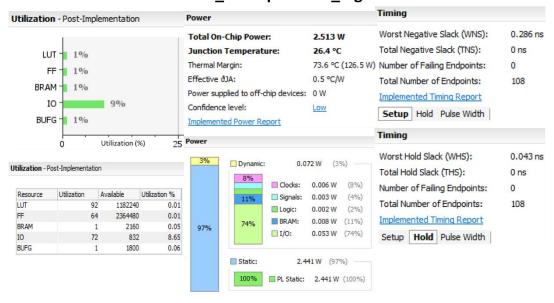

| Figure 85.  | Vivado Default Results for Coherent Integration Model                          | 116 |

| Figure 86.  | Vivado Flow_AreaOptimized_high Results for Coherent Integration Model.         | 117 |

| Figure 87.  | Vivado Flow_AreaOptimized_medium Results for Coherent<br>Integration Model     | 117 |

| Figure 88.  | Vivado Flow_AreaMultThresholdDSP Results for Coherent<br>Integration Model     | 118 |

| Figure 89.  | Vivado Flow_AlternateRoutability Results for Coherent Integration Model.       | 118 |

| Figure 90.  | Vivado Flow_PerfOptimized_high Results for Coherent Integration Model.         | 119 |

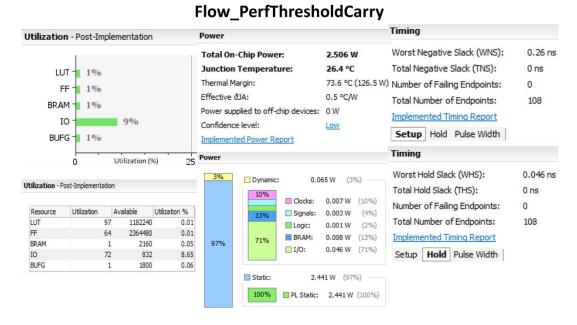

| Figure 91.  | Vivado Flow_PerfThresholdCarry Results for Coherent Integration Model.         | 119 |

| Figure 92.  | Vivado Flow_RuntimeOptimized Results for Coherent Integration Model.           | 120 |

| Figure 93.  | Vivado Default Results for Three-stage Compression Model                       | 120 |

| Figure 94.  | Vivado Flow_AreaOptimized_high Results for Three-stage<br>Compression Model    | 121 |

| Figure 95.  | Vivado Flow_AreaOptimized_medium Results for Three-stage Compression Model     | 121 |

| Figure 96.  | Vivado Flow_AreaMultThresholdDSP Results for Three-stage<br>Compression Model  | 122 |

| Figure 97.  | Vivado Flow_AlternateRoutability Results for Three-stage<br>Compression Model. | 122 |

| Figure 98.  | Vivado Flow_PerfOptimized_high Results for Three-stage<br>Compression Model    | 123 |

| Figure 99.  | Vivado Flow_PerfThresholdCarry Results for Three-stage<br>Compression Model.   | 123 |

| Figure 100. | Vivado Flow_RuntimeOptimized Results for Three-stage Compression Model         | 124 |

## LIST OF TABLES

| Table 1. | Related Technologies to FPGAs. Source: [8]                         | 24  |

|----------|--------------------------------------------------------------------|-----|

| Table 2. | Current FPGA Applications. Adapted from [8]                        | 28  |

| Table 3. | 1990s Multimedia PC Enabled by DSP Technologies. Source: [8]       | 30  |

| Table 4. | DSP Applications. Source: [8]                                      | 32  |

| Table 5. | Virtex UltraScale+ VCU 118 Evaluation Board Features. Source: [21] | 44  |

| Table 6. | Total Resources for Project Part: xcvu9p-plga2104-2L-e-es1         | 44  |

| Table 7. | List of Installed MATLAB/Simulink Toolboxes and Add-ons            | 46  |

| Table 8. | Recommended Training Courses.                                      | 100 |

#### LIST OF ACRONYMS AND ABBREVIATIONS

ADC analog-to-digital converter

ASIC application specific integrated circuit

ASSP application-specific standard parts

BPF band-pass filter

CLB configurable logic block

CMT clock management tiles

CPLD complex programmable logic device

CW continuous wave

DAC digital-to-analog converter

DCM digital clock manager

DDS direct digital synthesis

DIS digital imaging synthesizer

DP data processing

DRFM digital radio frequency memory

DSB double sideband

DSP digital signal processing

EA electronic attack

EW electronic warfare

FF flip-flop

FFT fast Fourier transform

FMCW frequency modulated CW

FPGA field programmable gate array

FSK frequency shift keying

Go-CFAR greatest of (GO) constant false alarm rate (CFAR)

GPP general purpose processor

I in-phase

IF intermediate frequency

IFFT inverse fast Fourier transform

I/O input and output

IOB input/output block

IP internet protocol

ISAR inverse synthetic aperture radar

LO local oscillator

LPF low pass filter

LPI low probability of intercept

LUT lookup table

MAC multiply and accumulate/add MATLAB matrix laboratory software

MIMO minimum input minimum output

PLD programmable logic device

PLL phase locked loop

PROM programmable read-only memory

PSK polyphase shift keying

Q quadrature

RAM random access memory

RF radio frequency

ROM read only memory

RSNS robust symmetrical number system

RSNS-P4 robust symmetrical number system – P4

SNR signal-to-noise ratio

SoC system on a chip

SRL shift register

SSB single sideband

VHDL Verilog hardware description language

WHS worst hold slack

WNS worst negative slack

#### **ACKNOWLEDGMENTS**

I would like to take the time to thank my thesis advisor, Dr. Pace, for his leadership, mentorship, and guidance over the past year. This thesis experience has been an endeavor in which I have personally learned more than I could have ever imagined in this field of expertise. I would also like to thank Max Hainz for the countless hours he spent helping me understand the pre-existing MATLAB simulations and further developing the required Simulink models for this thesis. Without his time and dedication, this thesis would not have been possible. I would like to thank Steve Iatrou for his support as a co-advisor and guiding me through the IWSE curriculum while understanding that with my knowledge learned from NPS, that I could indeed take on such a demanding thesis topic. Additionally, many thanks are also aimed toward CRUSER personnel, who through their generosity and sponsorship, made it possible for me to explore thesis topic ideas and eventually attend the required courses to broaden my knowledge and understanding of the presented material.

I would like to thank my parents, Kenneth Brad and Rae Nita Grubbs, for instilling in me the absolute importance of an education as a young child and to never forget who I am and where I come from. Furthermore, I would like to thank my children, Colt, Levi, Chloe, Cheyenne, and Conner, for always being the light in my life. Each of you continually make me proud, especially with how well each of you handled the difficulty of family separation for the past two years. Last but certainly not least, I would like to thank the love of my life, Rachael, for the love and support you have given me over the past thirteen years. Without that love and support, I would certainly not be the man I am today. You are the strongest woman I know for being able to serve as a single mother in my absence while earning your undergraduate degree. You are a shining example for our children; may the future bring many more wonderful memories for us to hold as a family.

### I. INTRODUCTION

# A. RADAR SYSTEMS AND COUNTER-RADAR DIGITAL RF MEMORIES: THE NEED FOR HIGH CAPACITY EMBEDDED PROCESSORS

Low probability of intercept (LPI) radar systems are vital in many regions around the world requiring force protection through surveillance. These radar systems often use low power, continuous waveform (CW) modulations to remain undetected while retaining the "capability to detect and track targets in clutter" [1]. The transmitted CW signal provides a processing gain based on the radar's periodic modulation. The radar return waveform from the target is then distinguished using coherent compression. Many periodic modulation techniques are used for digital CW radar systems such as frequency shift keying (FSK), e.g., Costas sequencing, frequency modulated CW (FMCW), noise and noise modulated waveforms. Also used are polyphase shift keying (PSK) with codes such as the Frank and P4 codes. The PSK techniques have inherently low sidelobes and are also compatible with digital sidelobe suppression techniques. Other CW modulation techniques such as hybrid PSK/FSK combinations have also been recently a topic of active investigation [1].

Lately, much attention has been given to PSK due to the many digital CW modulations available. LPI characteristics are then achieved with a periodic autocorrelation function that has inherently low time sidelobes. The PSK modulations have a code period T containing limited amounts of range bins, each containing differing phase values. The subcode width  $t_b$  is related to both the waveform's range resolution and the 3-dB bandwidth while the "processing gain (PG) of the radar is equal to the number of subcodes" [1]. One important example of a PSK technique is the P4. The P4 code exhibits a perfect periodic autocorrelation in that it has zero sidelobes. Using a polyphase code for CW modulation however, presents a major limitation in that the modulation code period greatly confines the unambiguous range.

Extending the unambiguous range through the use of the Robust Symmetrical Number System (RSNS) has been investigated. By combining the RSNS with the P4

polyphase modulation, the unambiguous range can be divided up into different *moduli*, with each modulus relating to a different P4 code period. Transmitting the moduli (P4 code periods) in series and recombining the ambiguous detection results can resolve the targets range at considerably longer ranges than the unambiguous range pertaining to only 1 code period. In addition, the RSNS-P4 has Gray code properties that can serve to detect target range errors.

A digital RF memory (DRFM) is a device that can receive, store, modulate and retransmit, an RF signal. The DRFM is arguably one of the most important technologies for electronic warfare (EW) since it can retransmit an intercepted radar waveform and can put complex modulations on the return signal such that when integrated within the radar, can deceive for example, the track loop. To create a "structured" false target that has shape or amplitude in range-Doppler space, a standard DRFM kernel is not sufficient. That is, this type of target cannot be accomplished with a DRFM kernel alone. Hence, an augmented kernel must be used such as a high-speed, high capacity Field Programmable Gate Array (FPGA).

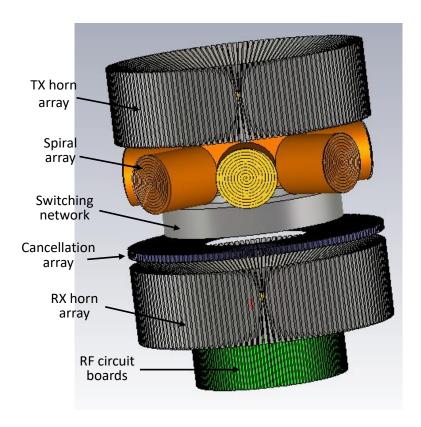

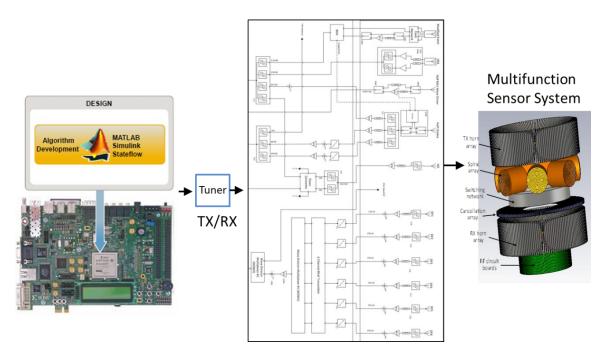

The circuit designs in this thesis are two-fold. First, the circuit design for a post analog-to-digital converter (ADC) compression process for a RSNS-P4 radar signal processor is designed for use within a Multifunction Sensor System for which the antenna is shown in Figure 1. A range compression processor is followed by a Doppler filter bank. This is then followed by a range-Doppler post-detection integration processor. A range compression circuit with a peak power consumption of 6.100W and a post-implementation utilization of 11% was designed. The Doppler filter bank was designed at 400 MHz with a peak power consumption of 2.688W and a post-implementation utilization of 9%. A coherent integration processor at 400 MHz had a peak power consumption of 2.517W and a post-implementation utilization of 9%. The second circuit design concept in this thesis is to design a DRFM single complex range bin processor that accepts the sampled input imaging radar waveform's phase value to first produce the range bin's desired Doppler profile using an accumulator and then the desired radar cross section using a multiplier. The final stage contains the range bin delay where the range bin consists of an adder. This

DRFM processor runs at 500 MHz and is quantified with a peak power 2.543W with a post-implementation utilization of 11%.

Figure 1. Multifunction Sensor System. Source: [2].

#### B. PRINCIPAL CONTRIBUTIONS

For this thesis, the first step was to investigate the concepts involved in radar signal processing. Detailed within the outline, the idea was to grasp an understanding from macroscopic to microscopic. This included the design requirements of an LPI radar, the specific modulation types used within the MATLAB code, and the three-stage compression which was the ultimate task at hand: to replicate the MATLAB version of the three-stage compression within Simulink. These investigations led into the study of DRFMs, which use many of the same design requirements and modulation techniques. The only difference was that DRFMs require an additional microprocessor to ensure false targets or images are injected into a return signal. The first DRFM designs focused purely on false target returns

whereas DRFM designed used today focus on the deception of high range resolution profiling radar and range Doppler imaging sensors.

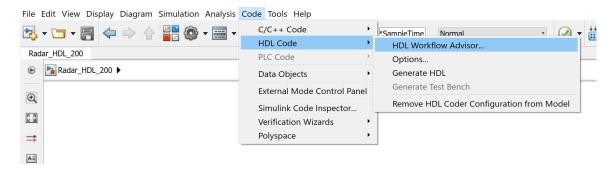

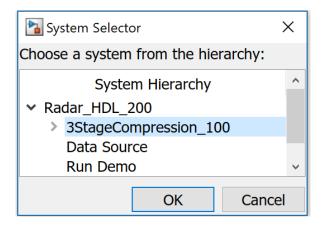

Subsequently, the use of FPGAs was examined. This study began through a MathWorks sponsored course titled "DSP for FPGAs" in Natick, Massachusetts. It was here that the fundamentals of Xilinx Vivado, DSP regarding FPGA synthesis and implementation, and the overall impact of area, power, and timing were introduced. Afterwards, familiarity with the specific FPGA purchased for this thesis was required. Through this familiarity of the FPGA, many design features could be rectified without need of compiling or synthesis/implementation. This in turn saved much time, which in the world of FPGAs, is extremely scarce.

Finally, the process of modeling, synthesis, and implementation of each digital system was investigated. This included many hours of Simulink tutorials and phone calls to MathWorks to ensure that the MATLAB derived results matched precisely with that of Simulink. This proved to be a challenge due to Simulink's reliance on power of twos and HDL specific blocks. Many concepts were used to overcome these requirements such as the periodic ambiguity function, which not only performed the required target detection but also was built in a way that greatly increased the speed at which the FPGA could process the bit streams. Once the models were complete, the synthesis and implementation within Vivado began. About eight runs per model were constructed. Four of the models are considered sub models of the overall three-stage compression model. The idea was to test the subcomponents and relate it to the overall scheme. The relationships were summarized within graphs and subsequently compared.

#### C. THESIS OUTLINE

In Chapter II, the LPI Radar concepts are discussed. This chapter delves into the requirements of LPI Radars, the specifics of how to generate LPI modulation, in addition to the RSNS-P4 Three-stage Compression. Chapter III discusses DRFM architecture as well as the need for augmentation in Electronic Attack (EA). Chapter IV discusses FPGA history and uses, digital signal processing (DSP) on FPGAs, and the specifics of the XILINX Virtex Ultrascale+ FPGA utilized during this research. The modeling, synthesis,

and implementation results are then analyzed and discussed within Chapter V. Chapter VI concludes and provides recommendations for follow-on research.

#### II. LOW PROBABILITY OF INTERCEPT RADAR

### A. REQUIREMENTS

The safest sensor on the modern battlefield is one that can perform surveillance and conduct operations without being identified as doing such. The most capable sensor that can operate in smoke, rain, day or night is the radio frequency sensor that transmits electromagnetic energy for target detection. If the radar transmits high-energy pulses, it can detect targets at long ranges. However, their high peak power, pulsed radiated output signals are easily intercepted by the adversary's non-cooperative intercept receiver. This often leads to them executing an immediate counter-attack using several options with the deadliest being an anti-radiation missile targeting the radar system and operators.

Arguably the most important development in radar system technology is the LPI radar that "uses a special emitted waveform intended to prevent the non-cooperative intercept receiver from intercepting the radiation" as discussed in [3]. The LPI radar emission is a continuous waveform (CW) with low power. Typical output power ranges from one to twenty milliwatts and is usually transmitted from a solid-state array. To perform target measurements, the CW carrier is periodically modulated with a bandwidth that depends on the range resolution. The range resolution also determines the bandwidth. A larger bandwidth can be achieved making it difficult for narrowband receivers to detect and intercept the signal. This technique is much like what is used in telecommunication and radio communications, which is called, spread spectrum. The idea is to deliberately spread the signal in the frequency domain causing it to increase in bandwidth while also lowering its overall peak power. If spread spectrum is used effectively, it can essentially hide the signal within noise making it difficult to intercept.

Another consideration for achieving LPI radar conditions also include using frequency variations that may propagate well for an intended target but cannot effectively be acknowledged by a passive or intercept receiver due to atmospheric absorption. Finally, an antenna design requirement for an LPI radar is to have ultra-low side lobes. The return signal to the radar is, for all intents and purposes, considered feint. Large side lobes would

cause enough interference to deafen the return signal defeating the overall purpose of the LPI radar.

As advancements continue with LPI radars, so come advancements to intercept receivers. Near-peer adversaries are increasingly interested in the ability to perform electronic attack on friendly radar or communication assets. "To See and Not Be Seen" is the first line of defense in countering these intentions [3].

#### B. GENERATING LPI WAVEFORMS

In [4], Paepolshiri states that

since pure CW waveforms cannot resolve the target's range, periodic modulation techniques are used, such as frequency modulated CW, frequency shift keying, noise modulation, PSK, as well as hybrids of these techniques." Paepolshiri found that the initial action to developing CW radar systems using periodic modulation compression is deciding on the necessary range resolution. According to Paepolshiri, this in turn "sets the transmitted bandwidth of the waveform for the above techniques (except for frequency shift keying where the range resolution is dependent to the duration of each frequency).

Paepolshiri goes on to say that

due to the advances in high-speed processing and direct digital synthesis modules, the use of PSK techniques in CW radar is highly advantageous. CW radars that transmit and receive PSK signals can result in LPI radar systems with small range resolution cells and are ideally suited for many sensor applications for situational awareness including minimum input minimum output (MIMO) configurations. [4]

Additionally, PSK allows for RSNS-P4 generation, as depicted in Figure 2, which is the modulated signal utilized within this research.

Figure 2. LPI Waveform Generation and Compression.

### 1. Polyphase Modulation (Polyphase Shift Keying)

The covert nature of polyphase modulation (or polyphase shift keying) is due to the code not being available to the receiver. "The unambiguous range of the radar is limited by the code period. That is, the unambiguous range is limited by the number of subcodes within the code period" [1]. The P4 polyphase code is unique due to it being a perfect code with zero periodic autocorrelation sidelobes. "The phase sequence of a P4 signal is given by

$$\phi_k = \frac{\pi}{N_c} (k-1)^2 - \pi (k-1)$$

(2.1)

where k is the subcode index and  $N_c$  is the number of subcodes within the code period" [1]. The phase distribution is both symmetrical and parabolic. It is these properties that allow the P4 modulation to lend itself nicely to being compatible with the RSNS described next.

#### 2. Robust Symmetrical Number System (RSNS)

"The RSNS is a modular system consisting of  $N \ge 2$  integer sequences with each sequence associated with a coprime modulus  $m_i$ ." Details on the RSNS are given in [1]. An example for N = 3 is

$$\begin{bmatrix} 0 \ 0 \ 0 \ 1 \ 1 \ 1 \ 2 \ 2 \ \dots \ m_1 \ m_1 \ m_1 \ \dots \ 1 \ 1 \ 1 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1 \dots \\ 1 \ 0 \ 0 \ 0 \ 1 \ 1 \ 1 \ 2 \ 2 \ \dots \ \dots \ m_2 \ m_2 \ m_2 \ \dots \ 1 \ 1 \ 1 \ 0 \ 0 \ 0 \ 1 \dots \\ 1 \ 1 \ 0 \ 0 \ 0 \ 1 \ 1 \ 2 \ 2 \ \dots \ \dots \ m_3 \ m_3 \ m_3 \ \dots \ 1 \ 1 \ 1 \ 0 \ 0 \dots \end{bmatrix}.$$

The above sequences "exhibit an integer Gray code property making the RSNS well suited for radar signal processing applications which can benefit from the inherent error detection and correction capability. To use the RSNS for radar signal processing, it is only necessary to know the greatest length of combined sequences without ambiguities, known as the dynamic range  $\hat{M}$  and its position." As described in [1], combining the P4 with the RSNS (RSNS-P4) the phase relationship is

$$\phi_{m_i,k} = \left[ \frac{\pi}{2m_i} \left( RS_{m_i,k} - m_i \right)^2 \right] - \frac{\pi}{2} m_i , \qquad (2.2)$$

"where,  $RS_{m_i,k}$  is the symmetrical residue, and  $k \in \{1,2,...,N_{c_i}\}$  is the phase index. The code length is given as  $N_{c_i} = NN_c = 2Nm_i$ ."

Figure 3. "P4-RSNS Channels and Symmetrical Residues." Source: [1].

## C. RSNS-P4 THREE-STAGE COMPRESSION

The polyphase is transmitted, reflected from the target and upon receive, down converted and digitized, as shown in Figure 4. The digitized RSNS-P4 waveform is strobed into memory for receiver processing. The receive processing consists of range compression, Doppler processing and range-Doppler integration. The total processing gain  $PG_T$  is then  $PG_T = PG_R + PG_D + PG_I$  which is determined from the required  $SNR_{Ri}$  input, the maximum detection range  $R_{Rmax}$ , and the "greatest of constant false alarm rate" (GOCFAR). The range compression determines  $PG_R$  and is determined from the maximum unambiguous detection range and range resolution while the "Doppler filtering process determines  $PG_D$  from the max target velocity at the unambiguous range during the process

sync time. The range-Doppler map is shown in Figure 5. The coherent integration of the range-Doppler" output is used to derive  $PG_I$  over the process sync time [1].

Figure 4. "RSNS-P4 CW Radar - Block Diagram Indicating the Processing Gain Steps." Source: [1].

Figure 5. "RSNS-P4 CW Radar - Range-Doppler Detection Map." Source: [1].

## 1. Range Compression

The range compression multiplies the "fast Fourier transform (FFT) of the complex received signal by the FFT of a reference (transmitted RSNS-P4 phase) waveform and then taking the inverse fast Fourier transform (IFFT). Described in [1], the processing gain from the range compression is

$$PG_R = 10\log(N_{c_i}).$$

(2.3)

## 2. Doppler Filtering

The Doppler filters for a particular range bin are calculated by executing the FFT algorithm on all the range bins collected during the number of code periods  $M_i$ , described in [1] as

$$M_i = 1/(t_b N_{c_i} \Delta f) \tag{2.4}$$

and is a function of the Doppler resolution  $\Delta f$ , the subcode width  $t_b$  and the code period for the modulus  $N_{c_i}$ . The estimated PG from the Doppler filtering is described in [1] as

$$PG_D = 10\log(M_i). \tag{2.5}$$

# 3. Integration

Coherent integration provides a means to enhance the SNR and increase the processing gain, which is described in [1] as

$$PG_I = 10\log(N_i) \tag{2.6}$$

where  $N_i$  is the number of maps that are averaged together coherently. The range-Doppler maps after the coherent integration are shown in Figure 6 "for all three RSNS-P4 channels or moduli (note the different range scales). Targets that have significant velocity separation from the clutter can be detected" [1].

Figure 6. "Range-Velocity Maps for Each of the Three Channels. Target Moves at Relative Speeds Sufficiently Different from the Sea Clutter Spectra." Source: [1].

Figure 7. LPI Signaling Environment and Integration with the Multifunction Sensor System.

## D. CHAPTER SUMMARY

In this chapter, the requirements for LPI radar were presented. PSK modulation as an ideal modulation for LPI radars, the concept of RSNS, and advantages of using RSNS-P4 were also presented. Additionally, the RSNS-P4 three-stage compression was presented which broke down the properties of range compression, Doppler filtering, and coherent integration. The next chapter presents the concept of Digital Radio Frequency Memory and its continuing evolution to deceive current and future radar signatures.

## III. DRFM

### A. DRFM ARCHITECTURE

The DRFM provides the ability to capture radiated emissions and generate precise, coherent replicas, making them important in applications such as signal jamming, deception of covert communications, SIGINT operations, decoys, radar transmitters, simulations, and test equipment as discussed in [5]. A block diagram of single sideband DRFM is shown in Figure 8. At the receive antenna, a bandpass filter is used to pass only the signals of interest. A Local Oscillator (LO) is used to tune the DRFM to intercept the desired signal in the down conversion process. A Low Pass Filter (LPF) removes the components above Nyquist (anti-aliasing) along with unwanted mixer products. This configuration gives good rejection of spurious signals while retaining all the advantages of a conventional superheterodyne. At the output of the LPF, the signal is digitized by an ADC with resolution typically on the order of one to eight bits depending on the DRFM throughput. The higher the resolution, the slower the conversion process. After digitization, the samples are strobed into memory. High-speed, dual-ported memory is often used so the stored digital signal is captured and replayed simultaneously through memory control. "Dual-ported memory usually requires a serial-to-parallel and parallel-to-serial circuitry to achieve the necessary data-rate conversion to match the dual-port memory's input/output bandwidth" [5]. With the use of multi-ported memory, recording and multiple replays can occur simultaneously. The retrieved digital signal is strobed from memory to a DAC to reconstitute the signal back into an analog waveform. After lowpass filtering, the baseband signal is mixed with the LO to reconstruct the radio frequency (RF) version (typically a single sideband modulator). A band-pass filter (BPF) at the output serves to transmit only the desired frequencies [5].

Figure 8. Block Diagram of a Single Sideband DRFM. Source: [5].

Figure 9 shows a block diagram of a double sideband DRFM. As discussed by Dr. Pace in [5], this architecture is similar to Figure 8 except that the phase of the DRFM signal is retained throughout the digitization process using both an I and Q channel. These are produced by the signals Q intermediate frequency (IF) modulator at the input. The Q IF modulator also down converts the input RF signal. Also shown in this configuration is the capability to retrieve the stored digital signal for further, more complicated signal processing using FPGAs or DSPs. This additional processing power can be used to create a variety of complex waveforms. For example, digital image synthesis for inverse synthetic aperture radar (ISAR) counter targeting applications require a level of signal processing that cannot be accomplished with simple memory recall and bit manipulation. The synthesis of the image requires focusing the Doppler frequency at each range bin, and amplitude modulating the output correctly such that the proper image is constructed [5].

Dr. Pace goes on to say that the double sideband (DSB) architecture requires the lowest sampling rate and has the capability of retaining the phase of the signal. The single sideband (SSB) is a less complex architecture; however, a higher sampling rate is required, and the phase of the intercepted signal is not retained. Due to this higher sampling rate, the bit resolution is less [5].

Figure 9. Block Diagram of a Double Sideband DRFM. Source: [5].

Dr. Pace also notes that to process the signals of interest, the DRFM uses a memory controller. The memory controller simply provides the memory address and control signals for the signal storage and recall operations. Several user controls are also available. The storage enable function is used to designate the pulse to be stored. The store address designates where the leading edge of the pulse is to be stored. The recall initiates a recall cycle at the next word clock time. The recall output triggers must be synchronized with the DRFM clock for coherent output. The recall address is the address where recall begins, and the delay time is the throughput delay impressed upon the stored signal [5].

Lastly, Dr. Pace determines that the development of a common DRFM kernel interface specification has been of interest in the Electronic Warfare (EW) community. The purpose of this specification is to define a common narrowband DRFM kernel that meets the jamming requirements of the Department of Defense. This kernel can be utilized in existing and future countermeasure systems. The interface architecture provides potential for efficient upgrades and simplifies DRFM-based system development, leading to a cost savings during development [5].

### B. NEED FOR AUGMENTATION IN ELECTRONIC ATTACK SYSTEMS

In [6], the authors propose that "the need for coherent countering of ISAR imaging sensors remains a high priority for many electronic warfare systems." They state that with the development of an "all-digital image synthesizer (DIS), multiple false-target images

can be generated from a series of intercepted ISAR chirp pulses to provide a novel counter targeting and counter lock-on capability." The authors comment that the DIS "can be also be deployed for Suppression of Enemy Air Defense and any operation that encounters interrogating ISAR imaging sensors." The authors then conclude that the "device can be deployed on aircraft, ships, unmanned air or surface vehicles to provide a superior imaging decoy and deception capability" [6].

In [7], Pak Ang examines and shows the concept of embedding an I/Q Phase Converter and DIS into a DRFM in Figure 10. In Ang's thesis, this DRFM can intercept and store RF waveforms as well as retransmit them subsequently. His thesis adds that upon capturing an ISAR waveform, the DRFM uses a local oscillator to down convert the signal to an intermediate frequency; and that these signals are separated into I and Q components and then digitized by the ADCs into digital samples that are stored in a high-speed memory. An I/Q phase converter extracts phase information from the digitized waveforms to generate phase samples for the Digital Imaging Synthesizer (DIS) to process. Ang continues that after modulation by the DIS is complete, the DRFM converts the processed signal back into an analog form. Finally, the DRFM transmits the analog signal back to the ISAR [7].

Figure 10. Simplified Block Diagram of the DRFM Integrated with the I/Q Phase Converter and DIS. Source: [7].

In [6], the authors remark that the "position of the false target in range can be controlled by delaying in time, the read-out samples going to the image synthesizer." They state that the

image synthesizer performs the complex modulations to synthesize the temporal lengthening and amplitude modulation due to the many recessed and reflective surfaces of the desired false target and generates a realistic Doppler profile for each surface. The FPGA contains a parallel array of identical digital modulators with one modulator for each false target range bin. That is, each modulator synthesizes the part of the overall image that is within the false-target range bin associated with that modulator. [6]

The authors state further that "each complex output pulse I(m,n) is the superposition of  $N_r$  copies of the intercepted pulse, each delayed with respect to one another by the delay within the modulator, scaled differently by the gains  $2^{g(r,n)}$  and phase rotated by  $\phi_{inc}(r,n)$  described in [6] as

$$I(m,n) = \sum_{r=0}^{N_r - 1} 2^{g(r,n)} e^{j\phi(m-r,n) + \phi_{inc}(r,n)}$$

(3.1)

where m represents the sample number within the chirp pulse, n is the pulse number index, and r represents the range bin modulator index. The target extent, amplitude, and target motion are controlled by the gain and phase increment coefficients applied to the FPGA" [6].

## C. CHAPTER SUMMARY

In this chapter, the current and proposed DRFM processes were presented to include the need for an augmentation update within electronic attack systems. This augmentation would require an I/Q Converter and DIS to be integrated into the current DRFM architecture. This addition would ensure that not only traditional radars are deceived but ISAR as well. The next chapter presents an overview of FPGAs, DSP utilizing FPGAs, the specific Xilinx FPGA used during this research, and the simulation process used to recreate the results in the follow-on chapter.

THIS PAGE INTENTIONALLY LEFT BLANK

## IV. FIELD PROGRAMMABLE GATE ARRAY

### A. OVERVIEW OF THE FPGA

In [8], the training course states that FPGAs are a fully reconfigurable resource: the implemented functionality is defined and programmed after manufacture, and this process can be repeated indefinitely. The programmable resources of the FPGA are configured into a desired digital circuit by downloading the user created design as a bitstream. Several steps are involved in creating, verifying, and preparing a design for download to an FPGA [8]. Table 1 provides a list of related technologies like FPGAs.

Historically, Application Specific Integrated Circuits (ASICs) have been faster, extra energy efficient, and typically achieved much more performance than their FPGA counterparts. In [9], the authors observed that implemented FPGA designs "need an average of 40 times as much area, draw 12 times as much dynamic power, and run at one third the speed of corresponding ASIC implementations." In [9], the training course determines that

much more recently, FPGAs including the Xilinx Virtex-7 or maybe the Altera Stratix-5 came to rival corresponding ASIC and application-specific standard parts (ASSP) through the process of delivering considerably minimal power consumption, improved speeds, lower overall production costs, less implementation utilization, and improved options for 'on-the-fly' re-configuration. [9]

Previously, implemented designs requiring and incorporating six to ten ASICs can now produce the same results using a single FPGA [8].

In [8], the training course illustrates that

advantages of FPGAs include the ability to reprogram in the field to fix bugs and may include a shorter time to market and lower non-recurring engineering costs. Vendors can also take a middle road by developing their hardware on ordinary FPGAs but manufacture their final version as an ASIC so that it can no longer be modified after the design has been committed. [8]

Due to ASIC complexity, revenue losses driving higher production costs, and slow time-to-market trends, FPGAs have become a much-needed solution for higher-volume

applications. Mentioned later in this chapter, many FPGAs can perform partial reconfiguration, which allows one section of the unit to be reprogrammed while various other regions keep on running.

Table 1. Related Technologies to FPGAs. Source: [8].

| <b>Application Specific Integrated Circuits</b> | Unlike FPGAs, the function of an ASIC is defined at             |

|-------------------------------------------------|-----------------------------------------------------------------|

| (ASICs)                                         | manufacture, and it cannot be reconfigured. However,            |

|                                                 | ASICs are generally smaller, lower power and when               |

|                                                 | manufactured in high volume, cheaper to produce. The            |

|                                                 | time for design and manufacture of ASICs is longer than         |

|                                                 | for FPGAs, which is a consideration where fast time-to-         |

|                                                 | market is important.                                            |

| Digital Signal Processors (DSPs)                | DSPs historically had one processing engine of fixed            |

|                                                 | wordlength, although modern devices may have several            |

|                                                 | cores. In comparison, FPGAs have parallel processing            |

|                                                 | capabilities, and the designer is not restricted to pre-        |

|                                                 | specified wordlengths. As DSPs and FPGAs offer such             |

|                                                 | different capabilities, they are often used for different tasks |

|                                                 | within a larger system.                                         |

| General Purpose Processors (GPPs)               | While DSP processors are optimized for fast arithmetic,         |

|                                                 | multiply-accumulate type operations, GPPs have the              |

|                                                 | flexibility to deal with a variety of applications but are not  |

|                                                 | suited to the fast arithmetic demanded by DSP.                  |

| Processor Arrays / Sea of Processors            | This type of device exhibits some of the characteristics of     |

|                                                 | an FPGA (parallelism, interconnects) with the processor         |

|                                                 | architecture of a DSP. One of the challenges associated         |

|                                                 | with this type of device is efficiently programming them.       |

| Complex Programmable Logic Devices              | CPLDs are like FPGAs in the sense that they are parallel        |

| (CPLDs)                                         | and reconfigurable, but they are smaller and far less           |

|                                                 | sophisticated. CPLDs have very low power consumption            |

|                                                 | and are suited to "glue logic" type applications.               |

| Structured ASIC                                 | Structured ASICs offer a compromise between ASICs and           |

|                                                 | FPGAs, and there are several slightly different                 |

|                                                 | architectures that fall into this category. The benefits of     |

|                                                 | lower power, and cheaper high-volume production than            |

|                                                 | FPGAs.                                                          |

| FPGA-hardening services                         | The major FPGA companies offer a path to high-volume            |

|                                                 | production based on an FPGA prototype. These are                |

|                                                 | appropriate when the full reprogrammability of an FPGA is       |

|                                                 | not required, are cheaper than standard FPGAs, and faster       |

|                                                 | to produce than ASICs.                                          |

# 1. History

In [10], the article states that the FPGA industry began from "programmable readonly memory (PROM) and programmable logic devices (PLDs)." Both PROMs and PLDs had the ability to be uniformly and "mass-programmed either in a factory or in the field by the user (field programmable)." The programmable logic of the initial FPGA design was "hard-wired between logic gates" [10].

The article adds that in the late 1980s, Steve Casselman proposed to the Naval Surface Warfare Center that a personal computer might be created that could apply 600,000 reprogrammable array gates. The system was funded as well as in 1992 a patent was given because of the program eventually naming Casselman as "the expert in the field of virtual computing" [10].

As found in [11] and [12], David W. Page and LuVerne R. Peterson were awarded with patents in 1985. These patents evolved into several of the "industry's foundational principles for programmable logic blocks, arrays, and gates."

In [13], Ron Wilson claims Altera was founded in 1983, In 1984, Altera delivered the EP300, which was the company's first product. This reprogrammable logic device "offered erasability by shining a UV lamp through the window above the die." The article states that the logic device maintained a quartz window allowing the UV lamp to penetrate the die, erasing the "EPROM cells that held the device configuration" [13].

In [14] and [15], the articles state that Xilinx co-founders Ross Freeman and Bernard Vonderschmitt invented the XC2064 in 1985, which was the first commercially viable FPGA. The sources explain that the XC2064 began a new technology and marketable demand using "programmable gates and interconnects between gates." The XC2064 had "64 configurable logic blocks (CLBs), with two three-input lookup tables (LUTs)." As explained in [16] and [17], after two decades, "Freeman was entered into the National Inventors Hall of Fame for his invention."

Unchallenged, Altera and Xilinx expanded through the latter part of the 1980s to the mid-1990s. At this point, competition began to form within the technological market causing Altera and Xilinx shares to decrease rapidly. In [15], the article explains that by 1993, "Actel (now Microsemi) was serving about 18 percent of the market." In [18], the article reports that by 2013, "Altera (31 percent), Actel (10 percent) and Xilinx (36 percent) together represented approximately 77 percent of the FPGA market."

The ability to mass produce as well as the sophistication of circuitry within FPGAs made significant leaps during the 1990s. The overall use of FPGAs transitioned from being primarily used by telecommunications and networking to be utilized in everyday consumer, automotive, and industrial applications by the early 2000s.

### 2. Current Uses

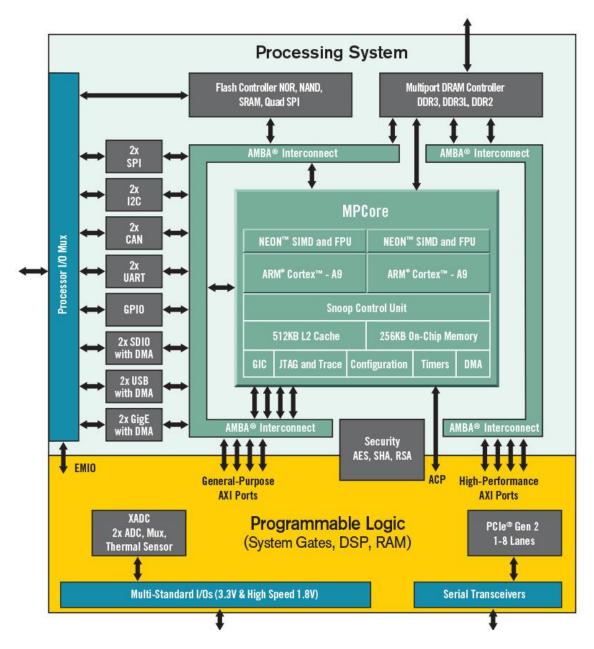

A trend has formed within the past decade to develop a "complete system on a programmable chip" as seen on the Xilinx website in [19]. This idea of having a system on a chip (SoC) involves the combination and assembling of logic blocks and interconnects of previous generations of FPGAs as well as fixed microprocessors and associated peripherals. The website states that the Zynq-7000 All Programmable SoC is an example of such hybrid technology and is depicted in Figure 11. The website adds that this chip "includes a 1.0 GHz dual-core ARM Cortex-A9 MPCore processor embedded within the FPGA's logic fabric." The website concludes that his hybrid technology uses specific high-performance processors and pair them "with programmable logic architectures or multichannel ADC and DAC analog peripherals to their flash-based FPGA fabric" [19].

Figure 11. "A Xilinx Zynq-7000 All Programmable System on a Chip." Source: [19].

Implemented within the FPGA logic are soft processor cores, which provide a hard-macro processor alternate approach. Examples of such technology with soft processor cores are the Nios II, MicroBlaze and Mico32. Reconfigurable computing or systems is the idea of programming current-day FPGAs prior to or during use which allows CPUs to meet any task by reconfiguring themselves. Additionally, non-FPGA technology is emerging.

Microprocessors, such as the Stretch S5000, are software configurable and maintain FPGA-like programmable cores, which, in turn, provide an array of processor cores all within the same chip.

In [20], the article states that "companies like Microsoft have started to use FPGAs to accelerate high-performance, computationally intensive systems (like the data centers that operate their Bing search engine), due to the performance per watt advantage FPGAs deliver." Table 2 provides a list of current FPGA Applications per specified category.

Table 2. Current FPGA Applications. Adapted from [8].

| Aerospace and Defense | Audio                           | Broadcast                 | Automotive                             |

|-----------------------|---------------------------------|---------------------------|----------------------------------------|

| Avionics/DO-254       | Connectivity Solutions          | Real-Time Video<br>Engine | High Resolution Video                  |

| Communications        | Portable Electronics            | EdgeQAM                   | Image Processing                       |

| Missiles & Munitions  | Software-Defined Radio          | Encoders                  | Vehicle Networking and<br>Connectivity |

| Secure Solutions      | Digital Signal Processing (DSP) | Displays                  | Automotive Infotainment                |

| Space                 | Speech Recognition              | Switches and Routers      |                                        |

| Medical          | High Performance Computing    | Industrial            | Integrated Circuit Design   |

|------------------|-------------------------------|-----------------------|-----------------------------|

| Ultrasound       | Servers                       | Industrial Imaging    | ASIC Prototyping            |

| CT Scan          | Super Computers               | Industrial Networking | Computer Hardware Emulation |

| MRI              | SIGINT Systems                | Motor Control         |                             |

| X-ray            | High-end RADARs               |                       | •                           |

| PET              | High-end Beam Forming Systems |                       |                             |

| Surgical Systems | Data Mining Systems           |                       |                             |

| Data Center              | Consumer Electronics    | Security                 | Wired Communications       |

|--------------------------|-------------------------|--------------------------|----------------------------|

| Servers                  | Digital Displays        | Industrial Imaging       | Optical Transport Networks |

| Security                 | Digital Cameras         | Secure Solutions         | Network Processing         |

| Hardware security module | Multi-function Printers | Hardware security module | Connectivity Interfaces    |

| Routers                  | Portable Electronics    | Image Processing         |                            |

| Switches                 | Set-top Boxes           |                          |                            |

| Gateways                 | Flash Cartridges        |                          |                            |

| Load Balancing           |                         | -                        |                            |

| Video & Image Processing | Scientific Instruments | Wireless<br>Communications | Bioinformatics |

|--------------------------|------------------------|----------------------------|----------------|

| High Resolution Video    | Lock-in amplifiers     | Baseband                   |                |

| Video Over IP Gateway    | Boxcar averagers       | Connectivity<br>Interfaces |                |

| Digital Displays         | Phase-locked loops     | Mobile Backhaul            |                |

| Industrial Imaging       | Radio Astronomy        | Radio                      |                |

| Computer Vision          |                        |                            |                |

#### B. DIGITAL SIGNAL PROCESSING ON A FPGA

In [8], the training course states that from a DSP perspective, the resources available on FPGAs have evolved significantly over the last 25 years. Early FPGAs comprised a general-purpose array of CLBs and routing resources, surrounded by IOBs at the edge of the chip. Over time, integrated memory blocks and fast arithmetic slices have been introduced. The functionality of these arithmetic components has increased too. Initially, embedded multipliers were provided, and now DSP engineers have access to an integrated tile containing an adder, multiplier and accumulator. In terms of system integration, embedded processors and communications interfaces have become standard. Naturally, the speed and size of FPGAs has increased also, as have the sophistication of clock management resources [8].

### 1. Introduction to DSP

In the 1980s, the arrival of microprocessors such as Intel 8086 and Rockwell 6502 triggered the so-called Microprocessor Revolution, as stated in [8]. This resulted in commonly accessible and cost-effective computer equipment. Besides several early 1980s home computer systems as well as video gaming machines, the primary development was the IBMPC in 1980 as well as the Macintosh in 1984. This proliferation of computer systems in the workplace, in the market, and the house, entirely altered business processes along with the way info is stored as well as processed. By the 1990s,

multimedia PC was essentially enabled by DSP technology, devices, and algorithms. Additionally, the processing power of DSP (micro-) processors was increased by an order of magnitude with a decrease in price. The digital reliability, repeatability, and programmability of DSP has widely displaced analog systems in both consumer and industrial markets. [8]

Table 3 is a list of the individual DSP technology and components of early 1990 machines and Table 4 is a list of current DSP Applications per specified category.

Table 3. 1990s Multimedia PC Enabled by DSP Technologies. Source: [8].

|                       | Facilities for speech coding / compression (ADPCM, LPC, GSM etc.). Digital filtering, FFT, correlation facilities all within Microsoft Excel spreadsheet.                                              |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _                     | Fast ADC / DAC technology and DSP video coding algorithms for MPEG etc. FFTs, DCTs, sub band coding etc.                                                                                               |

|                       | Most modern disk Speech synthesis, speech recognition. Drives now include a DSP processor for control purposes.                                                                                        |

| Teleconferencing Card | Enabled by DSP coding for audio and video, and adaptive acoustic echo cancellation.                                                                                                                    |

| Sound-card            | 16-bit sound technology sampling up to 48kHz. Sigma delta technology allows low cost implementation; DSP processor implements algorithms for decimation, interpolation, mixing, filtering, coding etc. |

| Speech Processing     | DSP enabled digital recording answering machine.                                                                                                                                                       |

| FAX-modem             | Enabled by adaptive signal processing algorithms for echo cancellation, data equalization                                                                                                              |

Furthermore, a distinction must be made between data processing (DP) and DSP according to the training course. DP and DSP are both

ideally performed by high speed computers which have very fast numerical capabilities. DP is the arithmetic processing of (sampled) stored integer numerical quantities (accounts, salary spreadsheets and so on); fast processing of data is desirable but not essential. DSP is concerned with the arithmetic processing of numerical representations of real world analog quantities. Real time performance is necessary, such that processed outputs are produced as fast as input data is available. For both, a suitable sampling rate must be chosen (not too high and not too low). [8]

In short, DSP means real-time arithmetic operations and DP means non-real time arithmetic operations [8].

Additionally, the training course provides the following DSP Strategies:

# a. Linear Filtering

Removing high frequency background noise from speech. Linear filtering strategies can be used in any application where it is known that two signals can be discriminated by the frequency bands they occupy. [8]

## b. Signal Transforms

Signal component analysis, signal detection etc. Transforming a signal into a different domain often allows a signal to be more conveniently analyzed and viewed. For example, transformation into the s-domain (Laplace) allows more straightforward mathematical manipulation. Transforming into the frequency domain allows the frequency variation of a signal to be seen more easily than in the time domain [8]

## c. Non-linear Signal Enhancement / Filtering

Removing of impulse noise by median / order type filtering. Some signals may often benefit from non-linear filtering. A well-known audio non-linear filter is for impulsive noise, whereby a signal is contaminated by impulses. Given that an impulse essentially contains all frequencies, frequency or phase discriminating filter is not of use. Hence, a median filter may be used whereby the *N* most recent samples are ordered and the median value is chosen. Hence, very large magnitude outliers are likely to be ignored if the duration of the *N* samples is somewhat longer than the duration of the impulsive noise [8].