**Calhoun: The NPS Institutional Archive**

**DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2011-12

# A compression algorithm for field programmable gate arrays in the space environment

Humberd, Caleb J.

Monterey, California. Naval Postgraduate School

http://hdl.handle.net/10945/10623

Downloaded from NPS Archive: Calhoun

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

# NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

## **THESIS**

#### A COMPRESSION ALGORITHM FOR FIELD PROGRAMMABLE GATE ARRAYS IN THE SPACE ENVIRONMENT

by

Caleb J. Humberd

December 2011

Thesis Advisor: Frank E. Kragh

Thesis Co-Advisor: Herschel Loomis

Approved for public release; distribution is unlimited

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |  | Form Approv                 | ved OMB No. 0704–0188                    |                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|-----------------------------|------------------------------------------|--------------------------------|

| Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202–4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704–0188) Washington DC 20503.                                                                                                  |                                            |  |                             |                                          |                                |

| 1. AGENCY USE ONLY (Leave blank) 2. REPORT DATE December 2011 3. RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                            |  | _                           | ND DATES COVERED 's Thesis               |                                |

| <b>4. TITLE AND SUBTITLE</b> A Compression Algorithm for Field Programmable Gate Arrays in the Space Environment <b>6. AUTHOR(S)</b> Caleb J. Humberd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |  |                             | 5. FUNDING N                             | IUMBERS                        |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) Naval Postgraduate School Monterey, CA 93943–5000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                            |  |                             | 8. PERFORMING ORGANIZATION REPORT NUMBER |                                |

| 9. SPONSORING /MONITORING AGENCY NAME(S) AND ADDRESS(ES) N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |  |                             | ING/MONITORING<br>EPORT NUMBER           |                                |

| 11. SUPPLEMENTARY NOTES The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government. IRB Protocol numberN.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                            |  |                             |                                          |                                |

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT Approved for public release; distribution is unlimited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                            |  | 12b. DISTRIBUTION CODE<br>A |                                          |                                |

| 13. ABSTRACT (maximum 200 v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vords)                                     |  |                             |                                          |                                |

| The focus of this thesis is a lossy Fourier-transform-based compression algorithm for implementation on field programmable gate arrays in the space environment. The algorithm computes the fast Fourier transform (FFT) of a real input signal, determines the energy in user-defined time and frequency ranges of interest, and transmits only those frequency domain portions of the signal that exceed the predefined thresholds. Error detection against single event upsets for the FFT is implemented by comparing the sum of the squares of the input to the scaled sum of the squares of the FFT output, which should be equal according to Parseval's Theorem. Error correction is implemented by duplicating the FFT calculation and error detection and choosing the output of the FFT that is not in error. |                                            |  |                             |                                          |                                |

| <b>14. SUBJECT TERMS</b> Fast Fourier Transform, Software Defined Radio, Field Programmable Gate Array, Compression, Lossy Data Compression, Fault Tole Event Upset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                            |  | erant, Single               | 15. NUMBER OF<br>PAGES<br>111            |                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                            |  |                             |                                          | 16. PRICE CODE                 |

| 17. SECURITY CLASSIFICATION OF REPORT Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18. SECURITY<br>CLASSIFICAT<br>PAGE<br>Unc |  | ABSTRAC                     | ICATION OF                               | 20. LIMITATION OF ABSTRACT  UU |

NSN 7540-01-280-5500 Standard Form 298 (Rev. 2-89)

Prescribed by ANSI Std. 239-18

THIS PAGE INTENTIONALLY LEFT BLANK

#### Approved for public release; distribution is unlimited

## A COMPRESSION ALGORITHM FOR FIELD PROGRAMMABLE GATE ARRAYS IN THE SPACE ENVIRONMENT

Caleb J. Humberd Lieutenant, United States Navy B.S., United States Naval Academy, 2005

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

#### NAVAL POSTGRADUATE SCHOOL December 2011

Author: Caleb J. Humberd

Approved by: Frank E. Kragh

Thesis Advisor

Herschel H. Loomis, Jr. Thesis Co-Advisor

Clark Robertson

Chair, Department of Electrical and Computer Engineering

THIS PAGE INTENTIONALLY LEFT BLANK

#### **ABSTRACT**

The focus of this thesis is a lossy Fourier-transform-based compression algorithm for implementation on field programmable gate arrays in the space environment. The algorithm computes the fast Fourier transform (FFT) of a real input signal, determines the energy in user-defined time and frequency ranges of interest, and transmits only those frequency domain portions of the signal that exceed the predefined thresholds. Error detection against single event upsets for the FFT is implemented by comparing the sum of the squares of the input to the scaled sum of the squares of the FFT output, which should be equal according to Parseval's Theorem. Error correction is implemented by duplicating the FFT calculation and error detection and choosing the output of the FFT that is not in error.

THIS PAGE INTENTIONALLY LEFT BLANK

## TABLE OF CONTENTS

| I.         | INT        | RODUCTION                                                | 1        |

|------------|------------|----------------------------------------------------------|----------|

|            | <b>A.</b>  | OBJECTIVES                                               | 2        |

|            | В.         | DESIGN PROCESS                                           | 2        |

|            | <b>C.</b>  | THESIS ORGANIZATION                                      | 3        |

| II.        | BAC        | CKGROUND                                                 | 5        |

|            | Α.         | THE FOURIER TRANSFORM                                    |          |

|            |            | 1. Fourier Analysis                                      |          |

|            |            | 2. The Fast Fourier Transform                            |          |

|            | В.         | COMPRESSION                                              |          |

|            | C.         | COMPUTING IN THE SPACE ENVIRONMENT                       | 13       |

|            |            | 1. Fault Detection                                       |          |

|            |            | 2. Fault Correction                                      |          |

|            | D.         | TARGET FIELD PROGRAMMABLE GATE ARRAYS                    |          |

|            | E.         | SUMMARY                                                  |          |

| III.       | DEX        | VELOPMENT ENVIRONMENT                                    | 19       |

| 111.       | A.         | MATLAB / SIMULINK                                        |          |

|            | В.         | XILINX SYSTEM GENERATOR FOR DSP                          |          |

|            | <b>С.</b>  | XILINX ISE                                               |          |

|            | D.         | MODELSIM                                                 |          |

|            | Б.<br>Е.   | XILINX CHIPSCOPE PRO                                     |          |

|            | F.         | XILINX XUP VIRTEXTM-II PRO DEVELOPMENT BOARD             |          |

|            | G.         | SUMMARY                                                  |          |

| IV.        | FAS        | T FOURIER TRANSFORM COMPUTING                            | 33       |

| _ , ,      | <b>A.</b>  | FFT V4.1                                                 |          |

|            | В.         | FFT V1.0                                                 |          |

|            | <b>С</b> . | FFT V3.2                                                 |          |

|            | D.         | SUMMARY                                                  |          |

| V.         |            | ROR DETECTION                                            |          |

| <b>v</b> . | A.         | FFT ERROR DETECTION WITH PARSEVAL'S THEOREM              |          |

|            | Α.         | 1. Analysis of the Original Error Detection Algorithm    |          |

|            |            | 2. Modification to FFT Error Detection                   |          |

|            | В.         | MEMORY ERROR DETECTION USING PARITY                      |          |

|            | в.<br>С.   | SUMMARY                                                  |          |

|            |            |                                                          |          |

| VI.        |            | ROR CORRECTION                                           |          |

|            | <b>A.</b>  | INITIAL ERROR CORRECTION DEVELOPMENT                     |          |

|            | В.         | MODIFICATION TO REDUCE RESOURCE REQUIREMENTS             |          |

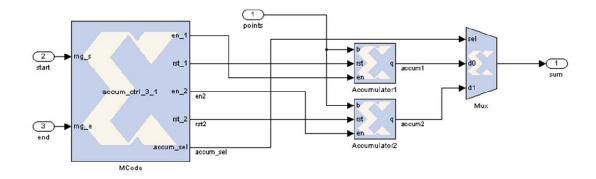

|            |            | 1. Eliminate Redundant Multiply-and-Accumulate Circuitry |          |

|            | C          | 2. Modify Voter to Reduce Usage of Slice Logic           |          |

|            | C.         | PROTECTED FFT WITH THE COMPRESSION ALGORITHM             | 71<br>74 |

|            |            | NI HVIIVI A R V                                          | 1/       |

| VII.  | CONC      | CLUSION                                                | 75 |

|-------|-----------|--------------------------------------------------------|----|

|       | <b>A.</b> | SUMMARY                                                | 75 |

|       | B.        | CONCLUSIONS                                            | 76 |

|       | C.        | RECOMMENDED FUTURE WORK                                |    |

|       |           | 1. Test Error Correction FFT and Compression Algorithm | 77 |

|       |           | 2. Additional Error Correction Capabilities            |    |

|       |           | 3. Develop a Comprehensive Test Set                    |    |

|       |           | 4. Conduct Comprehensive Functional Testing            |    |

|       |           | 5. Implement In Hardware                               |    |

| APPE  | NDIX.     | COMPUTER FILES                                         | 79 |

|       | <b>A.</b> | REQUIRED FILES                                         | 79 |

|       | B.        | INSTRUCTIONS                                           | 84 |

|       |           | 1. Examine System Generator Model                      | 84 |

|       |           | 2. Execute Control Script and Run Simulation           |    |

|       |           | 3. Generate                                            |    |

|       |           | 4. Compile                                             |    |

|       |           | 5. Conduct Behavioral Simulation with ModelSim         |    |

| LIST  | OF RE     | FERENCES                                               | 87 |

| INITI | AL DIS    | STRIBUTION LIST                                        | 89 |

## LIST OF FIGURES

| Figure 1.  | Fourier Theory (After [8]).                                                 | 7 |  |  |

|------------|-----------------------------------------------------------------------------|---|--|--|

| Figure 2.  | Radix-2 FFT signal flow graph (a.) and shorthand notation (b.) (After [8]). |   |  |  |

| Figure 3.  |                                                                             |   |  |  |

| C          | [9])                                                                        |   |  |  |

| Figure 4.  | Eight point constant geometry decimation in time (DIT) FFT (After [8])      |   |  |  |

| Figure 5.  | Eight point normal order DIT FFT (After [8])                                |   |  |  |

| Figure 6.  | Compression (After [4])                                                     |   |  |  |

| Figure 7.  | Compression Algorithm Block Diagram (From [4])                              |   |  |  |

| Figure 8.  | Bitwise Majority Voter (After [14]).                                        |   |  |  |

| Figure 9.  | FPGA Design Process, and Associated Tools (After [6])                       |   |  |  |

| Figure 10. | Example System Generator Design in Simulink                                 |   |  |  |

| Figure 11. | System Generator Options.                                                   |   |  |  |

| Figure 12. | System Generator Resource Estimator.                                        |   |  |  |

| Figure 13. | Compile HDL Simulation Libraries                                            |   |  |  |

| Figure 14. | ChipScope Pro Block Diagram (From [23])                                     |   |  |  |

| Figure 15. | Xilinx University Program Development Board.                                |   |  |  |

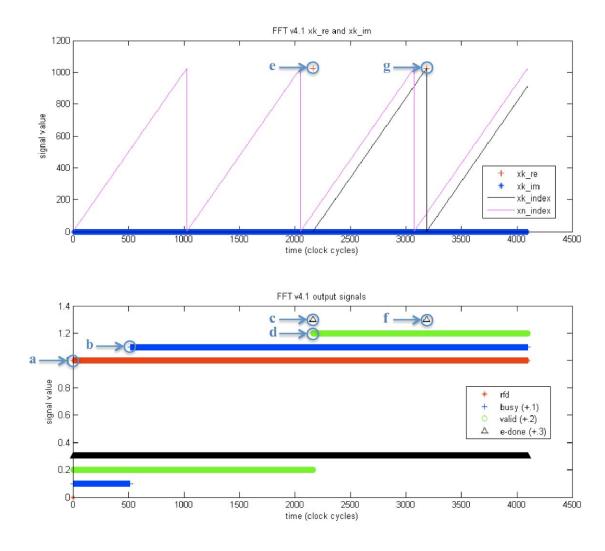

| Figure 16. | FFT v4.1 Configuration Options (After [5])                                  |   |  |  |

| Figure 17. | FFTv4.1 Output Signals (After [5]).                                         |   |  |  |

| Figure 18. | Circuit for Timing Analysis of FFT v4.1 (After [5]).                        |   |  |  |

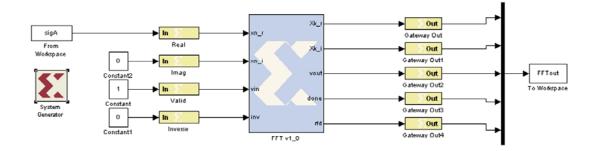

| Figure 19. | Circuit for Timing Analysis of FFT v1.0 (After [5]).                        |   |  |  |

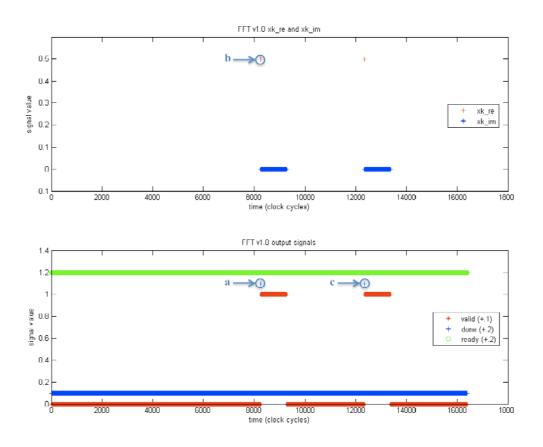

| Figure 20. | FFT v1.0 Output Signals (After [5]).                                        |   |  |  |

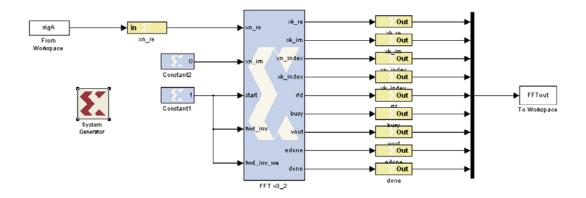

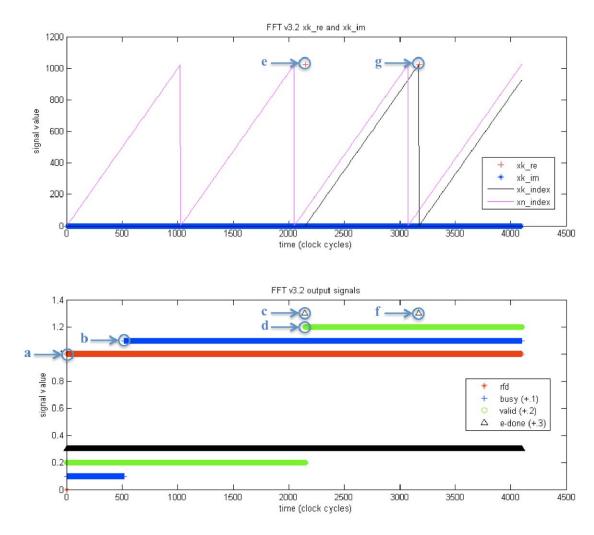

| Figure 21. | Circuit for Timing Analysis of FFT v3.2.                                    |   |  |  |

| Figure 22. | FFT v3.2 Output Signals.                                                    |   |  |  |

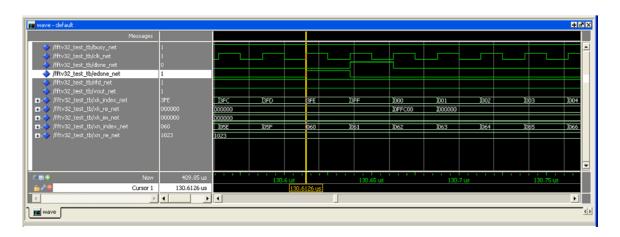

| Figure 23. | FFT v3.2 ModelSim Simulation.                                               |   |  |  |

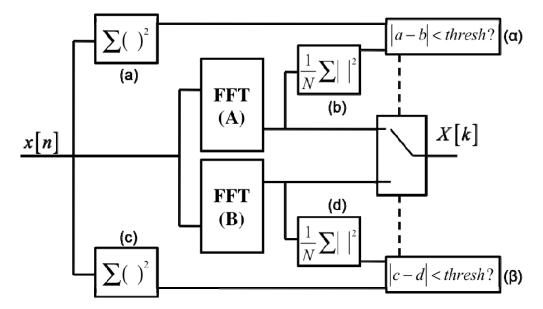

| Figure 24. | Error Detection with Parseval's Theorem (Conceptual) (After [5])            |   |  |  |

| Figure 25. | Error Detection applied to the FFTv4.1 IP block (After [5])                 |   |  |  |

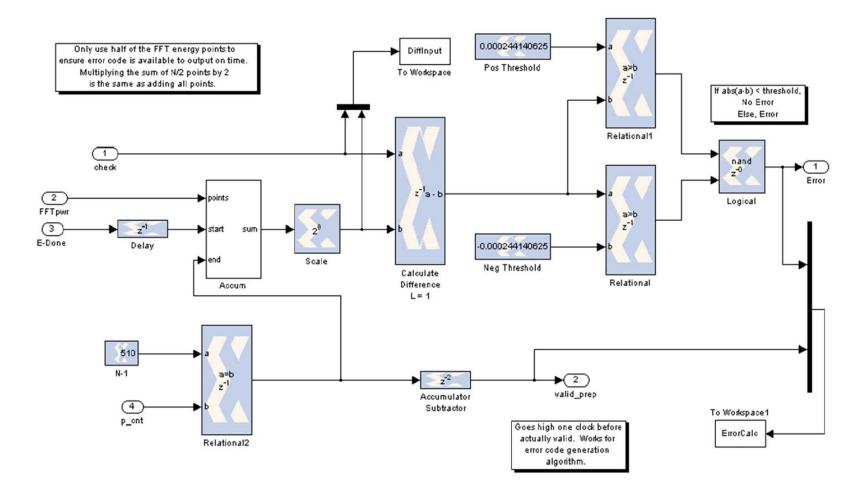

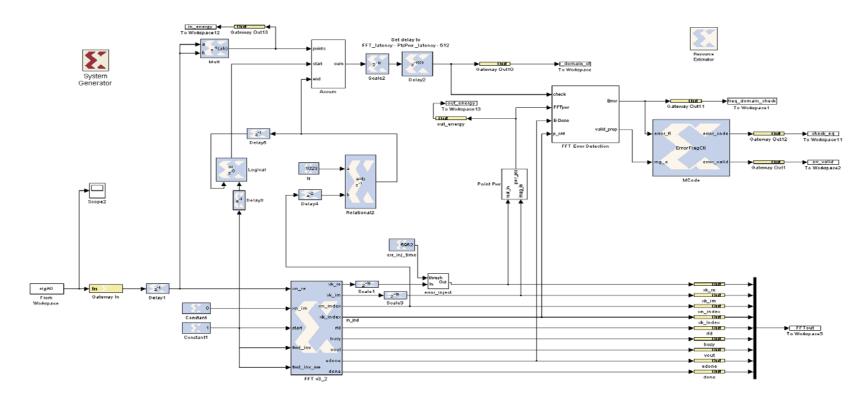

| Figure 26. | "Accum" Subsystem (From [4]).                                               |   |  |  |

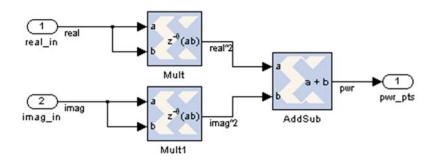

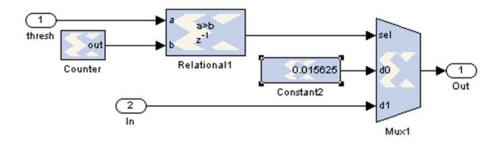

| Figure 27. | "Point Pwr" Subsystem (From [5])                                            |   |  |  |

| Figure 28. | Error Injection circuit (After [5]).                                        |   |  |  |

| Figure 29. | "FFT Error Detection" Subsystem (From [5])                                  |   |  |  |

| Figure 30. | Error Detection Applied to the FFT v3.2 IP Block                            |   |  |  |

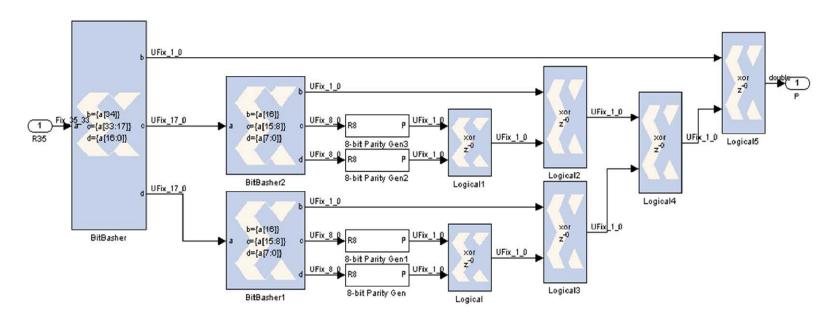

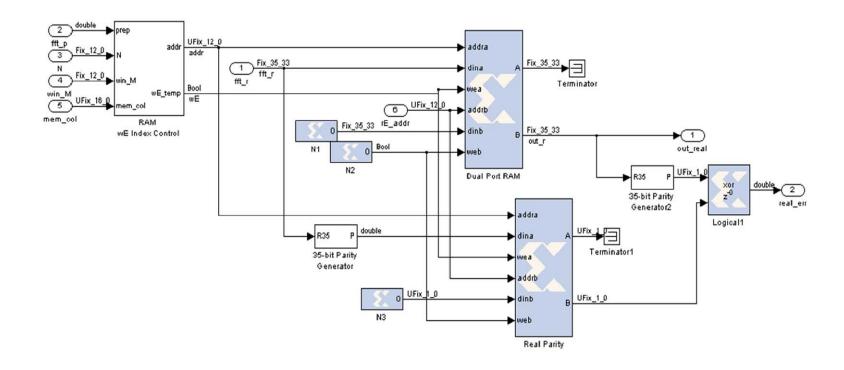

| Figure 31. | Parity Generator (From [5]).                                                |   |  |  |

| Figure 32. | Temporary Memory Subsystem with Parity Check (From [5])                     |   |  |  |

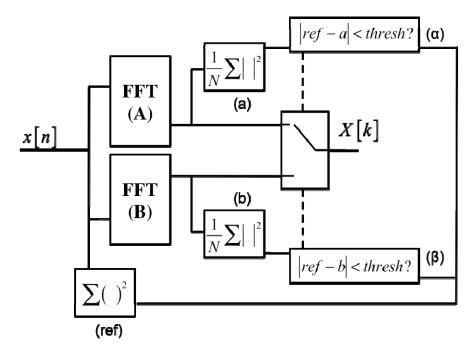

| Figure 33. | Error Correction (Conceptual).                                              |   |  |  |

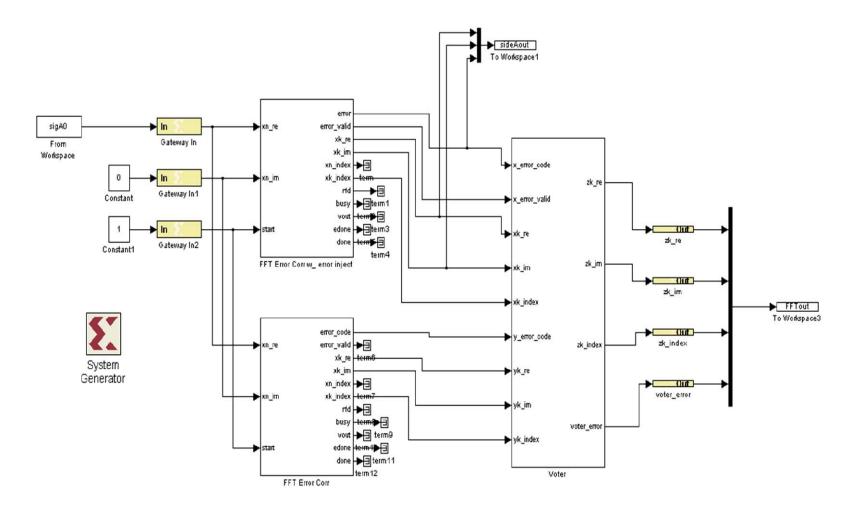

| Figure 34. | FFT Error Correcting Circuit.                                               |   |  |  |

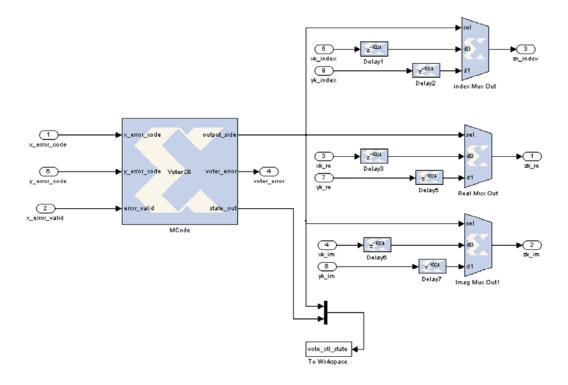

| Figure 35. | Voter Subsystem.                                                            |   |  |  |

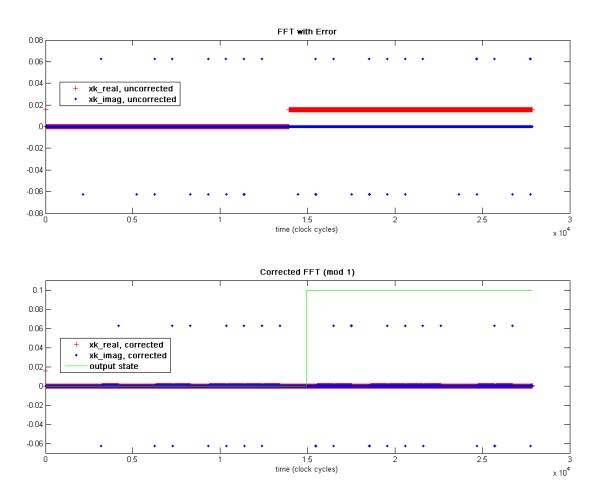

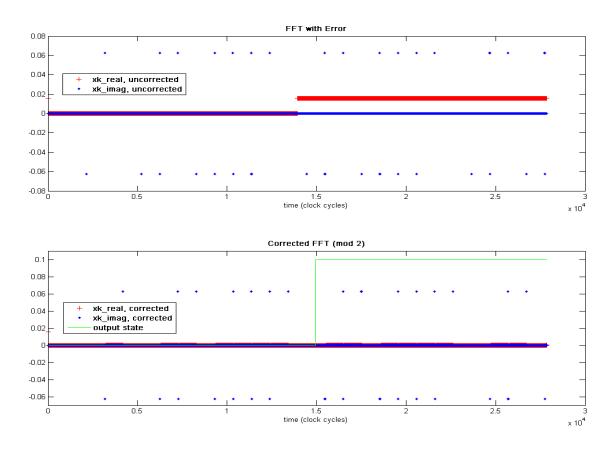

| Figure 36. | Error Correction of a Single Error                                          |   |  |  |

| Figure 37. | Modification to Error Correction (Conceptual)                               |   |  |  |

| Figure 38. | Modification to FFT Error Correction.                                       |   |  |  |

| Figure 39. | Error Correction of Single Error by the Modified Circuit                    |   |  |  |

| Figure 40. | Memory-Based Voter Circuit.                                                 |   |  |  |

| Figure 41. | Error Corrected by Memory-Based Voter.                                      |   |  |  |

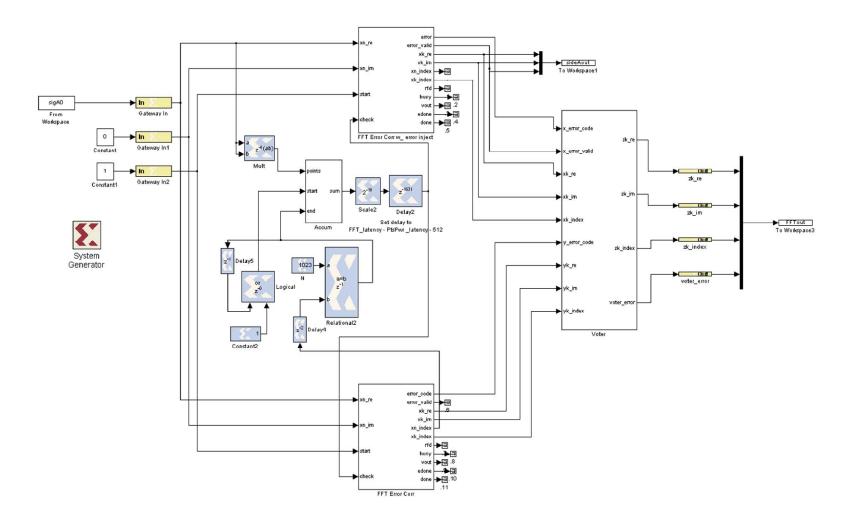

| Figure 42. | Modified Error Correcting FFT.                               | 72 |

|------------|--------------------------------------------------------------|----|

| •          | Modified Compression and Data Formatting Circuit (After [5]) |    |

## LIST OF TABLES

| Table 1.  | Target FPGAs.                                                                        | 16 |

|-----------|--------------------------------------------------------------------------------------|----|

| Table 2.  | FPGA Development Tools                                                               | 31 |

| Table 3.  | FFT v4.1 Resource Utilization on a Virtex <sup>TM</sup> -II Pro xc2vp30–7ff896       |    |

|           | (After [5])                                                                          | 36 |

| Table 4.  | FFT v1.0 Resource Utilization on a Virtex <sup>TM</sup> xcv1000–6fg680 (After [5])   | 38 |

| Table 5.  | FFT v3.2 Resource Utilization on a Virtex <sup>TM</sup> -II xc2v3000–6fg676          | 42 |

| Table 6.  | Resource Comparison of FFT v3.2 and v4.1 on a Virtex <sup>TM</sup> -II Pro           | 43 |

| Table 7.  | Resource Requirements for Compression Algorithm on Virtex <sup>TM</sup> -II Pro      |    |

|           | xc2vp30                                                                              | 52 |

| Table 8.  | Resources Required for Modified Compression Algorithm on Virtex <sup>TM</sup> -II    |    |

|           | xc2v3000                                                                             |    |

| Table 9.  | Truth Table for Error Correction Algorithm                                           | 60 |

| Table 10. | Resource Utilization for Error Correcting FFT on Virtex <sup>TM</sup> -II xc2v3000–  |    |

|           | 6fg676                                                                               | 63 |

| Table 11. | Truth Table for Modified Correction Algorithm.                                       | 65 |

| Table 12. | Resources Required for Modified Error Correction Circuit on Virtex <sup>TM</sup> -II |    |

|           | xc2v3000                                                                             | 67 |

| Table 13. | Resources Required for Modified Voter Circuit on Virtex <sup>TM</sup> -II xc2v3000   | 70 |

| Table 14. | Resources Required for Compression and Data Formatting Subsystems                    | 74 |

| Table 15. | DVD directories.                                                                     | 79 |

| Table 16. | Subdirectories of FFT_error_correct.                                                 |    |

| Table 17. | System Generator Models                                                              | 81 |

| Table 18. | MCode files required for Compression and Error Detection Algorithms                  |    |

|           | (After [5])                                                                          | 82 |

| Table 19. | Supporting *.m files                                                                 | 83 |

THIS PAGE INTENTIONALLY LEFT BLANK

#### LIST OF ACRONYMS AND ABBREVIATIONS

ASIC Application Specific Integrated Circuit

BRAM Block Random Access Memory

CLB Configurable Logic Block

CPLD Complex Programmable Logic Device

COTS Commercial Off-the-Shelf

CW Continuous Wave

DFT Discrete Fourier Transform

DIF Decimation in Frequency

DIT Decimation in Time

DSP Digital Signal Processing

DTFT Discrete Time Fourier Transform

EDIF Electronic Data Interchange Format

FFT Fast Fourier Transform

FIFO First In First Out

FPGA Field Programmable Gate Array

GCLK Global Clock Buffer

GUI Graphical User Interface

HDL Hardware Description Language

IC Integrated Circuit

ICON Interface Control

IDFT Inverse Discrete Fourier Transform

IFFT Inverse Fast Fourier Transform

ILA Integrated Logic Analyzer

IO Input / Output

IOB Input / Output Block

I-Q In-phase and Quadrature

ISE Integrated Software Environment

JTAG Joint Test Action Group (IEEE 1149.1)

LUT Look-Up Table

MATLAB Matrix Laboratory

MUX Multiplexer

ORS Operationally Responsive Space

RAM Random Access Memory

RF Radio Frequency

ROI Range(es) of Interest

RPR Reduced Precision Redundancy

SDR Software Defined Radio

SECDED Single Error Correction, Double Error Detection

SEU Single Event Upset

SOI Signal(s) of Interest

TCL Tool Control Language

TMR Triple Modular Redundancy

USB Universal Serial Bus

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VIO Virtual Input / Output

XUP Xilinx University Program

#### **EXECUTIVE SUMMARY**

Because of their high cost and long lead-time of development, manufacture, and launch, satellites are designed for a long service life in order to recoup investment. This means that the technology aboard operational satellites lags behind the state-of-the-art technology on the ground. In fact, a satellite may be rendered obsolete because the technology onboard has been surpassed by the technology of the ground infrastructure. In addition, the long lead-time results in delays in delivery of vital services to end-users. The Office of Operationally Responsive Space (ORS) is charged with developing strategies to mitigate these twin problems of obsolescence and untimeliness.

One of the methods for increasing the flexibility of communications satellites is through the use of software defined radio (SDR). Because the function of the radio is programmable, the satellite's software can be updated to keep up with the pace of technology on the ground. Field programmable gate arrays (FPGAs) are becoming the design choice for including the processing required to implement an SDR because they can approach the performance of application specific integrated circuits (ASICs) while exceeding the flexibility of general purpose processors (GPPs).

Computing in space has special considerations due to radiation effects. High energy radiation causes several degradations to computational hardware. Single-event upsets (SEUs) are caused when a high-energy particle deposits enough charge in a memory element to change its state. This has special significance to FPGAs used for onboard processing since the configuration of the calculation being conducted is stored in memory. FPGA applications must be designed to detect and correct errors caused by SEUs.

The traditional method to implement error correction is through triple modular redundancy (TMR), where the digital circuit is triplicated and a voter circuit decides the correct calculation based on a majority vote. In order to reduce the logic resources required for error correction, reduced precision redundancy (RPR) can be used to protect arithmetic calculations. In RPR, one full-precision result is calculated along with lower-

precision upper and lower bounds. The full precision calculation is deemed correct if it is between the bounds, otherwise the result returned is a lower-precision average of the two bounds.

Design for FPGA applications differs from writing programs for execution by GPPs. The focus of this thesis is the design flow of FPGA design, from high-level design entry and simulation through low-level functional simulation to hardware implementation. Xilinx System Generator, a high-level graphical design and simulation tool for use within The MathWorks' Simulink® environment, was used to design and test the algorithm. Once the design was behaving as desired, very high speed integrated circuit hardware description language (VHDL) code was generated by System Generator. This code was imported into the Xilinx integrated software environment (ISE) design suite for syntax checking and compilation. Mentor Graphics' ModelSim software was used with ISE for simulating the function of the algorithm defined by the HDL code.

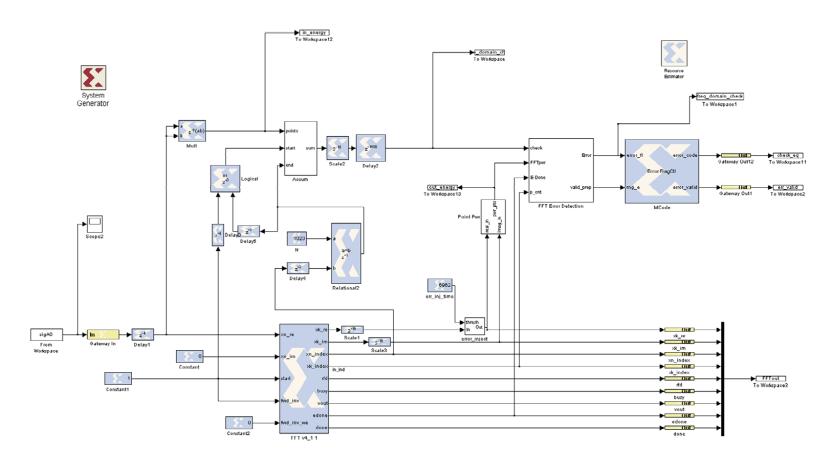

The design of a lossy Fourier-transform-based compression algorithm for implementation on a FPGA-based SDR in the space environment is the focus of this thesis. The compression algorithm was designed by Wright and further refined by Livingston, both students at the Naval Postgraduate School. The algorithm computes the fast Fourier transform (FFT) of a wideband signal, divides it into user-defined time-frequency ranges of interest (ROI), and calculates the energy in those ROIs. If the energy exceeds the user-defined threshold, then the signal within that ROI is forwarded for downlink.

The FFT calculation that comprises the first stage of the compression algorithm is implemented using Xilinx FFT intellectual property (IP) blocks. The original algorithm designed by Wright uses the FFT v4.1 block and was targeted for the Virtex<sup>TM</sup>-II Pro. In order to implement the algorithm on a Virtex<sup>TM</sup> FPGA, Livingston modified the algorithm to use the FFT v1.0 block. The performance of these FFT algorithms is examined and compared to the performance of the FFT v3.2 block, which is supported for implementation on Virtex<sup>TM</sup>-II FPGAs.

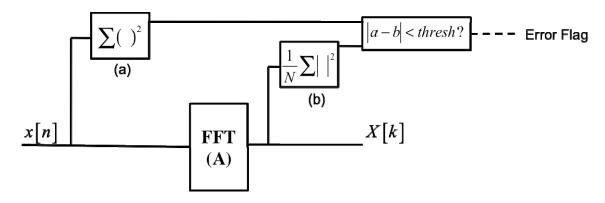

The FFT used in the compression algorithm is a Xilinx, Inc. IP black box. TMR or RPR cannot be implemented directly within the FFT. Livingston implemented error detection by making use of Parseval's Theorem. Parseval's theorem states that the energy prior to the Fourier transform is equal to the energy after the transform. The sum of the squares of the input points to the transform is compared to the sum of the magnitudes squared of the output points scaled by the length of the FFT. If these values are not equal to within a pre-defined tolerance, the calculation is determined to be in error. This method of error detection was analyzed, and the algorithm was modified to be used with the FFT v3.2 block.

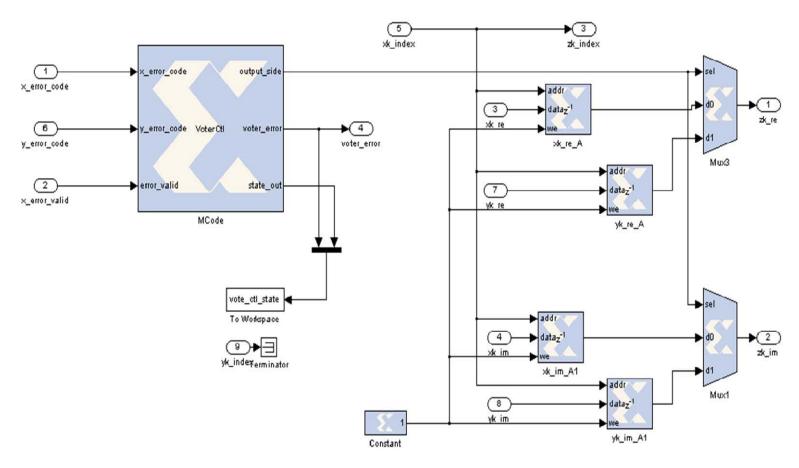

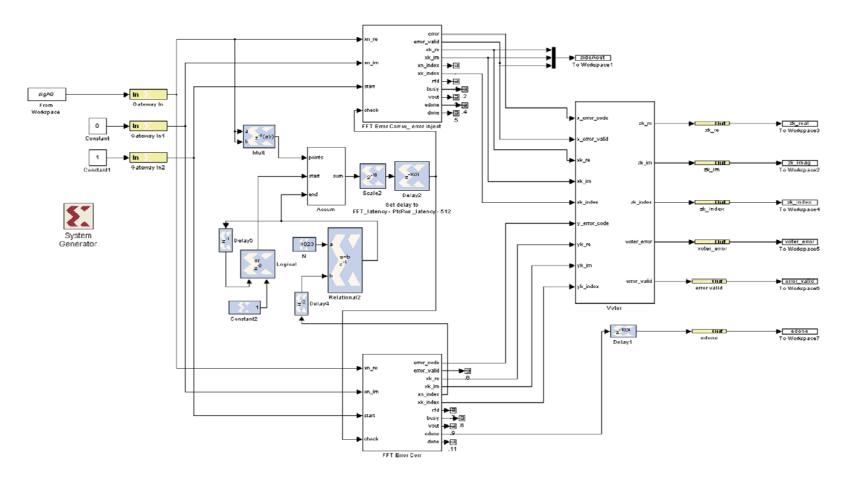

The previously designed error detection algorithm was used as the basis for an error correction algorithm. The error detection circuit was duplicated, and a voting circuit compared the error flags. The output of the FFT not flagged as in error was passed to the ROI analysis and data formatting portions of the compression algorithm. Adjustments were made to the error correction algorithm to reduce the logic resources required for implementation in order to allow the algorithm to be implemented in a Virtex<sup>TM</sup>-II FPGA. Redundant sum-of-squares circuitry was removed from the input to the FFT blocks. The voting circuit was redesigned to implement delays required for aligning data with control signals with random access memory (RAM) rather than logic resources.

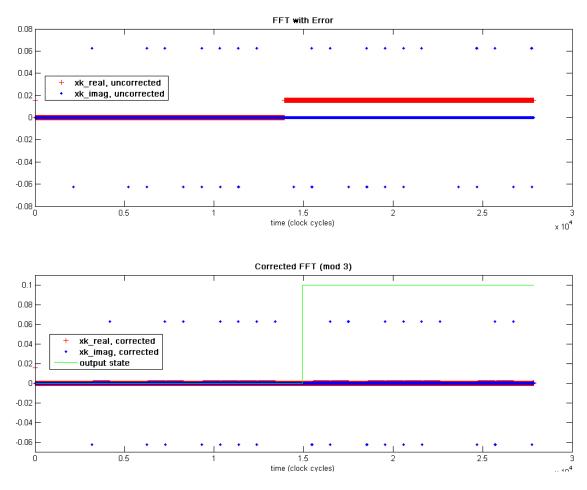

The error correcting circuit was tested by inserting a circuit into the output of one of the FFTs which after a set period of time would switch from the correctly calculated FFT points to an erroneous constant. It was shown that before the error correcting circuitry, erroneous values were present at the output of the FFT. After the error correcting circuitry, it was shown that the values present in the output were corrected. The process of iterative design of the error correcting and voting circuits to fit within the logic resources of the target FPGA validated the use of System Generator as a rapid prototyping, high-level design tool.

THIS PAGE INTENTIONALLY LEFT BLANK

#### **ACKNOWLEDGMENTS**

There are so many to whom I owe a debt of gratitude for the help and support you lent me during my research and writing of this thesis:

To Professor Frank Kragh, for introducing me to the world of software radio. Thanks especially for your encouragement during the final push to get this thesis written.

To Professor Hersch Loomis, for your help with understanding reconfigurable processors and fault tolerant computing.

To Donna Miller and Ron Aikins, for your help in the Communications Research Lab, and with my numerous computer questions on both sides of the campus.

To my fellow Space Systems Engineering students, for helping me through a course of study including mechanics, structures, thermodynamics, and a whole host of subjects foreign to me.

To my parents, Mary and Charlie, for inspiring in me from a young age (and still to this day) a sense of curiosity and love of learning.

To my loving fiancé wife, Nichole, for putting up with the nights and weekends I spent on this thesis – and still marrying me!

THIS PAGE INTENTIONALLY LEFT BLANK

#### I. INTRODUCTION

Satellites are highly complex machines that have long acquisition lead times. Due to the high costs of design, construction, and launch, satellites tend to have long design lives and are often pressed to continue service well beyond their intended life. Satellites in service may be ten, fifteen, or even twenty years old; however, technology continues to advance. The technology aboard otherwise operational satellites may become obsolete because the ground infrastructure has progressed beyond the envisioned capabilities when the satellite was launched [1].

This is a concern for the Department of Defense because the long lead-time in designing, building, and launching spacecraft means that satellites are not available to respond to new demands from warfighters. Operationally Responsive Space (ORS) is a strategy, presented in [1], to provide advanced space-based technology in a more timely manner. ORS provides solutions in three categories: tier 1 involves the re-use of on-orbit assets, tier 2 comprises the rapid launch of existing spacecraft using commercial off-the-shelf (COTS) parts, and tier 3 is the rapid development of new spacecraft designs.

Flexibility of the payload is one design strategy to implement tier 1 solutions. Reconfigurable payloads also allow on-orbit troubleshooting and re-engineering in the event of spacecraft damage or design flaws, mitigating risk of spacecraft mission non-completion. On-board processing, specifically the signal processing and routing used in software defined radio (SDR) applications, provides the flexibility to keep pace with the advance of communication technology in ground-based systems without launching a new satellite [2], [3].

Wright described an FPGA-based SDR for space applications in [4]. His design consisted of a Fourier transform-based bandwidth reduction algorithm with user-defined time-frequency parameters for extraction of signals-of-interest (SOI) from a wide-bandwidth front-end. This design was further refined by Livingston in [5], making it more resource-efficient, splitting the design for a multiple field programmable gate array (FPGA) implementation as well as adding error detection. In this research error

correction is added, building on the previously designed error detection as well as continuing development of the multiple FPGA design.

#### A. OBJECTIVES

The objectives of this research are twofold. First is to continue progress on the existing design. The previous design effort concluded with two algorithms: one that was designed for a three-FPGA implementation and one that incorporated error detection. In this research, error correction, based on the previously designed error detection algorithm, was implemented.

The second objective is to explore the design process for rapid code iteration of an FPGA design using available design tools to implement a signal processing application on an FPGA and utilizing fault-tolerant design principles. The single-chip design was implemented from graphical design and simulation through hardware description language (HDL) design and simulation, and ultimately to hardware implementation and verification.

#### B. DESIGN PROCESS

FPGA design generally takes place using high-level design tools such as block diagrams and schematics. From this high-level concept, the design is developed in a HDL such as VHDL (very high speed integrated circuit [VHSIC] HDL) or Verilog. Unlike a high-level language for general-purpose processors, where commands are executed sequentially, an HDL specifies the interconnections between logic cells within the FPGA where logic level signals are processed in parallel. This parallelism is what lends FPGAs to real-time signal processing applications; however, it also renders HDL designs more difficult to program and debug and even more difficult to decipher (if not well commented) than sequentially-executed computer software. There are design tools to mitigate these drawbacks to HDL designs. Code modularity is one such tool. The Xilinx Integrated Software Environment (ISE) uses the terminology of "cores" to describe these pre-built modules that can be integrated into a design [6].

High-level design tools have also begun to be used for industrial design. By implementing design ideas at a more abstract level, the iterative process of improving and fielding the design can be accelerated while at the same time reducing the instance of syntax and code-level implementation errors. Because this method of algorithm design is more abstract than design in an HDL, it is possible to build a design that cannot be implemented in hardware. For this reason, it is a design tool that cannot be used alone [6].

The design was first modeled using the graphical method described in the previous paragraph in Simulink® using the System Generator plugin from Xilinx. Once the design was working in the Simulink® environment, the design was compiled in VHDL. This VHDL instantiation was then added to a Xilinx ISE project, where it was integrated with other VHDL modules and cores and targeted to a specific FPGA, in this case a Virtex<sup>TM</sup>-II Pro. The VHDL project was then simulated using ModelSim. Penultimately, the ISE project was compiled to bitcode, which defines the resulting FPGA configuration. This bitcode is finally loaded onto the target FPGA. The target FPGA for this research is the Virtex<sup>TM</sup>-II Pro XC2V30 on the Xilinx University Program (XUP) development board, with onboard universal serial bus (USB) Joint Testing Action Group (JTAG), codified as IEEE 1149.1. JTAG is the industry-standard debugging interface for printed circuit boards and internal sub-blocks of integrated circuits (ICs) [6].

#### C. THESIS ORGANIZATION

A presentation of Fourier analysis, including the development of the fast Fourier transform is given in Chapter II, as well as properties of Fourier transforms which are useful to the development of a compression algorithm. The concept behind a data compression algorithm is presented. Radiation effects, especially single-event upsets (SEUs), are presented, the special implications to FPGA designs are discussed, and strategies used implement fault tolerance, error detection, and error correction are presented.

Chapter III, Development Environment, is an overview of the software tools used for this design. The general design flow for the development of an FPGA application is presented along with why each tool was chosen for each design process step. The strengths of each tool are explained, and the limitations are discussed. Also addressed are software setup and use for this design process.

Chapter IV, Fast Fourier Transform (FFT) Computing, contains an investigation of the Xilinx FFT intellectual property (IP) blocks. Previous analysis of FFT v4.1 and FFT v1.0 are reviewed, and FFT v3.2 is investigated as a replacement for FFT v4.1 for implementation on a Virtex<sup>TM</sup>-II FPGA.

Chapter V, Error Detection, is a review of the design work conducted in [5] to add an error detection circuit to the FFT IP blocks. A modification to the design in which FFT v3.2 is substituted for FFT v4.1 is presented.

A design that corrects errors produced by FFT IP blocks is presented in Chapter VI. Several iterations of the design are presented, with a focus on logic resource minimization.

Conclusions from this design work, as well as recommendations for future work to continue to refine both this design as well as the design process, are presented in Chapter VII.

#### II. BACKGROUND

The compression algorithm discussed in this thesis is based on the Fourier transform of the received signal. It allows the user to define specific time and frequency ranges of interest in order to discard information deemed not important. Fault tolerance is implemented using the principles of triple modular redundancy (TMR) as well as a property of Fourier transforms defined by Parseval's theorem.

#### A. THE FOURIER TRANSFORM

#### 1. Fourier Analysis

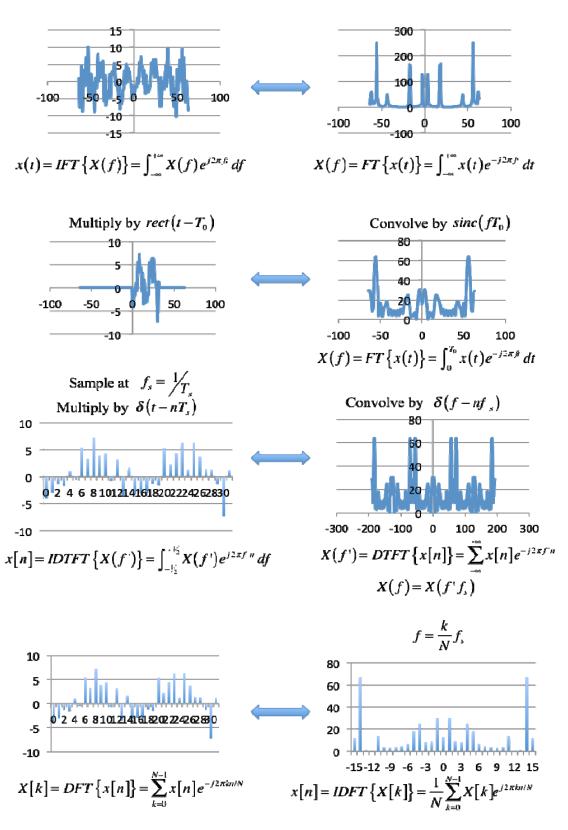

The basis of the compression algorithm is the Fourier Transform. After [5] the relationship between the time domain and frequency domain of a continuous signal is

$$X(f) = FT\left\{x(t)\right\} = \int_{-\infty}^{+\infty} x(t)e^{-j2\pi ft}dt, \qquad (II.1)$$

where X(f) is the Fourier transform of x(t).

The time domain signal is sampled by multiplying by an infinite series of impulse functions separated by the sample interval  $T_s$ . In the frequency domain this sampled signal is a convolution of the original signal with an infinite series of impulse functions separated by the sample frequency  $f_s = \frac{1}{T_s}$ . The sampled time domain signal is  $x[n] = x(nT_s)$ , where n is an integer. The discrete time Fourier transform (DTFT) is defined in [8] as

$$X(f) = DTFT\left\{x[n]\right\} = \sum_{-\infty}^{+\infty} x[n]e^{-j2\pi fnT_s}.$$

(II.2)

The time domain signal x(t) exists for all time, from  $-\infty$  to  $+\infty$ . A time-limited signal is defined as the previous signal multiplied by a rectangle function  $\mathrm{rect}\left(\frac{t-T_o/2}{T_o}\right)$ . The rect function is defined as

$$rect(u) = \begin{cases} 1 & if |u| < \frac{1}{2} \\ 0 & otherwise \end{cases}$$

(II.3)

This multiplication in the time domain corresponds to convolving the frequency domain signal by the  $sinc(fT_0)$  function. The sinc function is defined as

$$\operatorname{sinc}(u) = \begin{cases} 1 & \text{if } u = 0\\ \frac{\sin(\pi u)}{\pi u} & \text{otherwise} \end{cases}$$

(II.4)

The number of samples included in the time window  $N = T_o / T_s$  is an integer. Limiting the transform to this time-limited window gives the Discrete Fourier Transform (DFT) [8],

$$X[k] = \sum_{n=0}^{N-1} x[n] e^{-jk(2\pi/N)n}, k = 0, 1, ..., N-1,$$

(II.5)

where  $k = fN / f_s$ .

A summary of Fourier Theory is shown in Figure 1.

Properties of Fourier transforms that are of consideration for a compression algorithm are the properties of conjugate symmetry and the reversibility of the transform. Conjugate symmetry implies

$$X[k] = X^*[N-k] \tag{II.6}$$

for real x[n] input. The other property of use is that the inverse DFT (IDFT)

$$x[n] = \frac{1}{N} \sum_{k=0}^{N-1} X[k] e^{jk(2\pi/N)n}, k = 1, 2, ..., N-1$$

(II.7)

can be calculated [8].

One property that can cause an undesirable effect is the fact that multiplication in the frequency domain transforms to circular convolution in the time domain,

$$X[k]Y[k] \xrightarrow{\mathcal{F}} x[n] * y[n]. \tag{II.8}$$

This property must be considered during bin analysis since the frequencies of interest are selected by multiplying by a rectangle function. During decompression this multiplication is transformed into a periodic convolution with a sinc function, which causes distortion of the data if not compensated for [5], [8].

Figure 1. Fourier Theory (After [8]).

One other property of Fourier transforms that can be used to implement error detection is the inner product property, also known as Parseval's theorem [5]:

$$\sum_{n=0}^{N-1} x^* [n] y[n] = \frac{1}{N} \sum_{k=0}^{N-1} X^* [k] Y[k].$$

(II.9)

From this equation we see that the energy of the signal prior to the transform is equal to the energy of the signal after the transform scaled by the factor 1/N. By using this property of Fourier transforms, we can relate the input and output of a transform in a less computationally intensive manner. In [5], Equation II.9 is manipulated into the form

$$\frac{1}{N} \sum_{n=0}^{N-1} \operatorname{Re}^{2} \left\{ x[n] \right\} = 2 \sum_{k=0}^{N/2-1} \left( \frac{\operatorname{Re} \left\{ X[k] \right\}}{N} \right)^{2} + \left( \frac{\operatorname{Im} \left\{ X[k] \right\}}{N} \right)^{2}$$

(II.10)

which can be implemented computationally.

#### 2. The Fast Fourier Transform

The DFT is a discrete input, discrete output function and is suitable for computation. As discussed in [7], direct computation of the DFT requires  $O(N^2)$  computations. By taking advantage of symmetries within the DFT, we can reduce the number of required computations to  $O(N\log_2 N)$  with a class of algorithms known as fast Fourier transforms (FFT).

To simplify notation when discussing the DFT and FFT, the phase factor, or "twiddle factor," is written

$$W_N = e^{-j(2\pi/N)}$$

. (II.11)

The DFT has symmetry about N/2 such that

$$w_N^{k+N/2} = -w_N^k . {(II.12)}$$

The DFT also has periodicity of N such that

$$w_N^k = w_N^{k+N}. (II.13)$$

For N=2 and substituting the phase factor given by Equation (II.11) into the DFT given by Equation (II.5) we get

$$X[k] = \sum_{n=0}^{1} x[n] w_2^{nk} = x[0] w_2^{0k} + x[1] w_2^{1k}$$

(II.14)

where

$$w_2 = e^{-j(2\pi/2)} = e^{-j\pi} = -1,$$

(II.15)

$$w_2 = e^{-j(2\pi/2)} = e^{-j\pi} = -1,$$

(II.15)

$w_2^{0k} = (-1)^0 = 1,$  (II.16)

and

$$w_2^{1k} = (-1)^k . (II.17)$$

For k = 0...1, the resulting DFT points are

$$X[0] = x[0] + x[1]$$

$X[1] = x[0] - x[1]$  (II.18)

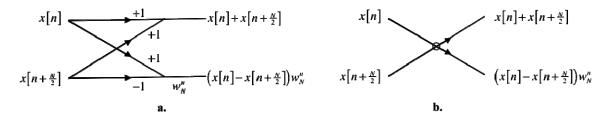

The signal flow graph, or "butterfly" operator, shown in Figure 2 represent the resulting operation.

Figure 2. Radix-2 FFT signal flow graph (a.) and shorthand notation (b.) (After [8]).

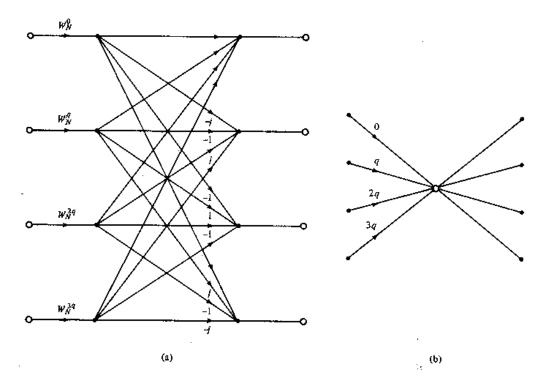

Similarly, as discussed in [7], the radix-4 FFT can be calculated by dividing the input into four summations. The radix-4 FFT achieves a 25 percent reduction in the number of complex multiplies required over the radix-2 FFT. The signal flow graph of a radix-4 FFT is shown in Figure 3.

Figure 3. Radix-4 FFT signal flow graph (a.) and shorthand notation (b.) (From [7], [9]).

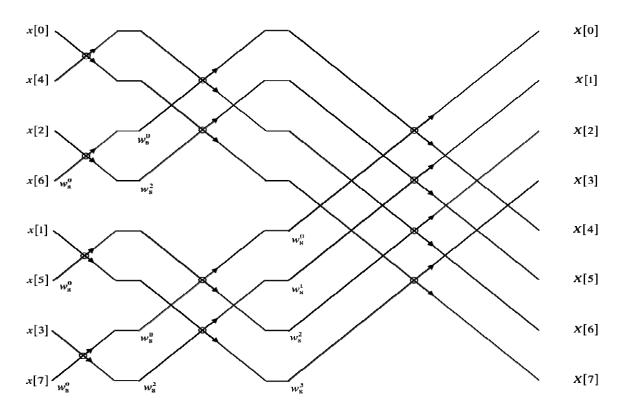

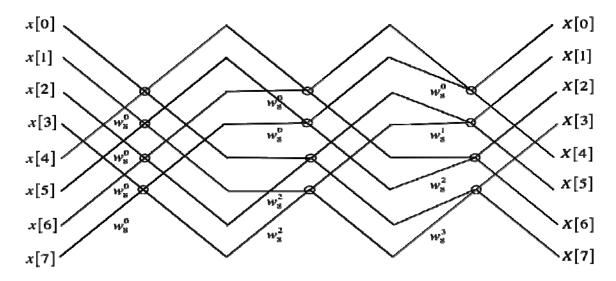

The FFT algorithm can be used for any signal with a length that is a power of two. To do so, the butterflies are cascaded. An eight-point, radix-2, decimation in time (DIT) FFT is shown in the signal flow graph in Figure 4.

When implementing the FFT in software or in an FPGA, the algorithm can be initiated with either in-place addressing or constant geometry. For constant geometry addressing, shown in Figure 4, the output of the butterfly is written into the same memory locations that the input was read from. This results in either the input or output points' memory locations being out of order in memory. In normal order addressing, shown in Figure 5, the input and output values are in order in memory. However, since the butterfly operators cannot write to the same memory locations from which they read their input values, this geometry requires additional memory resources to implement [5], [8].

Figure 4. Eight point constant geometry decimation in time (DIT) FFT (After [8]).

Figure 5. Eight point normal order DIT FFT (After [8])

#### B. COMPRESSION

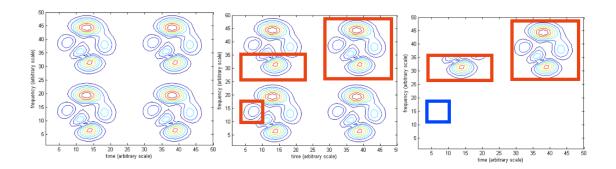

The bandwidth of a SOI may be much less than the passband of the radio frequency (RF) front-end of a wideband digitizing SDR. In addition, the signal-ofinterest may not be a continuous wave (CW) signal but pulsed or otherwise interrupted periodically such that there are periods of silence in the SOI. Therefore, the SOI can be represented by fewer bits than if the entire passband is digitized. In order to achieve this reduction in the downlink data rate, the received and digitized signal is divided into userdefined time and frequency ranges of interest, referred to as "bins." The energy present in each bin is compared against an operator-specified threshold, and the points representing the signal of interest are only downlinked when bin energy exceeds the threshold. This method for reducing downlink data rate was presented in [4], and a conceptual representation of this is illustrated in Figure 6. Shown in the first plot is a time-varying signal. The colored contours represent the energy contained in the signal as a function of time and frequency. In the second plot, the red boxes denote the user defined time-frequency ranges of interest (ROI) overlaid on the signal. The third plot shows the signal that would be included in the downlink in the red boxes, while the blue box indicates a bin of interest in which the energy did not meet the required threshold and no data is downlinked.

Figure 6. Compression (After [4]).

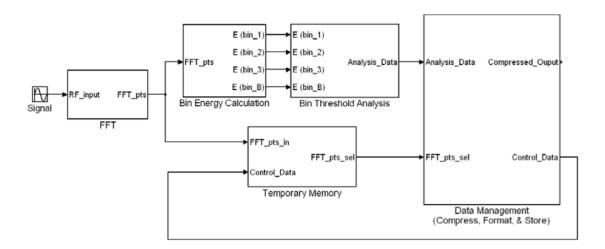

The algorithm developed by Wright and presented in [4] to conduct this compression is illustrated in Figure 7. The FFT of the time domain signal is calculated, and the frequency domain points are passed to the bin energy calculation and bin energy

threshold algorithms. The data management block then reads the FFT points in the bins meeting the energy threshold and formats the data points for downlink. There are four bins available with user defined time and frequency ROI.

Figure 7. Compression Algorithm Block Diagram (From [4]).

#### C. COMPUTING IN THE SPACE ENVIRONMENT

As discussed in [10], choices for implementing onboard processing include general-purpose processors (GPPs), application-specific integrated circuits (ASICs), and FPGAs. For performing the same calculations on streams of data, such as real-time digital signal processing (DSP), an ASIC provides the most performance to power consumption of these alternatives. Their downside is that they require extensive development before they are produced, and they cannot be modified beyond their intended purpose. GPPs are the most flexible option; however, their strength lies in sequential operations in which the calculations performed on the data differ from one operation to the next. Their throughput for performing the same calculation on streaming data is lower than ASICs for the same clock speed. FPGAs offer the capability to process streaming data as efficiently as an ASIC with the ability to modify the application for which they are being used [10].

### 1. Fault Detection

FPGAs come at the cost of higher power consumption as well as being susceptible to their programming being altered by single-event upsets (SEU) due to high-energy particles present in the space environment. FPGA application design for space applications must take these issues into consideration. A SEU occurs whenever a high-energy particle impacts the semiconductor material and deposits enough charge to change the state of a single bit. The effect of this unintended state change depends on whether the affected bit is in data memory is a data bit in the midst of the calculation circuitry or is part of the FPGA configuration memory [10].

Parseval's theorem states that the energy into the DFT must equal the energy out. Because of this property, it is possible to detect whether or not the calculation of the DFT contains an error. In [5], Livingston implemented error detection for a FFT through application of Equation (II.10). In this application the accumulated (summed) squared input points to the DFT are compared to the accumulated squares of the output points, scaled by 1/N. If the input to the DFT is limited to a real, as opposed to in-phase and quadrature (I-Q) signal, then the output only has to accumulate squares of the first half of the output points and scale by 2/N. This saves memory requirements as well as latency in the error detection.

### 2. Fault Correction

Electronics in the space environment must be designed to tolerate high-energy particle radiation as discussed in [11]. Some of this tolerance must be implemented at the physical level: shielding is used to reduce the incidence of radiation on the electronics, and specialized semiconductor design techniques are used to mitigate the long- and short-term effects of radiation on the electronics. Beyond these methods, the algorithm implementation in software and hardware must also be made radiation tolerant.

Errors in data memory are usually checked and corrected using a parity scheme, such as a single error correction, double error detection (SECDED) Hamming code. When data is read into memory, parity check bits are calculated and stored in a separate memory location. When the data is read out, parity is calculated again and compared

against the original parity bits. If the parity check bits are not equal, an error occurred, and if a single error, the check bits can be decoded to point to the location of the error [12], [13].

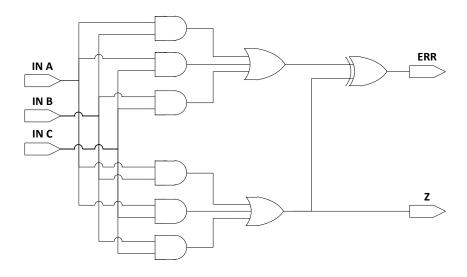

Configuration errors must be detected and corrected by a circuit which itself may be in error. This has been done traditionally through triple modular redundancy (TMR). In TMR, the calculation is performed three times, the results are compared, and any erroneous result is discarded. The price of TMR is more than three times the required logic resources, since the calculation circuitry must be triplicated, and a voting circuit is required to check the results. The voting circuit shown in Figure 8 compares the result of each bit from each of the three calculations. This circuit can correct any one error from the inputs and can detect when the voting circuit itself is in error [12].

Figure 8. Bitwise Majority Voter (After [14]).

A method of redundancy requiring fewer resources, Reduced Precision Redundancy (RPR), was discovered by Snodgrass and presented in [12], and expanded upon by Sullivan in [14]. In RPR the full precision result is calculated once, while a lower-precision upper and lower bound are calculated. If the full precision calculation is outside of the calculated bounds, it is assumed to be in error and the reduced precision bound is returned. This technique results in lower logic resource use and power

consumption at the cost of a more complex voting circuit as well as a less precise result when the full precision calculation is found to be in error. Reduced precision redundancy is also limited to arithmetic processes. Logic control operations must be protected using TMR.

### D. TARGET FIELD PROGRAMMABLE GATE ARRAYS

This algorithm is targeted for the Virtex<sup>TM</sup> family of FPGAs manufactured by Xilinx. A summary of the devices considered is shown in Table 1. These devices are fully described in [15], [16], [17], and [18].

Table 1. Target FPGAs.

| Family                       | Device   | Configurable Logic Blocks | Multipliers               | Block RAM     |

|------------------------------|----------|---------------------------|---------------------------|---------------|

| Virtex <sup>TM</sup>         | xcv1000  | 6144                      | 0                         | 32 (512 Byte) |

| Virtex <sup>TM</sup> -II     | xc2v3000 | 3584                      | 96                        | 96 (18 kB)    |

| Virtex <sup>TM</sup> -II Pro | xc2vp30  | 3424                      | 136                       | 136 (18 kB)   |

| Virtex <sup>TM</sup> -4      | xc4vlx25 | 2688                      | 48 (Xtreme<br>DSP blocks) | 72 (18 kB)    |

The devices considered include the older Virtex<sup>TM</sup> and Virtex<sup>TM</sup>-II devices, which are in use on legacy space platforms. The newer Virtex<sup>TM</sup>-4 device is considered because it is also available in a radiation hardened version. The Virtex<sup>TM</sup>-II Pro device is included for comparison since that device was the one available for this research.

The oldest device, the xcv1000, has the most configurable logic blocks (CLBs). This device does not include the embedded multipliers, which degrades its ability to perform DSP calculations such as the FFT. This device can conduct algorithms that require multiplication; however, the multipliers must be constructed from the available

CLBs. Also, this device has the least amount of available block random access memory (RAM), which significantly limits the amount of data that can be processed at one time [15].

The newer devices all contain fewer CLBs but include embedded 18x18 bit multipliers, reducing the demand for CLBs. These devices also include significantly more RAM than the Virtex<sup>TM</sup>. This increased on-chip RAM allows faster processing since algorithms do not need to make as many off-chip data accesses. The Virtex<sup>TM</sup>-4 has the fewest number of embedded multipliers; however, they are arranged in XtremeDSP blocks in which the 18x18 bit multiplier is followed by a 48-bit accumulator. The Virtex<sup>TM</sup>-II Pro includes a PowerPC® core, which was not used in this research [16], [17], [18].

### E. SUMMARY

Several high level concepts that support the development of a Fourier transform-based, fault tolerant compression algorithm were introduced in this chapter. A summary of Fourier analysis was discussed, and the development of the fast Fourier transform was presented. Challenges associated with spaceborne computing were discussed, and the Triple Modular Redundancy and Reduced Precision Redundancy methods for correcting errors caused by single event upsets were presented. A number of design tools that enable the designer to develop the design at a high level, and then remove the layers of abstraction down to implementing the compression algorithm in hardware are introduced in the next chapter.

THIS PAGE INTENTIONALLY LEFT BLANK

## III. DEVELOPMENT ENVIRONMENT

Design for FPGAs is quite different and distinct from writing a sequential computer program. The tools used for development of FPGA applications are designed to allow the designer to control the sequential and parallel behavior of the logic. A design to be implemented on an FPGA is mapped out by the designer as a block diagram, flow chart, or schematic. From this high-level abstraction of the desired behavior of the design, the designer develops components of the circuit in an HDL. Design in an HDL allows full control over the hardware-level behavior of the algorithm while still allowing abstractions that aid the designer, such as human-readable variable names. This control at the hardware level comes at the price of a more difficult to understand design. Unless the HDL files are well documented, anyone other than the original designer may never be able to understand the purpose of the design [6].

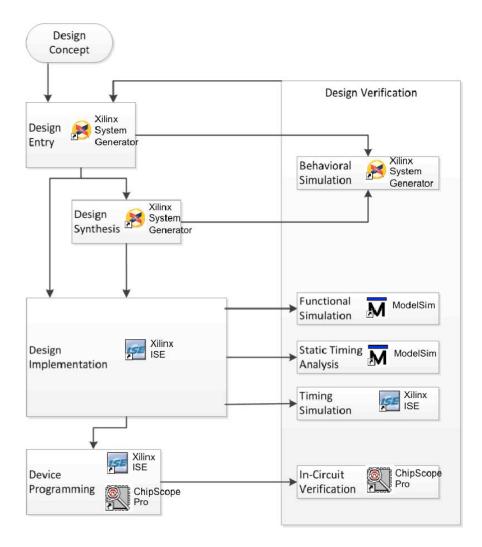

To increase the ease and speed with which a design can be developed and altered, high-level design tools have become popular. With these tools, HDL components and their interconnections are represented graphically. As discussed in the introduction to [6], abstracting away the complexities of an HDL allows the designer to focus on the function of the design. The analogy is that a programmer writing a DSP algorithm will code most of the algorithm in a high-level language and only code portions with strict performance requirements in assembly code. In the same fashion, once the behavioral design is complete, the high-level design tool outputs a lower-level instantiation of the design for functional development, simulation, and eventual implementation in hardware. At each step in the design process, results of the verification are used to refine the initial design. This design flow, from high level algorithm development, HDL-level implementation, and hardware implementation is illustrated in Figure 9, along with the design tool used in that step.

This chapter is an overview of the design tools used for this research. An overview of the software packages, their features, and their operation are presented. Also discussed are the relative advantages as well as the potential pitfalls of each software package. The design tools discussed are summarized in Table 2 at the end of the chapter.

Figure 9. FPGA Design Process, and Associated Tools (After [6]).

## A. MATLAB / SIMULINK

MATLAB (Matrix Laboratory) is a high-level numerical analysis oriented programming language developed by The Math Works<sup>®</sup>. Simulink® is a graphical modeling and simulation application which works within the MATLAB environment.

The primary use of MATLAB for this design was the generation of input signals and the analysis and display of the output. MATLAB is designed for numerical analysis and the manipulation of large arrays of numbers. MATLAB scripts, or M-files, were the primary means for setting up environment variables. The plotting tools were used for generating displays of input and output. In multiple FPGA instantiations of the

algorithm, M-files were also used to script the execution of the separate models and control the routing of signals from one module to the next, simulating the function of the common backplane in hardware [5].

Models built in Simulink® are useful for investigating the behavior of applications destined for FPGA implementation; however, the timing of signals through the model is not accurate. Simulink® allows models to be run in discrete or continuous time; however, this design process made use of only discrete time modeling, where each time step represents one clock cycle of the FPGA.

### B. XILINX SYSTEM GENERATOR FOR DSP

Xilinx System Generator is a plugin for Simulink, which adds the functionality to develop applications for Xilinx FPGAs using the high-level, graphical modeling and simulation environment of Simulink. The modeling environment uses Simulink® and MATLAB to generate input signals, pass the signals into the System Generator model, and collect output signals for post-processing and display [19].

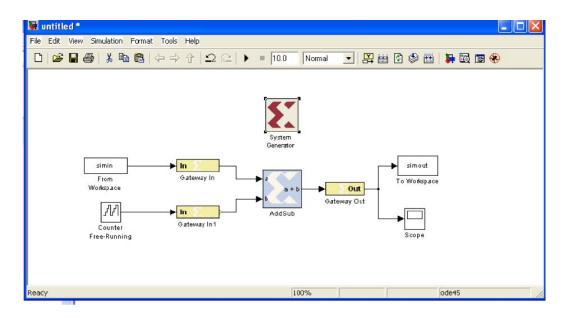

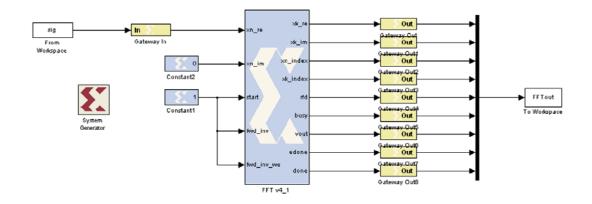

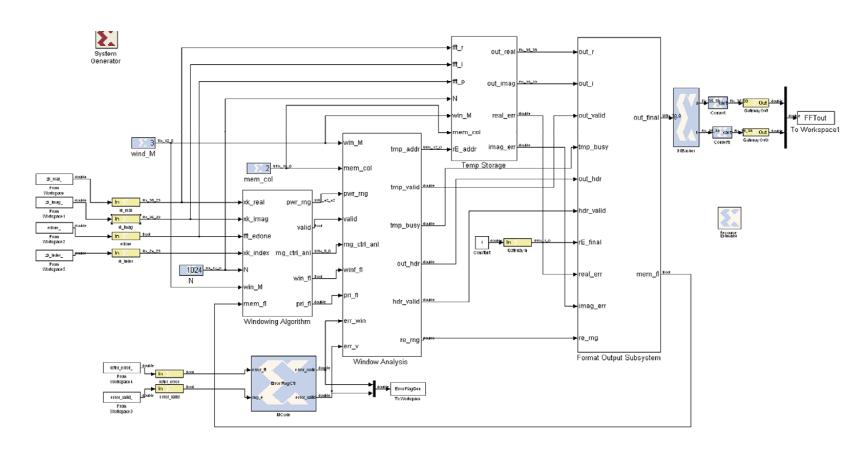

An example System Generator design is shown in Figure 10. The plain white blocks are standard Simulink® blocks, while the blocks with the Xilinx "X" logo are System Generator blocks. The Gateway In and Gateway Out blocks represent bonded Input / Output Blocks (IOB) on the FPGA, and all blocks between the input and output represent functional segments of the user's choice of HDL. The stand-alone System Generator block controls the instantiation and compilation of the block diagram into HDL [19].

Figure 10. Example System Generator Design in Simulink

Simulation of applications for FPGA implementation using System Generator is more faithful to the actual behavior of the algorithm than a simulation using just Simulink. The reason is that the System Generator blocks represent segments of HDL code with the attendant constraints. System Generator outputs HDL which can then be modified and compiled with FPGA synthesis tools [19].

The version of System Generator used is version 10.1 because this is the last version that supports the original Virtex<sup>TM</sup> devices which are still in use in certain applications. As discussed in [20], this version of System Generator requires MATLAB R2007a / Simulink®6.6 or MATLAB R2007b / Simulink® 7.0. This version also requires Xilinx ISE version 10.1.

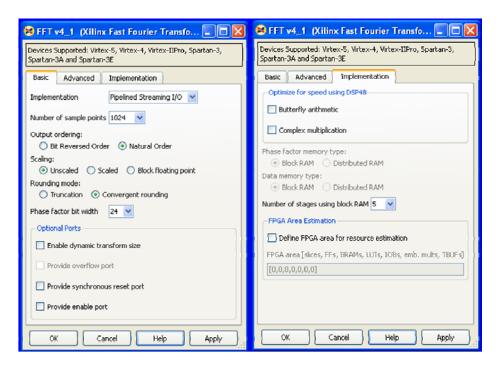

System Generator for DSP contains many blocks that are specific functions for DSP. The blocks under consideration for this design were the FFT v1.0, FFT v4.1, and FFT v3.2 blocks, discussed in Chapter IV. These pre-built blocks take advantage of specific on-chip DSP-specific logic resources (such as the XtremeDSP slices in the Virtex<sup>TM</sup>-4). These blocks make use of Xilinx intellectual property (IP) core generation algorithms to optimize the performance of the design for the chosen FPGA [19].

If the desired function block does not exist, the MCode block may be used to implement the desired function. MCode blocks allow the insertion of a MATLAB M-file into a System Generator design to allow scripting and control of signal flow. This gives the designer a higher-level way to implement control over the logic, rather than designing a state machine from individual gates, allowing for increased flexibility of the control of the design. However, as discussed in [20], MATLAB algorithms, such as the MATLAB fft() function, cannot be implemented using this method. This design uses MCode blocks to implement state machines based on control signals generated by the logic circuitry to control the flow of signals within the design.

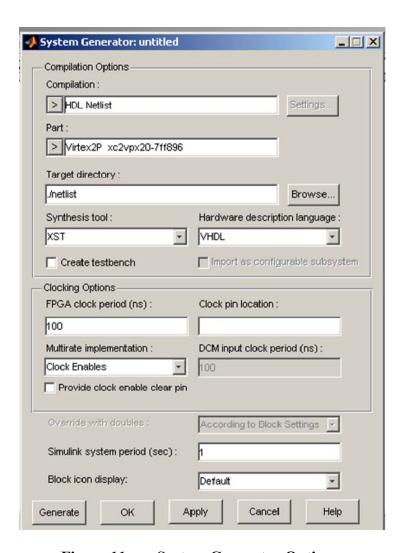

The System Generator block contains the synthesis and generation options available for the design. Shown in Figure 11, the user can specify the compilation target, the type of generation, and various design constraints. The Part menu allows selection of the FPGA on which the design is to be implemented with additional options for speed grade and pinout of the device. The Compilation menu allows the designer to select the output type. HDL Netlist outputs a VHDL or Verilog file along with a pre-populated Xilinx ISE project file, which was the output type used for this research. Other options available are the NGC Netlist wrapper file, which is the Xilinx proprietary format analogous to the industry standard electronic data interchange format (EDIF), compilation directly to bitstream for direct implementation on an FPGA, and hardware cosimulation [19], [20].

Hardware cosimulation uses a JTAG-configurable target device to load the generated bitcode of the current System Generator model to speed simulation and provide a check on whether the hardware implementation of the design matches the software simulation. Under the hardware cosimulation option in the Compilation menu is a list of all devices for which hardware cosimulation is supported. Instructions for adding the XUP development board are given in [21]. Generation produces a single System Generator block with inputs and outputs corresponding to the GATEWAY IN and GATEWAY OUT blocks of the source design. When the model is simulated, the new

block causes System Generator to connect to the target device through the selected JTAG interface, upload the bitfile to the FPGA, insert the input waveforms, and read the output waveforms.

Figure 11. System Generator Options.

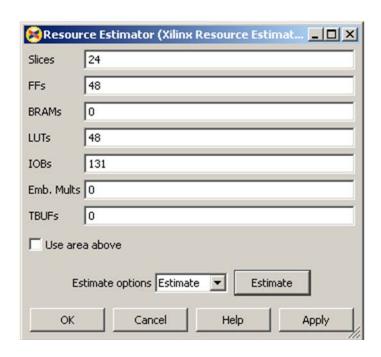

Another useful feature of System Generator is its ability to estimate the resources required to implement the design. The Resource Estimator block, shown in Figure 12, can be placed into the System Generator design to compile an estimate of the number of slices and other embedded logic resources required to implement the design. This function is useful for the designer to get an early estimate of the logic resources required

for the design; however, the estimator is somewhat device agnostic. Conflicts in logic allocations can arise that make a design require more logic resources than the estimator indicates [20].

Figure 12. System Generator Resource Estimator.

Another feature of System Generator used in this design was the HDL Testbench generation feature. As noted in [19] when this option is selected, in addition to the usual files, System Generator also produces a file <design>\_tb.vhd, as well as data vectors and scripts which ModelSim uses for HDL simulation. The data vectors are produced using the data passed from Simulink® to System Generator through the GATEWAY IN blocks.

# C. XILINX ISE

Xilinx ISE is the integrated development environment for developing applications for Xilinx FPGAs. Although in Xilinx ISE the designer has the option to start a FPGA design project from scratch, System Generator includes a pre-configured ISE project file among the generated files, named <design>\_cw.ise. This is the starting point for modifying the design in ISE after generation with System Generator. [6]

The primary use of Xilinx ISE for this design was synthesizing the design to determine actual logic resource utilization of the various designs. Xilinx ISE was also used as the interface with ModelSim for behavioral simulation of the design as well as generating the bitstream, which contains the configuration information for the target FPGA, for hardware implementation [6].

### D. MODELSIM

ModelSim, by Mentor Graphics, is a simulation environment for testing the functional behavior of an application in HDL. It is a separate program from Xilinx ISE that provides an alternate environment for testing and verifying the behavior of HDL designs. The simulation passes stimuli into the HDL file and displays the output. It is also possible to script the input / output process to speed the simulation process as well as increase testing flexibility [22].

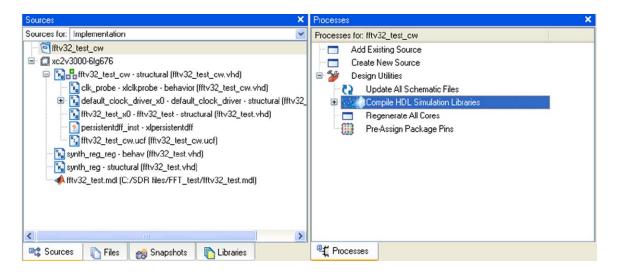

In order to use ModelSim with Xilinx ISE, the Xilinx HDL simulation libraries must be compiled. This can be performed using a command line argument, as discussed in [5], or it can be done using menu options. On the left side of the screen, under "Sources," select the top-level file for the project. Under "Processes," expand the "Design Utilities" option and double-click "Compile HDL Simulation Libraries." These menu options are shown in Figure 13. If the libraries were compiled during installation, the user does not need to complete this step.

Figure 13. Compile HDL Simulation Libraries.

ModelSim uses Tool Control Language (TCL) based testbench files to control stimulus into the design under test. The System Generator option to automatically generate these testbench files was the primary method used to create the input waveforms for the model. Another option, described in [22], is to use the Waveform Editor to generate stimulus signals.

### E. XILINX CHIPSCOPE PRO

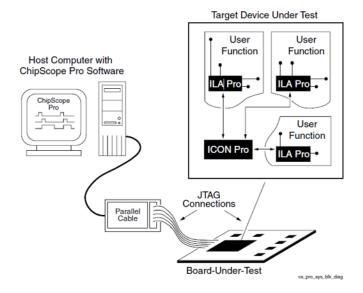

Xilinx ChipScope Pro is a software package that works with Xilinx FPGAs and CPLDs to conduct hardware level test and debugging. As described in [23], ChipScope consists of three main components: the Xilinx CORE Generator<sup>TM</sup> tool, the core inserter, and the analyzer. The ICON (interface control) core controls the logic analyzer cores and provides a communications path to the JTAG boundary scan port. The integrated logic analyzer (ILA) core is used to monitor and analyze logic within the chip. The virtual input / output (VIO) core provides access to internal FPGA signals without requiring on-chip RAM. The relationship between the cores, the device under test, and the analyzer software is illustrated in Figure 14.

Figure 14. ChipScope Pro Block Diagram (From [23]).

ChipScope Cores are inserted into a design, providing access to in-chip signals. With System Generator, inserting cores is as simple as including the appropriate ChipScope block in the design. The limitation to this method is that only one ChipScope Core can be inserted in this manner, and it cannot be used at the same time as JTAG hardware co-simulation, which is discussed in the next section [19]. ChipScope Cores can also be generated with the CORE Generator and included in HDL source files from within Xilinx ISE. Finally, cores can be inserted into a finished design using the ChipScope Pro Core Inserter tool [23].

ChipScope Analyzer is two pieces of software used to interact with the inserted cores when the design is implemented in hardware. The server is a command line application that connects to the target device via JTAG. It is run automatically if the target device is connected to the local computer, which is the method used for this research. It is also possible to use the server application to connect to a target device over a network. The client application is the graphical user interface (GUI) used to debug the design on the target device. It is used to set data collection triggers and to display collected waveforms [23].

## F. XILINX XUP VIRTEXTM-II PRO DEVELOPMENT BOARD

The Xilinx XUP (Xilinx University Program) Virtex<sup>TM</sup>-II Pro development board, shown in Figure 15, was used as the hardware target during this design process. It was used during two parts of the design process: first, during System Generator design with the hardware cosimulation option, and second after design implementation with Xilinx ISE with the hardware implementation of the bitcode [19], [21].