**Calhoun: The NPS Institutional Archive**

**DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2014-03

# A systematic software, firmware, and hardware codesign methodology for digital signal processing

Chang, Daniel Y.

Monterey, California: Naval Postgraduate School

http://hdl.handle.net/10945/41358

Downloaded from NPS Archive: Calhoun

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NAVAL POSTGRADUATE SCHOOL

MONTEREY, CALIFORNIA

# **DISSERTATION**

#### A SYSTEMATIC SOFTWARE, FIRMWARE, AND HARDWARE CODESIGN METHODOLOGY FOR DIGITAL SIGNAL PROCESSING

by

Daniel Y. Chang

March 2014

Dissertation Supervisor:

Neil C. Rowe

Approved for public release; distribution is unlimited

#### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington DC 20503.

| 1. AGENCY USE ONLY (Leave blank)                                                                            | 2. REPORT DATE  March 2014 | 3. REPO | RT TYPE AND DATES COVERED  Dissertation             |

|-------------------------------------------------------------------------------------------------------------|----------------------------|---------|-----------------------------------------------------|

| <b>4. TITLE AND SUBTITLE:</b> A SYSTEM HARDWARE CODESIGN METHODOLO PROCESSING                               | 5. FUNDING NUMBERS         |         |                                                     |

| 6. AUTHOR(S) Daniel Y. Chang                                                                                |                            |         |                                                     |

| 7. PERFORMING ORGANIZATION NA<br>Naval Postgraduate School<br>Monterey, CA 93943-5000                       | AME(S) AND ADDRESS(ES)     |         | 8. PERFORMING<br>ORGANIZATION REPORT<br>NUMBER      |

| 9. SPONSORING / MONITORING AGI<br>ECSEL/JEWEL, NAWCWD<br>575 I Avenue, Suite 1<br>Point Mugu, CA 93042-5049 | ENCY NAME(S) AND ADDR      | ESS(ES) | 10. SPONSORING / MONITORING<br>AGENCY REPORT NUMBER |

11. SUPPLEMENTARY NOTES The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government. IRB protocol number N/A

# **12a. DISTRIBUTION / AVAILABILITY STATEMENT** Approved for public release; distribution is unlimited

12b. DISTRIBUTION CODE

Α

#### 13. ABSTRACT (maximum 200 words)

Creating an embedded system that meets its functional, performance, cost, and schedule goals is a software-and-hardware codesign problem, since the design of the software and hardware components influence each other. The traditional design methodology is sequential, with hardware designed first and then software. The lack of a unified and unbiased approach can lead to suboptimal design and incompatibilities across the software and hardware boundary.

To solve these problems, we propose a new software/firmware/hardware codesign methodology to systematically build correct designs efficiently. This codesign methodology includes requirements development, architecture forming, software/ firmware/hardware partitioning, design-pattern mapping, new-design pattern synthesis, integration, and testing.

We tested our methods on three application areas. One was a digitizer-filter architecture for ultra-high frequency signals for which we synthesized design patterns in firmware to meet high-frequency requirements. Another was a digitizer-filter architecture for low-frequency signals. A third was a hidden Markov model using dynamic programming. We implemented and tested the first application on a Tektronix/Synopsys embedded system and the second on a Pentek embedded system based on the requirements provided by the stakeholders

| <b>14. SUBJECT TERMS</b> A*, AN digital signal processing, design FPGA, OR tree, hidden Marko | PAGES                                          |                                               |                               |

|-----------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------|-------------------------------|

| remapping, pre-serialization bits re                                                          | 16. PRICE CODE                                 |                                               |                               |

| 17. SECURITY<br>CLASSIFICATION OF<br>REPORT                                                   | 18. SECURITY<br>CLASSIFICATION OF THIS<br>PAGE | 19. SECURITY<br>CLASSIFICATION OF<br>ABSTRACT | 20. LIMITATION<br>OF ABSTRACT |

| Unclassified                                                                                  | Unclassified                                   | Unclassified                                  | UU                            |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

#### Approved for public release; distribution is unlimited

# A SYSTEMATIC SOFTWARE, FIRMWARE, AND HARDWARE CODESIGN METHODOLOGY FOR DIGITAL SIGNAL PROCESSING

Daniel Y. Chang Civilian, Naval Air Warfare Center, Weapons Division B.S., Fu-Jen Catholic University, 1979 M.S.E.E, California State University, Northridge, 1992

Submitted in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY IN SOFTWARE ENGINEERING

from the

#### NAVAL POSTGRADUATE SCHOOL March 2014

| Author:      |                                         |                           |

|--------------|-----------------------------------------|---------------------------|

|              | Daniel Y. Chang                         |                           |

| Approved by: |                                         |                           |

|              | Neil C. Rowe                            |                           |

|              | Professor of Computer Science           |                           |

|              | Dissertation Supervisor, Dissertation G | Committee Chair           |

|              | 1                                       |                           |

|              | National Assessment                     | M T1. C1                  |

|              | Mikhail Auguston                        | Man-Tak Shing             |

|              | Associate Professor                     | Associate Professor       |

|              | of Computer Science                     | of Computer Science       |

|              | Roberto Cristi                          | Melissa Midzor            |

|              | Professor of Electrical Engineering     | JEWEL, NAWCWD             |

| Annewad ha   |                                         |                           |

| Approved by: | Peter J. Denning, Chair, Depar          | tment of Computer Science |

|              |                                         |                           |

| Approved by: |                                         |                           |

|              | Douglas Moses, Vice Prove               | ost for Academic Affairs  |

#### **ABSTRACT**

Creating an embedded system that meets its functional, performance, cost, and schedule goals is a software-and-hardware codesign problem, since the design of the software and hardware components influence each other. The traditional design methodology is sequential, with hardware designed first and then software. The lack of a unified and unbiased approach can lead to suboptimal design and incompatibilities across the software and hardware boundary.

To solve these problems, we propose a new software/firmware/hardware codesign methodology to systematically build correct designs efficiently. This codesign methodology includes requirements development, architecture forming, software/firmware/hardware partitioning, design-pattern mapping, new-design pattern synthesis, integration, and testing.

We tested our methods on three application areas. One was a digitizer-filter architecture for ultra-high frequency signals for which we synthesized design patterns in firmware to meet high-frequency requirements. Another was a digitizer-filter architecture for low-frequency signals. A third was a hidden Markov model using dynamic programming. We implemented and tested the first application on a Tektronix/Synopsys embedded system and the second on a Pentek embedded system based on the requirements provided by the stakeholders.

## TABLE OF CONTENTS

| I.  | INT       | RODUCTION AND PROBLEM ADDRESSED                             | 1               |

|-----|-----------|-------------------------------------------------------------|-----------------|

|     | Α.        | ADDRESSED PROBLEM                                           |                 |

|     | В.        | MOTIVATION                                                  |                 |

|     | C.        | CLAIM                                                       |                 |

|     | D.        | TRADITIONAL METHODOLOGY FOR DSP DESIGN                      |                 |

|     | <b>E.</b> | OUR SOFTWARE ENGINEERING METHODOLOGY                        |                 |

|     | F.        | TOPICS COVERED FROM CHAPTERS II TO VIII                     |                 |

| II. | DDF       | VIOUS WORK                                                  | 7               |

| 11. | A.        | REQUIREMENTS ENGINEERING                                    | ···· /          |

|     | A.        | 1. Requirements Development                                 |                 |

|     |           | 2. Rational Unified Process                                 | /               |

|     |           | 3. Design-Based Requirements                                |                 |

|     |           | 4. Test-Based Requirements                                  |                 |

|     |           | 5. Agile Software Development                               |                 |

|     |           | 6. Model-Driven Requirements Engineering                    |                 |

|     |           | 7. Model-Driven Development                                 |                 |

|     |           | 8. Domain-Specific Modeling and Language                    |                 |

|     | В.        | SOFTWARE ENGINEERING OF EMBEDDED SYSTEMS                    |                 |

|     | в.<br>С.  | CONCURRENT SOFTWARE ENGINEERING OF EMBEDDED                 | •11             |

|     | C.        | SYSTEMS                                                     | 12              |

|     |           | 1. A Top-down Concurrent Design Process for an Embedded     |                 |

|     |           | System                                                      |                 |

|     |           | 2. POLIS.                                                   |                 |

|     |           | 3. Orthogonalization of Concerns and Platform-Based Design  |                 |

|     |           | 4. The Double Roof Model of Codesign, a System Level Design |                 |

|     |           | 5. Integrated Chip Codesign                                 |                 |

|     | D.        | FPGA DESIGN METHODOLOGY                                     |                 |

|     | D.        | 1. FPGA and Central Processing Unit                         |                 |

|     |           | 2. FPGA and Hardware Description Language                   |                 |

|     |           | 3. FPGA Programming                                         |                 |

|     |           | 4. HDL is Object-Based not Object-Oriented                  |                 |

|     |           | 5. Two Primary Hardware Description Languages—VHDL and      |                 |

|     |           | Verilog                                                     |                 |

|     |           | 6. FPGA Design Methodology—HDL Approach                     |                 |

|     | <b>E.</b> | DESIGN PATTERNS                                             |                 |

|     | L.        | 1. Software Design Patterns                                 |                 |

|     |           | 2. Embedded Software Design Patterns                        |                 |

|     |           | a. CPU-Based Firmware Design Patterns                       |                 |

|     |           | b. Reconfigurable Computing Based Design Patterns           |                 |

|     |           | 3. Hardware Components Selection                            |                 |

|     | F         | A* AND ΔO* ALCORITHMS                                       | 30<br><b>37</b> |

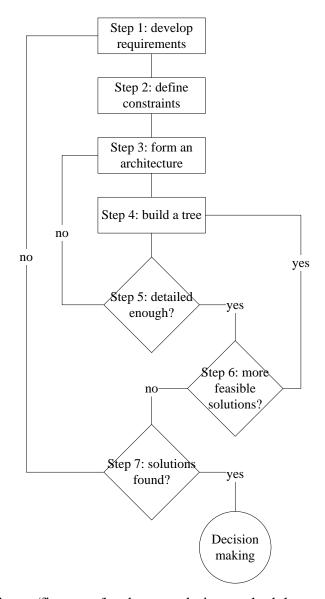

| III.  | MET       | <b>CHODO</b> | OLOGY                                                      | 39 |

|-------|-----------|--------------|------------------------------------------------------------|----|

|       | <b>A.</b> | SW/          | FW/HW PARTITIONING METHODOLOGY                             | 39 |

|       |           | 1.           | Develop Requirements                                       | 39 |

|       |           | 2.           | Define Constraints                                         |    |

|       |           | 3.           | Form an Architecture                                       |    |

|       |           |              | a. Consider Design Options                                 |    |

|       |           |              | b. Form an Architecture for the Optimal Option             |    |

|       |           |              | c. Simplify Architecture for Partitioning Analysis         |    |

|       |           | 4.           | Build a Tree to Assign Modalities to Functional Components |    |

|       |           |              | a. Software, Firmware and Hardware Partitioning            |    |

|       |           |              | b. Design Patterns Mapping                                 |    |

|       |           |              | c. Rate the Cost                                           |    |

|       |           | <b>5.</b>    | Repeat Steps 3 through 5                                   |    |

|       |           | 6.           | Repeat Steps 4 through 6                                   |    |

|       |           | 7.           | Repeat Steps 1 through 7                                   |    |

|       | В.        | EXA          | MPLE—FILTERING FOR ULTRA-HIGH FREQUENCY                    |    |

|       |           | SIG          | NALS                                                       | 44 |

|       |           | 1.           | Develop Requirements                                       | 44 |

|       |           | 2.           | Define Constraints                                         |    |

|       |           | 3.           | Form an Architecture                                       | 45 |

|       |           |              | a. Consider Design Options                                 | 45 |

|       |           |              | b. Form an Architecture for the Optimal Option             | 47 |

|       |           |              | c. Simplify Architecture for Partitioning Analysis         | 47 |

|       |           | 4.           | Build a Tree to Map Functions to Modalities                | 47 |

|       |           |              | a. Map to Software/Firmware/Hardware                       | 47 |

|       |           |              | b. Map to Design Patterns                                  |    |

|       | C.        |              | MPLE—FILTERING FOR LOW FREQUENCY SIGNALS                   |    |

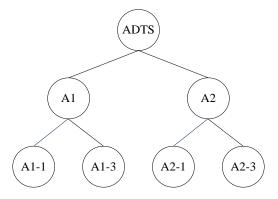

|       | D.        | EXA          | MPLE—AIR DATA TEST SET                                     |    |

|       |           | 1.           | Option 1 (A1-1)                                            |    |

|       |           | 2.           | Option 2 (A1-3)                                            |    |

|       |           | 3.           | Option 3 (A2-1)                                            |    |

|       |           | 4.           | Option 4 (A2-3)                                            |    |

|       | <b>E.</b> | A TO         | OOL FOR SW/FW/HW CODESIGN                                  | 70 |

| IV.   | REC       | CONFIC       | GURABLE COMPUTING DESIGN PATTERNS                          | 73 |

| _ , , | <b>A.</b> |              | YPHASE DFT FILTER BANKS                                    |    |

|       | 1.4       | 1.           | Name and Classification                                    |    |

|       |           | 2.           | Intent                                                     |    |

|       |           | 3.           | Motivation                                                 |    |

|       |           | 4.           | Applicability                                              |    |

|       |           | 5.           | Participants                                               |    |

|       |           | 6.           | Collaborations                                             |    |

|       |           | 7.           | Consequences (Benefits)                                    |    |

|       |           | 8.           | Implementation                                             |    |

|       |           | 9.           | Algorithm                                                  |    |

|       |           | 10.          | Known Uses (Examples)                                      |    |

|       |           |              |                                                            |    |

|           |            | a. Example 1                                | 76     |

|-----------|------------|---------------------------------------------|--------|

|           |            | b. Example 2                                |        |

|           | 11.        | Related Patterns                            | 78     |

| В.        | DAT        | A ALIGNMENT DESIGN PATTERN                  | 78     |

|           | 1.         | Name and Classification                     | 78     |

|           | 2.         | Intent                                      |        |

|           | 3.         | Motivation                                  |        |

|           | 4.         | Applicability                               |        |

|           | 5.         | Participants                                |        |

|           | 6.         | Collaborations                              |        |

|           | 7.         | Consequences                                |        |

|           | 8.         | Implementation                              |        |

|           | 9.         | Algorithm                                   |        |

|           |            | a. Bit-Alignment                            |        |

|           |            | b. Byte-Alignment                           |        |

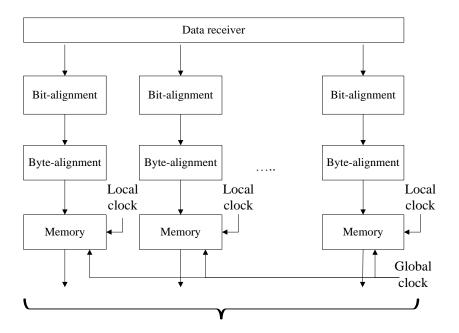

|           |            | c. Overall Alignment                        |        |

|           | 10.        | Known Uses (Examples)                       |        |

|           | 11.        | Related Patterns                            |        |

| C.        |            | Γ-DESERIALIZATION BITS REMAPPING DESIGN     | ••••ОТ |

| <b>C.</b> |            | ΓERN                                        | 84     |

|           | 1.         | Name and Category                           |        |

|           | 2.         | Intent                                      |        |

|           | 3.         | Motivation                                  |        |

|           | <b>4.</b>  | Applicability                               |        |

|           | 5.         | Participants                                |        |

|           | <b>6.</b>  | Collaborations                              |        |

|           | 7.         | Consequences                                |        |

|           | 8.         | Implementation                              |        |

|           | 9.         | Algorithm                                   |        |

|           | 9.<br>10.  | Known Uses (Examples)                       |        |

|           | 10.<br>11. | Related Patterns                            |        |

| D.        |            | SERIALIZATION BITS REMAPPING DESIGN PATTERN |        |

| υ.        | PKE-       | Name and Classification                     |        |

|           | 1.         |                                             |        |

|           | 2.         | Intent                                      |        |

|           | 3.         | Motivation                                  |        |

|           | <b>4.</b>  | Applicability                               |        |

|           | 5.         | Participants                                |        |

|           | <b>6.</b>  | Collaboration                               |        |

|           | 7.         | Consequences                                |        |

|           | 8.         | Implementation                              |        |

|           | 9.         | Algorithm                                   |        |

|           | 10.        | Known Uses (Examples)                       |        |

| -         | 11.        | Related Patterns                            |        |

| <b>E.</b> |            | TCH-AND-FILTER ARCHITECTURE                 |        |

|           | 1.         | Name and Classification                     | 92     |

|      |     | 2.        | Intent                                                   | 93  |

|------|-----|-----------|----------------------------------------------------------|-----|

|      |     | 3.        | Motivation                                               | 93  |

|      |     | 4.        | Applicability                                            | 93  |

|      |     | 5.        | Participants                                             | 93  |

|      |     | 6.        | Collaborations                                           | 93  |

|      |     | 7.        | Consequences                                             | 95  |

|      |     | 8.        | Implementation                                           |     |

|      |     | 9.        | Known Uses (Examples)                                    |     |

|      |     | 10.       | Related Patterns                                         | 97  |

| V.   | CAS | E STUI    | DY ONE                                                   | 99  |

|      | A.  | MET       | THODOLOGY                                                | 99  |

|      |     | 1.        | Develop Requirements and Define Constraints              | 99  |

|      |     | 2.        | Form an Architecture                                     |     |

|      |     | 3.        | Build a Tree to Map Functions to Modalities              |     |

|      |     | 4.        | Implementation                                           |     |

|      | В.  |           | A SOFTWARE TEST METHODOLOGY                              |     |

|      | C.  |           | T RESULTS                                                |     |

|      |     | 1.        | Setup                                                    |     |

|      |     |           | a. ADC/FPGA/DAC Specifications                           |     |

|      |     | _         | b. Equipment                                             |     |

|      |     | 2.        | Test Specifications                                      |     |

|      |     |           | a. Alignment Tests                                       |     |

|      |     |           | b. Harmonics Tests                                       |     |

|      |     |           | c. Flatness Tests                                        |     |

|      |     |           | d. Linearity Tests                                       |     |

|      |     |           | e. Noise Floor Tests                                     |     |

|      |     |           | f. Sensitivity Testsg. Test with JEWEL RF Jamming Device |     |

|      |     | 3.        | g. Test with JEWEL RF Jamming Device Functional Tests    |     |

|      |     | 3.        | a. Data in the FPGA                                      |     |

|      |     |           | b. Comparison between Analog-to-digital Converter        |     |

|      |     |           | FPGA Data                                                |     |

|      |     |           | c. Tests without Proper Alignment Software               | 109 |

|      |     |           | d. Tests with Proper Alignment Software                  |     |

|      |     | 4.        | Performance Tests                                        |     |

|      |     |           | a. Flatness Test                                         |     |

|      |     |           | b. Linearity Test (500 MHz, RBW=3 MHz)                   |     |

|      |     |           | c. Noise Floor Test                                      |     |

|      |     |           | d. Sensitivity Test                                      | 113 |

|      |     | <b>5.</b> | Validate with an Existing JEWEL RF Jamming Device        | 114 |

|      | D.  | TEST      | TS CONCLUSION                                            |     |

| VI.  | CAS | E STIII   | DY TWO                                                   | 117 |

| 1 1. | A.  |           | THODOLOGY                                                |     |

|      | 4.4 | 1.        | Develop Requirements and Define Constraints              |     |

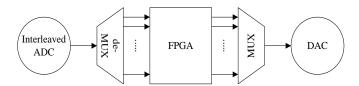

|      |     | 2.        | Form an Architecture                                     |     |

|      |     | -         |                                                          |     |

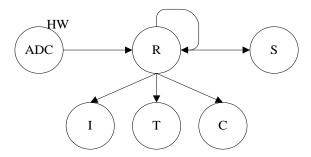

|       |            | 3. Build a Tree to Map Functions to Modalities            | .119 |

|-------|------------|-----------------------------------------------------------|------|

|       |            | 4. Reusable Assets                                        |      |

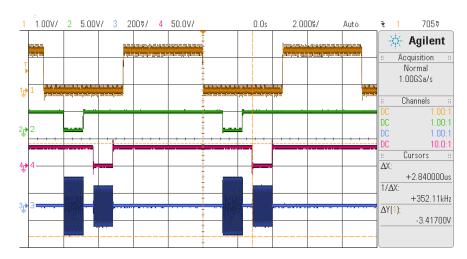

|       | В.         | TESTS                                                     | .127 |

|       |            | 1. Purpose of Our Tests                                   | .127 |

|       |            | 2. Test Specifications                                    |      |

|       |            | 3. Pentek Software IP Cores                               |      |

|       |            | 4. Tests Configurations, Methodology and Results          | .128 |

|       |            | a. Signals and IP Cores Configurations                    | .128 |

|       |            | b. Methodology (Software Program in C Programming         | 3    |

|       |            | Language)                                                 | .130 |

|       |            | c. Test Results                                           | .131 |

|       | <b>C.</b>  | TESTS CONCLUSION                                          | .133 |

| VII.  | CAS        | E STUDY THREE—HIDDEN MARKOV MODEL                         | 135  |

| V 11. | A.         | INTRODUCTION                                              |      |

|       | B.         | FORWARD ALGORITHM CASE STUDY                              |      |

|       | ъ.         | 1. Develop Requirements and Define Constraints            |      |

|       |            | 2. Form an Architecture                                   |      |

|       |            | 3. Build a Tree to Map Functions to Modalities            |      |

|       |            | 4. Discussion                                             |      |

|       | C.         | METHODOLOGY FOR VITERBI ALGORITHM                         |      |

|       |            |                                                           |      |

| VIII. |            | ICLUSION AND RECOMMENDATIONS FOR FUTURE RESEARCH          |      |

|       | <b>A.</b>  | OUR CLAIM                                                 |      |

|       | <b>B.</b>  | OUR CONTRIBUTIONS                                         |      |

|       | C.         | FUTURE RESEARCH DIRECTIONS                                | .144 |

| APPE  | ENDIX      | A. CASE STUDY ONE BACKGROUND                              | .147 |

|       | A.         | CHALLENGES WE ARE FACING                                  |      |

|       |            | 1. Background (Two-Ray Segment Propagation Model)         | .147 |

|       |            | 2. Using an Example to Illustrate the Challenges in Signa |      |

|       |            | Simulation                                                | .148 |

|       | В.         | HOW DO ADC/FPGA/DAC SYSTEMS SOLVE OUR PROBLEMS            | .152 |

| A DDE | ENDIX      | B. TEKTRONIX ADC/FPGA/DAC DEMO SYSTEM                     | 155  |

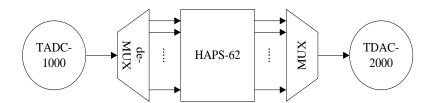

| AIII  | A.         | TADC-1000 DIGITIZER                                       |      |

|       | В.         | TIPA-3100 ADC INTERPOSER                                  |      |

|       | <b>С</b> . | HAPS-62-1 FPGA                                            |      |

|       | D.         | TIPD-3200 DAC INTERPOSER                                  |      |

|       | Б.<br>Е.   | TDAC-2000 DAC                                             |      |

|       |            |                                                           |      |

| APPE  | ENDIX      |                                                           |      |

|       | <b>A.</b>  | POLYPHASE DFT FILTER BANKS EXAMPLE 1                      |      |

|       | В.         | POLYPHASE DFT FILTER BANKS EXAMPLE 2                      | .162 |

| APPE  | ENDIX      |                                                           | .165 |

|       | A.         | SETUP TIME AND HOLD TIME REQUIREMENTS                     | .165 |

|       | B.         | INHERENT TIMING WINDOW                                    |      |

|       | C.         | DEMULTIPLEXER                                             |      |

| D.         | MULTIPLEXER                                     | 167 |

|------------|-------------------------------------------------|-----|

| APPENDIX   | E. DERIVATION OF POLYPHASE DFT FILTER BANKS     | 169 |

| <b>A.</b>  | POLYPHASE DFT FILTER BANKS REPRESENTATION IN Z- |     |

|            | DOMAIN                                          | 169 |

| В.         | POLYPHASE DECOMPOSITION                         | 171 |

| С.         | ANALYSIS POLYPHASE DFT FILTER BANKS WITH M      |     |

|            | FILTERS                                         | 171 |

| D.         | SYNTHESIS POLYPHASE DFT FILTER BANKS WITH M     |     |

|            | CHANNELS                                        | 174 |

| LIST OF RE | EFERENCES                                       | 175 |

| INITIAL DI | STRIBUTION LIST                                 | 183 |

## LIST OF FIGURES

| Figure 1  | Rational unified process lifecycle phases, milestones and iterations   | 9  |

|-----------|------------------------------------------------------------------------|----|

| Figure 2  | A top-down concurrent design process for an embedded system            | 14 |

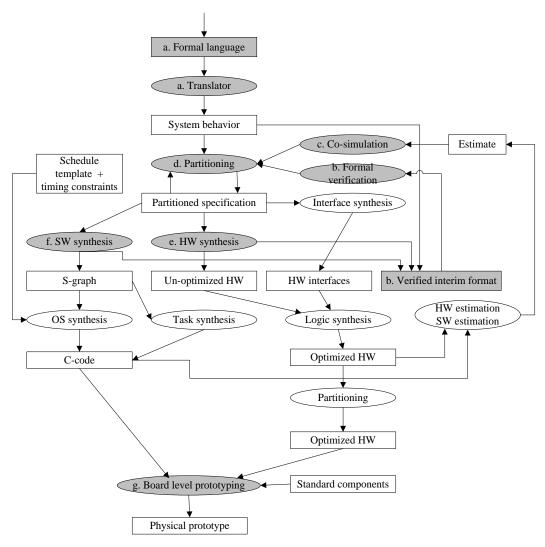

| Figure 3  | POLIS process                                                          | 16 |

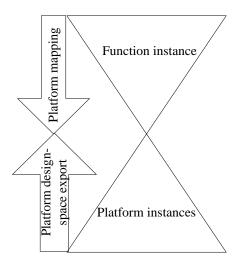

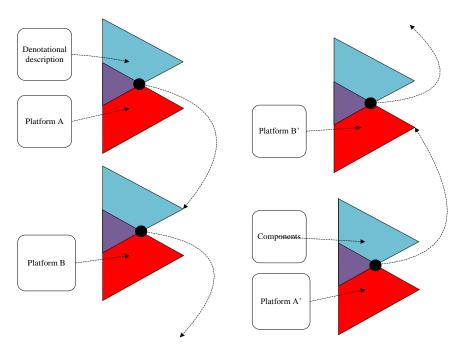

| Figure 4  | Platform-based design process                                          | 18 |

| Figure 5  | Platform-based design is iterative                                     | 19 |

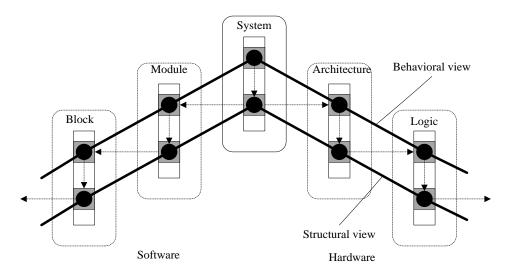

| Figure 6  | Double-roof model of codesign                                          | 20 |

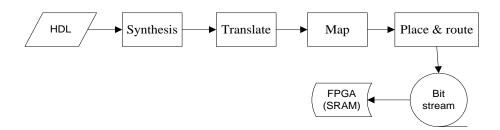

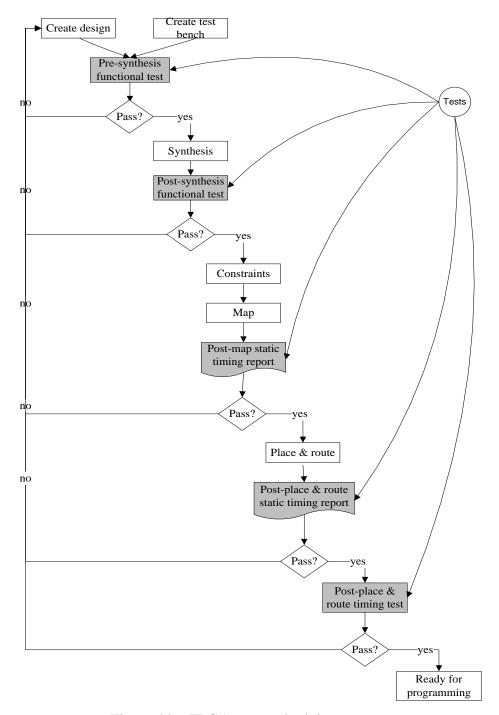

| Figure 7  | FPGA programming process                                               | 23 |

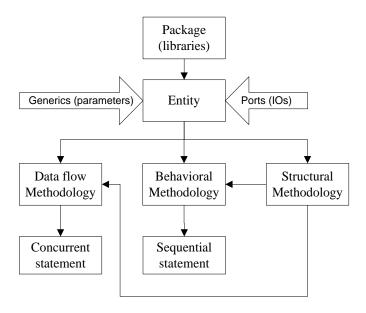

| Figure 8  | HDL hierarchy                                                          |    |

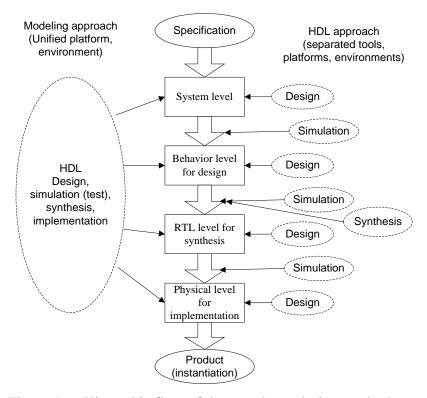

| Figure 9  | Hierarchic flow of the top–down design method                          | 29 |

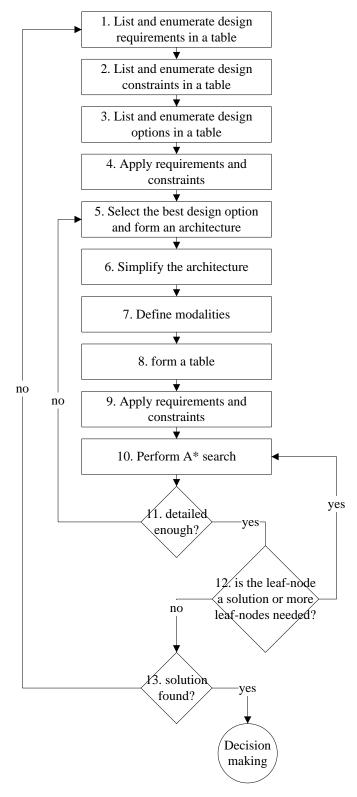

| Figure 10 | Software/firmware/hardware codesign methodology process flow           | 44 |

| Figure 11 | Five options for filtering                                             | 46 |

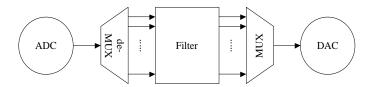

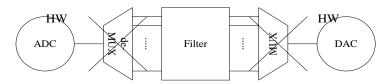

| Figure 12 | An architecture satisfying our requirements and constraints            | 47 |

| Figure 13 | Exclude ADC and DAC from analysis                                      | 47 |

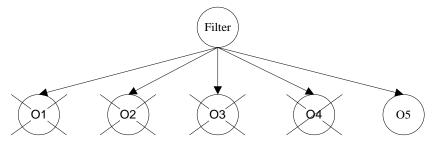

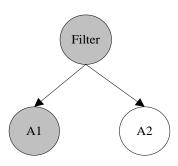

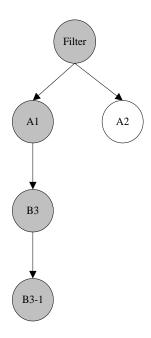

| Figure 14 | Four possible branches from the root                                   | 49 |

| Figure 15 | Four possible branches from the root in a simplified form              | 49 |

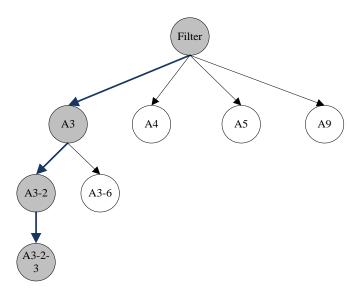

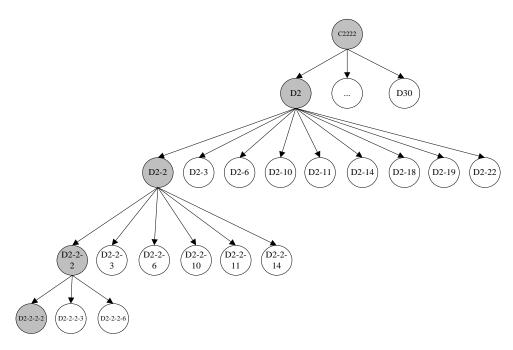

| Figure 16 | An OR tree for filtering of ultra-high frequency signals               | 50 |

| Figure 17 | Firmware components                                                    | 51 |

| Figure 18 | Only ATT and C are possible mappings                                   | 55 |

| Figure 19 | Only P is a possible mapping                                           | 57 |

| Figure 20 | Only DF, SD, and DP are possible mappings                              | 60 |

| Figure 21 | An architecture without parallelism                                    | 62 |

| Figure 22 | OR tree for low frequency signals                                      | 63 |

| Figure 23 | Optimal design pattern mapping                                         | 65 |

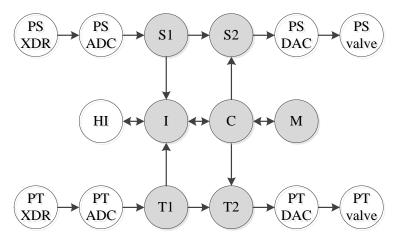

| Figure 24 | Air data test set architecture                                         | 66 |

| Figure 25 | A simplified architecture for analysis                                 | 67 |

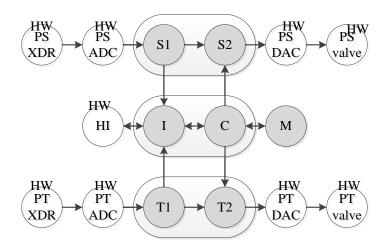

| Figure 26 | Four possible mappings                                                 | 68 |

| Figure 27 | Tool design flowchart                                                  | 72 |

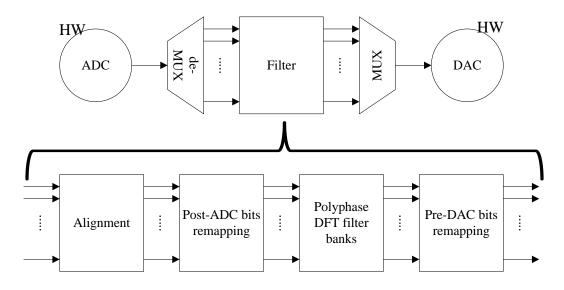

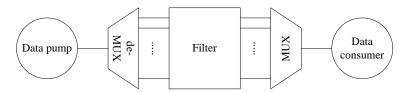

| Figure 28 | Typical components interfacing with polyphase DFT filter banks         | 74 |

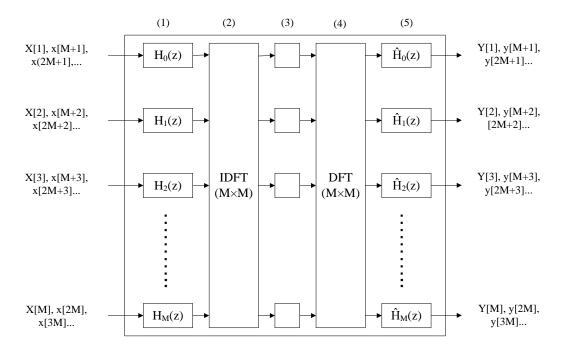

| Figure 29 | Polyphase DFT filter banks                                             | 75 |

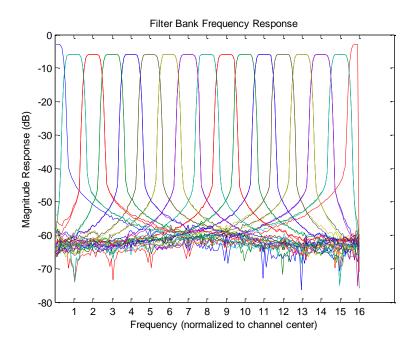

| Figure 30 | 16 magnitude responses of a polyphase DFT filter banks for real inputs | 77 |

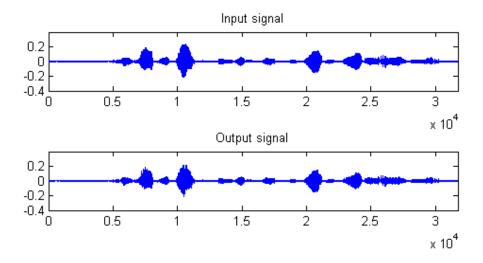

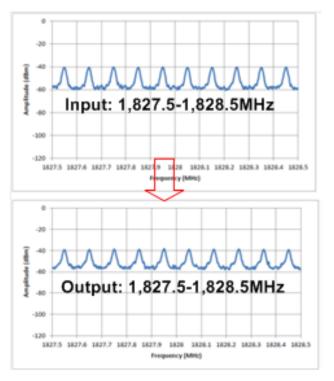

| Figure 31 | Signal before and after polyphase DFT filter banks                     |    |

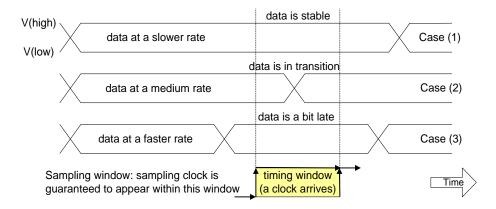

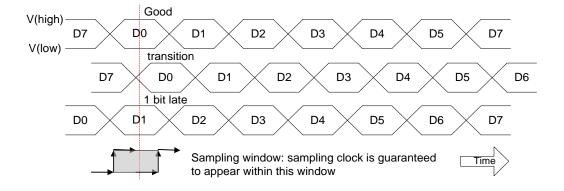

| Figure 32 | Shrinking of data window at higher data rate                           | 79 |

| Figure 33 | Three timing cases                                                     |    |

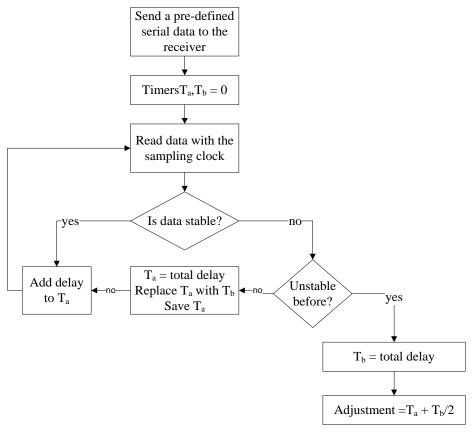

| Figure 34 | Bit-alignment flowchart                                                |    |

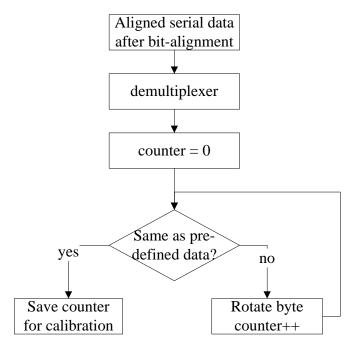

| Figure 35 | Byte-alignment flowchart                                               | 83 |

| Figure 36 | Overall-alignment flowchart                                            | 84 |

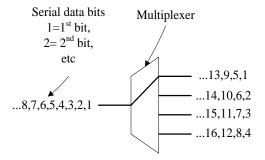

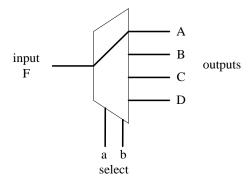

| Figure 37 | Level one demultiplexing                                               | 85 |

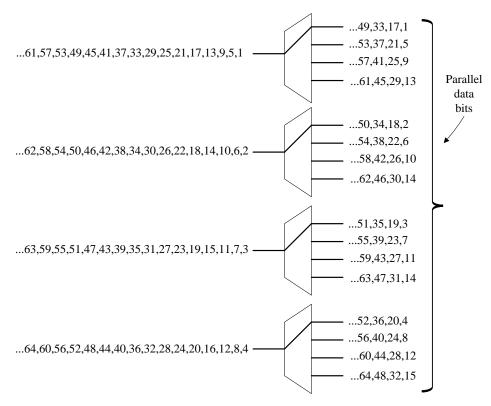

| Figure 38 | Level two demultiplexing                                               | 86 |

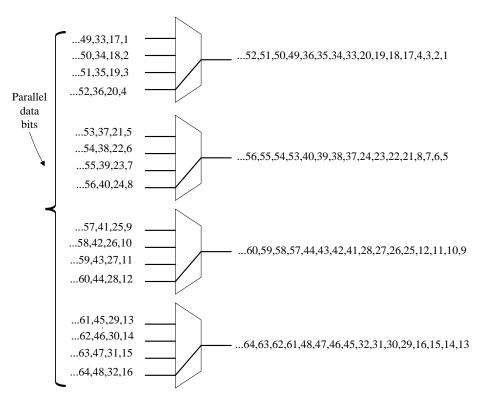

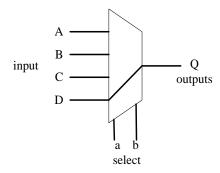

| Figure 39 | Level one multiplexing                                                 | 89 |

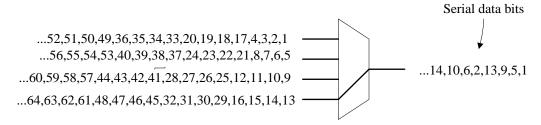

| Figure 40 | Level two multiplexing                                                 | 89 |

| Figure 41 | A switch-and-filter architecture                                       | 94 |

| Figure 42 | An instantiation of switch-and-filter architecture                     | 96 |

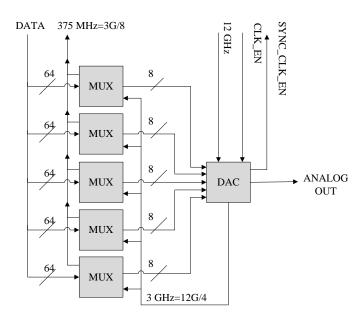

| Figure 43 | Architecture for ultra-wide instantaneous bandwidth signal processing | 100 |

|-----------|-----------------------------------------------------------------------|-----|

| Figure 44 | FPGA test methodology                                                 |     |

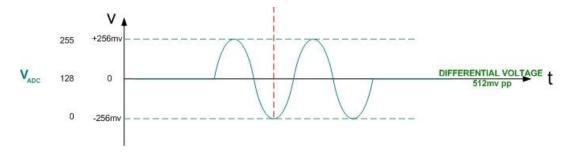

| Figure 45 | ADC input limits                                                      |     |

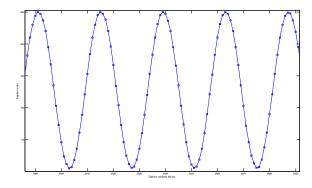

| Figure 46 | Digitized sinewave in the FPGA                                        | 108 |

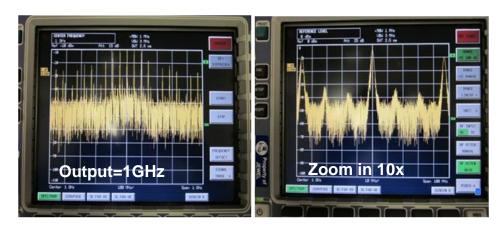

| Figure 47 | Tests without proper alignment software (in frequency domain)         | 110 |

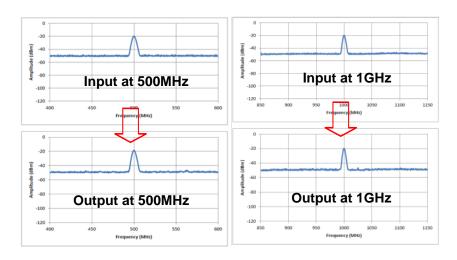

| Figure 48 | Signals at 500 MHz and 1 GHz; RBW=3 MHz                               | 110 |

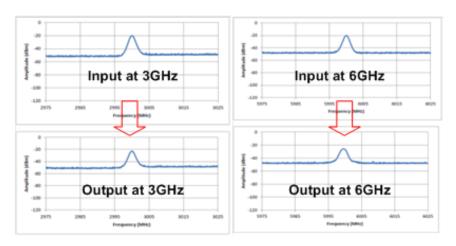

| Figure 49 | Signals at 3 GHz and 6 GHz, RBW=1 MHz                                 | 111 |

| Figure 50 | Sweeping, RBW=3 MHz; increment=10 MHz                                 | 112 |

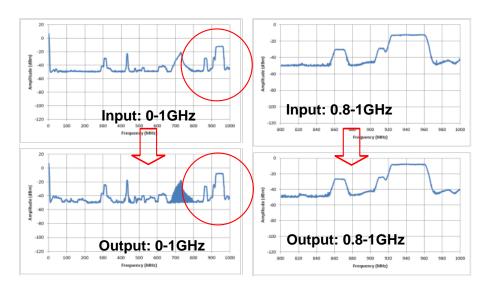

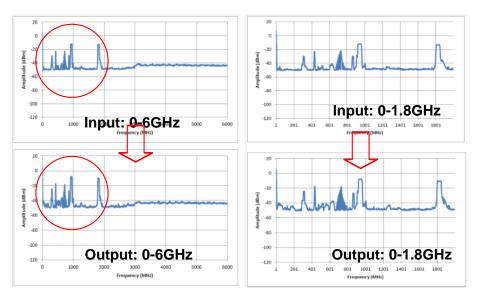

| Figure 51 | At bandwidths of 6 GHz and 1.8 GHz                                    | 114 |

| Figure 52 | At bandwidths of 1 GHz and 200 MHz                                    | 114 |

| Figure 53 | At bandwidth of 1 MHz                                                 | 115 |

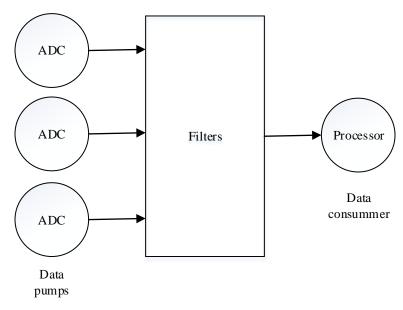

| Figure 54 | An architecture                                                       | 119 |

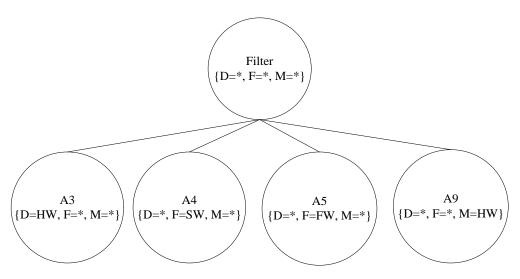

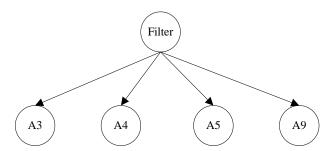

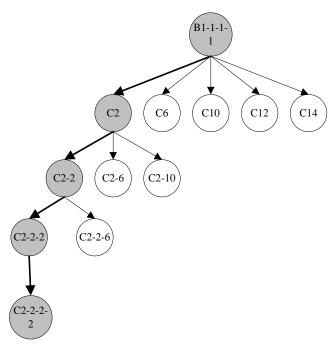

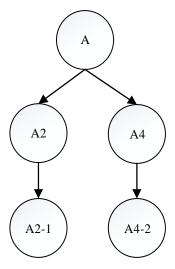

| Figure 55 | Node A2 (A4) is the only solution                                     | 121 |

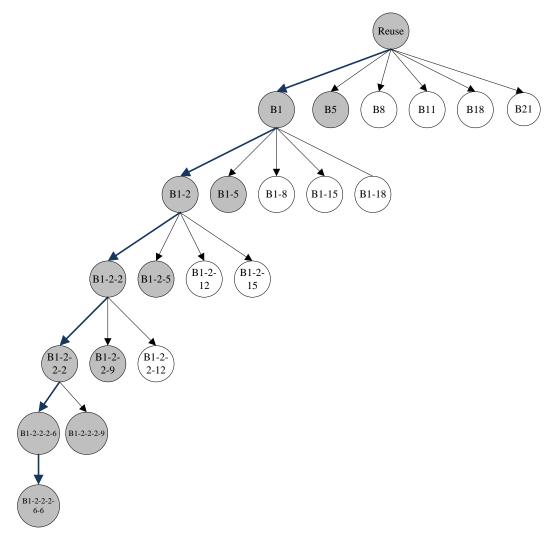

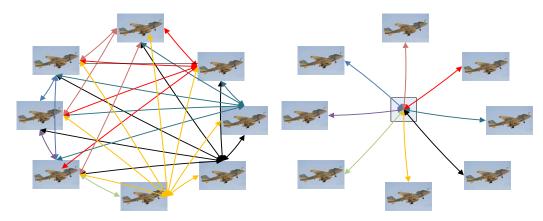

| Figure 56 | Reusable assets mappings                                              | 126 |

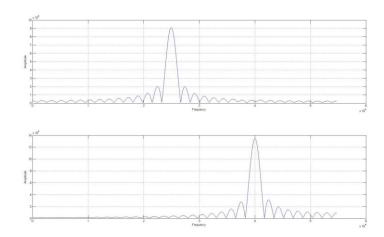

| Figure 57 | Two detected pseudo pulse Doppler target returns in a 2-D plot        | 131 |

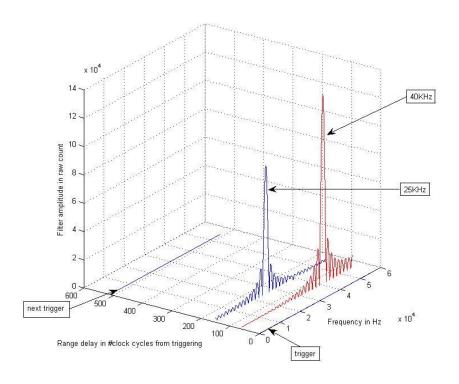

| Figure 58 | Two detected pseudo pulse Doppler target returns in a 3-D plot        | 132 |

| Figure 59 | Two input signals before detection                                    |     |

| Figure 60 | Hidden Markov model architecture                                      | 137 |

| Figure 61 | Two possible options                                                  | 141 |

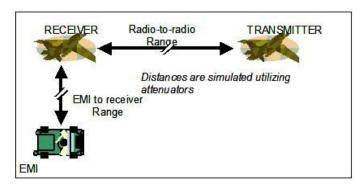

| Figure 62 | Distance is simulated by path loss                                    | 149 |

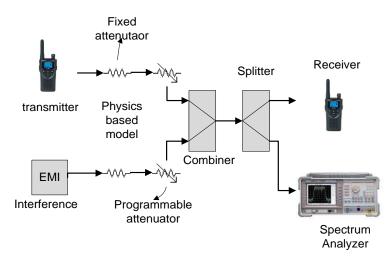

| Figure 63 | Simulation by using programmable attenuators                          |     |

| Figure 64 | N=4, N(analog)=12, N(digital)=8                                       | 151 |

| Figure 65 | N=8, N(analog)=56, N(digital)=16                                      | 151 |

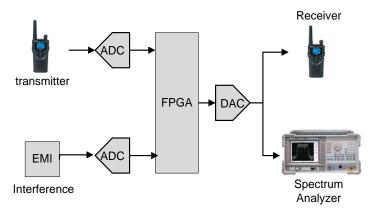

| Figure 66 | Simulation by using an ADC/FPGA/DAC system                            | 152 |

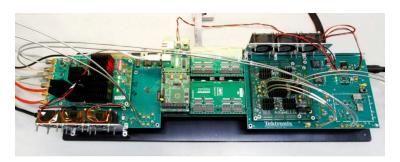

| Figure 67 | ADC/FPGA/DAC demo system                                              | 155 |

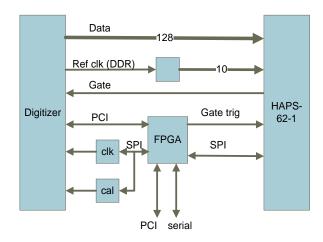

| Figure 68 | A simplified overall architecture for our case study                  | 155 |

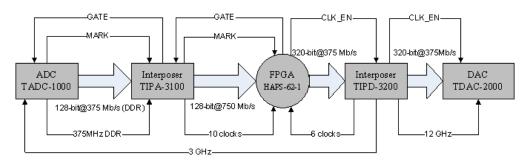

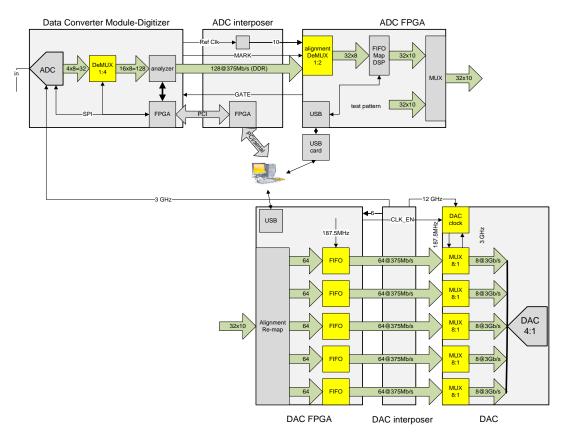

| Figure 69 | A detailed overall architecture for our case study                    | 156 |

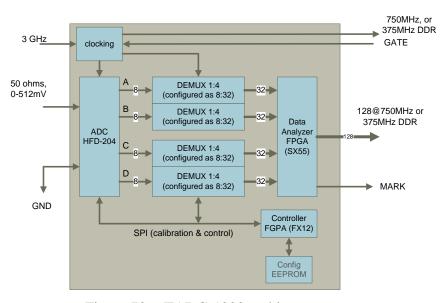

| Figure 70 | TADC-1000 architecture                                                | 157 |

| Figure 71 | TIPA-3100 architecture                                                | 158 |

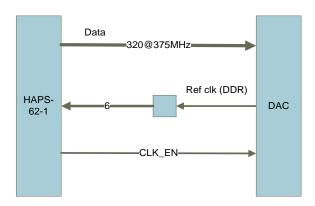

| Figure 72 | TIPD-3200 architecture                                                | 159 |

| Figure 73 | TDAC-2000 architecture                                                | 160 |

| Figure 74 | A one-to-four demultiplexer                                           | 166 |

| Figure 75 | A four-to-one multiplexer                                             | 167 |

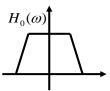

| Figure 76 | A single filter in frequency domain                                   |     |

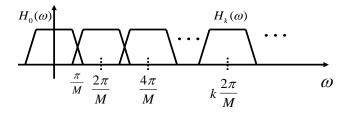

| Figure 77 | A filter bank of M filters spaced at $2\pi/M$ in the frequency domain |     |

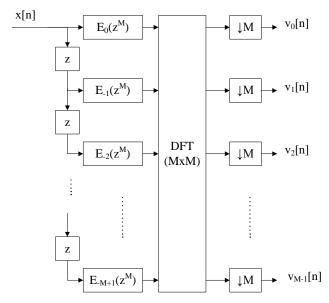

| Figure 78 | M-filter polyphase representation                                     |     |

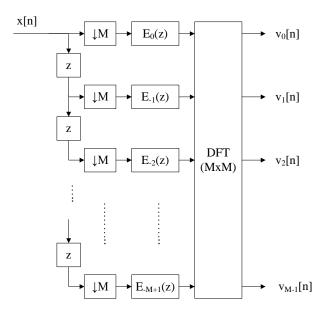

| Figure 79 | Apply Noble identity to polyphase representation                      |     |

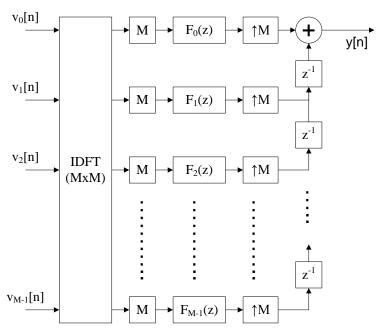

| Figure 80 | Synthesis network                                                     |     |

### LIST OF TABLES

| Table 1.  | Hardware description language features                         | 25 |

|-----------|----------------------------------------------------------------|----|

| Table 2.  | Some VHDL and Verilog construct differences                    |    |

| Table 3.  | Data flow method in Verilog                                    |    |

| Table 4.  | Behavior method in Verilog                                     | 27 |

| Table 5.  | FPGA design tools survey                                       | 30 |

| Table 6.  | Software design patterns                                       |    |

| Table 7.  | Design patterns for embedded systems                           | 33 |

| Table 8.  | Design patterns for reconfigurable computing                   |    |

| Table 9.  | Electronics component selection                                |    |

| Table 10. | A* algorithm                                                   |    |

| Table 11. | Least and most numbers of mappings                             |    |

| Table 12. | Functional requirements                                        |    |

| Table 13. | Non-functional constraints                                     |    |

| Table 14. | Five options for filtering                                     | 46 |

| Table 15. | Filter cost rating                                             |    |

| Table 16. | Nine options from the root                                     |    |

| Table 17. | Six mappings under A3                                          |    |

| Table 18. | Three mappings under A32                                       |    |

| Table 19. | Five classes                                                   |    |

| Table 20. | Only ATT and C are possible mappings                           | 54 |

| Table 21. | Four subclasses                                                |    |

| Table 22. | Only P is a possible mapping                                   |    |

| Table 23. | Eight purposes                                                 |    |

| Table 24. | Only DF, SD and DP are possible mappings                       |    |

| Table 25. | Possible optimal leaf-nodes                                    |    |

| Table 26. | New design patterns descriptions                               |    |

| Table 27. | Eliminate A3 from analysis                                     |    |

| Table 28. | Cost association                                               |    |

| Table 29. | Six major groups for CPU-based embedded system design patterns | 64 |

| Table 30. | Four subclasses design patterns for hardware interface         |    |

| Table 31. | Components descriptions                                        |    |

| Table 32. | A simplified table for analysis                                |    |

| Table 33. | Possible mappings for 2 components                             |    |

| Table 34. | Expand nodes A1 and A2                                         |    |

| Table 35. | Expand nodes A4 and A6                                         | 68 |

| Table 36. | Option 1                                                       | 69 |

| Table 37. | Option 2                                                       |    |

| Table 38. | Option 3                                                       |    |

| Table 39. | Option 4                                                       | 70 |

| Table 40. | VB6 program: post-deserialization bits remapping algorithm     | 87 |

| Table 41. | VB6 program: post-deserialization bits remap algorithm         |    |

| Table 42  | VR6 program: pre-serialization hits remapping algorithm        | 91 |

| Table 43. | VB6 program: pre-serialization bits remap algorithm           | 92  |

|-----------|---------------------------------------------------------------|-----|

| Table 44. | Data rate, throughput, and width calculation                  | 95  |

| Table 45. | Throughputs calculations                                      |     |

| Table 46. | FPGA process definitions                                      |     |

| Table 47. | Equipment models and serial numbers                           | 106 |

| Table 48. | Harmonics test specifications                                 | 106 |

| Table 49. | Flatness test specifications                                  | 107 |

| Table 50. | Noise floor test specifications                               | 107 |

| Table 51. | Sensitivity test specifications                               | 107 |

| Table 52. | The first 20 LFSR patterns                                    | 109 |

| Table 53. | Harmonics test specifications                                 | 111 |

| Table 54. | Flatness test specifications                                  | 112 |

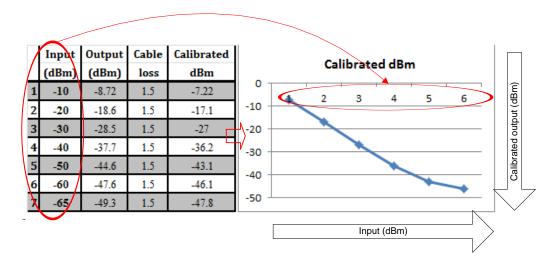

| Table 55. | Linearity test                                                | 113 |

| Table 56. | Noise floor test                                              | 113 |

| Table 57. | Sensitivity test                                              | 113 |

| Table 58. | Architectural components                                      | 119 |

| Table 59. | Node A                                                        | 120 |

| Table 60. | Node A2                                                       | 120 |

| Table 61. | Node A4                                                       | 120 |

| Table 62. | Vendors analysis                                              | 121 |

| Table 63. | Expanding node A2-1                                           | 123 |

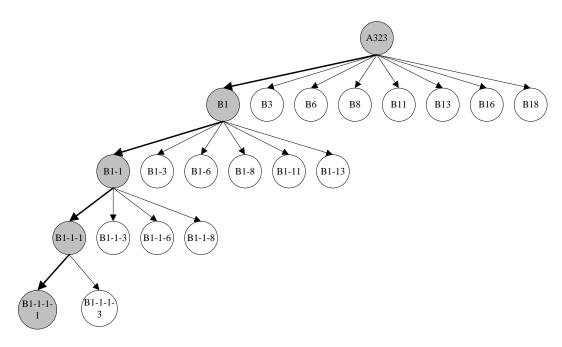

| Table 64. | Expanding node B1                                             | 124 |

| Table 65. | Expanding node B1-2                                           | 124 |

| Table 66. | Expanding node B1-2-2                                         | 125 |

| Table 67. | Expanding node B1-2-2-2                                       | 125 |

| Table 68. | Expanding node B1-2-2-6                                       | 125 |

| Table 69. | Map requirements to IP cores                                  | 127 |

| Table 70. | Map requirements to IP cores                                  | 127 |

| Table 71. | Pentek intellectual property cores                            | 128 |

| Table 72. | Input signal #1 characteristics                               | 129 |

| Table 73. | Input signal #2 characteristics                               | 129 |

| Table 74. | External trigger characteristics                              | 129 |

| Table 75. | DDC IP core configurations                                    | 130 |

| Table 76. | ADC IP core configurations                                    | 130 |

| Table 77. | Generated and captured Doppler shifts                         |     |

| Table 78. | Comparisons between with and without the SW/FW/HW methodology | 134 |

| Table 79. | Forward algorithm and Viterbi algorithm                       | 136 |

| Table 80. | Nodes A and A3                                                |     |

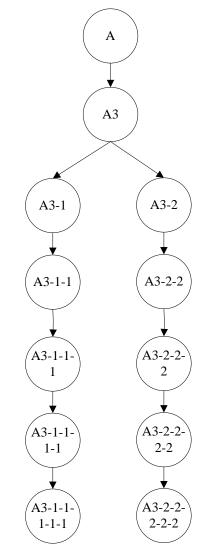

| Table 81. | Nodes A3-1, A3-1-1, A3-1-1-1 and A3-1-1-1-1                   | 139 |

| Table 82. | Nodes A3-2, A3-2-2, A3-2-2-2 and A3-2-2-2-2                   | 140 |

| Table 83. | Two options                                                   |     |

| Table 84. | Purpose and limitation of attenuators, combiners, splitters   |     |

| Table 85. | Analog and digital interconnections                           |     |

| Table 86. | Analog and digital power budget                               | 153 |

| Table 87. | Analog and digital time delays                                | 153 |

| Table 88. | XC6VLX760-1 resource                                              | 158 |

|-----------|-------------------------------------------------------------------|-----|

| Table 89. | MATLAB program: polyphase DFT analysis filter banks               | 162 |

| Table 90. | MATLAB program: polyphase DFT analysis and synthesis filter banks | 163 |

| Table 91. | Filter banks expressions                                          | 171 |

#### LIST OF ACRONYMS AND ABBREVIATIONS

A\* A star

ADC analog-to-digital converter

ADTS air data test set

AIRL Airborne Interceptor Research Laboratory

AO\* AO star

ASIC application-specific integrated circuit

CAD computer aided design

CFSM Codesign Finite-State Machine

COTS Commercial off-the-shelf

CPLD complex programmable logic device

DAC digital to analog converter

DCM data converter module

DFT discrete Fourier transform

DOD Department of Defense

DSL domain specific language

DSM domain specific modeling

DSP digital signal processing

EMI electromagnetic interference

ENOB effective number of bits

EP extreme programming

EW electronic warfare

FCC Federal Communications Commission

FFT fast Fourier transform

FIR finite impulse response

FPGA field programmable gate array

FSM finite state machine

GPU graphical processing unit

GSPS giga samples per second

GUI graphical user interface

HDL hardware description language

HMM hidden Markov model

HWIL hardware in the loop

IBW instantaneous bandwidth

IC integrated circuit

IF intermediate frequency

IQ in-phase quadrature

ISE Integrated Software Environment

JEWEL Joint Electronic Warfare Effects Laboratory

LOC logic of constraints

LTL linear temporal logic

MBD model-based design

MDA model-driven architecture

MDD model-driven developmen

MDD model-driven development

MDRE model-driven requirements engineering

MMM METROPOLIS meta-model

MoC model of computation

MSPS mega samples per second

OBP object based programming

OJT on-the-job-training

OMG Object Management Group

OOP object oriented programming

PBD platform-based design

PIM platform-independent model

PRF pulse repetition frequency

PSM platform-specific model

PSoC programmable system on a chip

RA requirements analysis

RAM random access memory

RE requirements engineering

RTL register transfer language

RUP rational unified process

SDRF software defined radiofrequency

SIS a system for sequential circuit synthesis

SLD system level design SoC system on a chip

SoPC system on a programmable chip

SRAM serial random access memory

SWAP size weight and power

UAV unmanned aerial vehicle

UHF ultra-high frequency

UML universal modeling language

Verilog verify logic

VHDL VHSIC hardware description language

VHSIC very high speed integrated circuit

VIS verification interacting with synthesis

#### **EXECUTIVE SUMMARY**

Creating an embedded system which meets its functional, performance, cost, and schedule goals is a software-and-hardware codesign problem, since the design of the software and hardware components influence each other. The traditional design methodology is sequential, with hardware designed first and then software. The lack of a unified and unbiased approach can lead to suboptimal design and incompatibilities across the software and hardware boundary.

To solve these problems, we develop a new codesign methodology to partition software/firmware/hardware, and then map functional components to design patterns if existing. This methodology includes first building a tree with conjunctions and disjunctions of possible mappings from functional components to the options of software, firmware, and hardware following requirements and constraints; second, rating the cost of each mapping; third, searching the tree to find a minimum weighted sum of the costs; and fourth, identifying existing design patterns once design is selected, and otherwise synthesizing new design patterns.

We tested our methods on three application areas. The first was a digitizer-filter architecture for ultra-high frequency signals. The major challenge was how to move ultra-fast data from a faster sensor (including a digitizer) to a slower processor and then perform useful tasks. We implemented and tested this application on a Tektronix/Synopsys demo embedded system based on the test specifications established by the vendor and Joint Electronic Warfare Effects Laboratory (JEWEL) at Point Mugu, California.

The second application was a digitizer-filter architecture for low-frequency requirements. The challenge was how to partition software/firmware/hardware and then map design to the existing vendor products to save development time and cost. We implemented and tested this application on a Pentek embedded system based on the test specifications established by the vendor and Airborne Interceptor Research Laboratory (AIRL) at Point Mugu, California. By way of contrast, for a period of more than 12

months from 2011 to 2012, with 10 engineers, we spent \$3.16M on an airborne interceptor project (including software, firmware and hardware designs) but failed to produce any software deliverable. In 2013, for a period of five months, starting from ground zero, with two engineers, we only spent \$90K on the same project with the help of our new software/firmware/hardware codesign methodology; we were able to map 86 percent of our project unto vendor's existing products and delivered Doppler range gating software successfully.

The third application was a hidden Markov model using dynamic programming. The challenge was how to partition software/firmware/hardware for better processing speed performance. We discussed the advantages and disadvantages of mapping hidden Markov models unto software and firmware in terms of cost, speed and design complexity.

#### ACKNOWLEDGMENTS

First I would like to thank my wife, Jennifer, for her unconditional love and encouragement for my PhD studies. Throughout this journey, she has never complained about my long hours of studies each day, including weekends and holidays. To show her support, she even accompanied me for my written examination and final oral defense at Naval Postgraduate School, Monterey, California.

This research is based on Dr. Melissa Midzor's vision in digitizing radiofrequency signals in the gigahertz range used for electronic warfare signal simulation. Without her vision and support in funding, equipment, and personnel, this research cannot be made possible.

Through weekly phone conversations, Professor Neil C. Rowe tirelessly provided strategic advice ensuring our work was on track. Even though, he is methodical in guiding this project, he is extremely flexible and open-minded, which allowed me to have much freedom in accomplishing the task. In addition, Professor Rowe suggests using an artificial intelligence A\* search with embedded AND nodes methodology to partition software/firmware/hardware, and then match the optimal leaf-nodes to some design patterns for embedded system design. Software and hardware partitioning is a very difficult challenge in the field of hardware-and-software codesign.

Special thanks to Professor Roberto Cristi for his enthusiasm and knowledge in digital signal processing. He gave directions in dividing ultra-wide bandwidth signals into multiple parallel subbands using polyphase discrete Fourier transform filter banks. Equally important, he has been enormously generous in sharing his lecture videos and class notes with me on various topics.

Professor Shing thoroughly reviewed my dissertation and pointed out the most important weakness in software testing. Without his meticulousness and diligence, this dissertation could not have been completed. In addition, I audited his Requirements Engineering course and much of the material in Chapter II reflects his knowledge.

Personally, I have taken Formal Methods and audited Software Testing from Professor Auguston; I was very impressed with his knowledge in fundamental software engineering and up-to-date tools. His influence can be seen clearly in Chapter V (Case Study One). Last but not the least, while Professor Auguston was experiencing a very difficult health condition, he was still able to promptly review my dissertation and give me valuable feedback.

#### I. INTRODUCTION AND PROBLEM ADDRESSED

#### A. ADDRESSED PROBLEM

Creating an embedded system which meets its functional, performance, cost, and schedule goals is a software-and-hardware codesign problem, since the design of the software and hardware components influence each other [1]. Traditionally, when designing an embedded system, hardware is designed first by a group of hardware engineers, and then software is designed by a group of software engineers. Once a design is completed, both software and hardware engineers strive to make every effort to implement changes in software to avoid expensive hardware redesign. The problems with this approach are:

- A presumptive definition of software-and-hardware partitions can cause suboptimal designs.

- Lack of a unified software-and-hardware design methodology can cause incompatibilities across the software and hardware boundary.

To solve these problems, the codesign group at U.C. Berkeley in 1997 developed a framework, POLIS, with a unified software-and-hardware representation for unbiased specification, automatic synthesis, and validation of the embedded systems. The most difficult challenge in POLIS according to the group is software-and-hardware partitioning because the partitioning decisions are heavily based on designer's expertise and are very difficult to automate [2].

For embedded systems, software can be divided into three categories: computer-based software, central-processing-unit (CPU) firmware, and reconfigurable computing firmware. Software and firmware both contain programming instructions and necessary documentations, except that software runs on a computer and firmware runs on a hardware device. As a result, it is helpful to replace the term software/hardware codesign with software/firmware/hardware codesign.

Our goal for this dissertation is to provide a new software/firmware/hardware codesign methodology for seamless integration and design of embedded systems. There

are several problems to resolve, in particular functional decomposition, what should be classified as software or firmware or hardware, design-pattern mapping, and new design-pattern synthesis.

#### B. MOTIVATION

A motivating problem is how to push the upper limit of the capability in moving very fast digitized data from a sensor and digitizer to a slower processor, and then usefully process it in real-time. The conventional data rate for a sensor is in the range of megasamples-per-second; the data rate for our research is in the range of gigasamples-per-second and above. This is too fast for an all-software design.

The solution to this problem is in software-and-hardware codesign because the final system must be flexible enough to accommodate different data rates and perform various useful tasks, and must not only function properly but also meet critical timing constraints due to its ultra-high data speed [1,3]. There are many details we need to keep straight; a software/firmware/hardware codesign methodology will help us build designs correctly and efficiently.

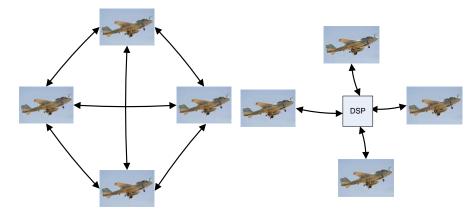

There are many similar problems in design of systems for use in electronic warfare, in which proper design decisions are critical because of the signal frequencies involved and the processing time required. Electronic warfare tries to dominate the electromagnetic spectrum, or to protect our use of the electromagnetic spectrum and to exploit the enemy's spectrum. This involves minimizing mutual interference among friendly systems, minimizing detection by enemy sensors, and minimizing enemy interference with the ability to execute a military deception plan. Techniques often used to prevent or reduce an enemy's effective use of the electromagnetic spectrum are jamming and electromagnetic deception [4]. An advantage can be gained in the domain of the electromagnetic spectrum by being able to handle higher frequencies than an adversary can handle.

A wide variety of equipment has been designed and used in electronic warfare, such as Northrop Grumman EA-6B Prowlers, Boeing EA-18G Growlers, unmanned aerial vehicle systems, and ground jamming vehicles. To ensure the readiness of this

equipment, tests and evaluations are required. The environment for tests and evaluations is simulated in software (that is, the aircraft, vehicles, terrain and weather), but the hardware is real.

#### C. CLAIM

Our claim is that rather than the trial-and-error approach being currently practiced for embedded system design, a new software/firmware/hardware codesign methodology based in software engineering has the potential to systematically build correct designs efficiently to satisfy the requirements provided by the stakeholders.

#### D. TRADITIONAL METHODOLOGY FOR DSP DESIGN

For many real-time applications, a specialized field-programmable gate array (FPGA) embedded system, instead of a general-purpose computer, should be used [5]. The reason is that an FPGA can process hundreds of times more operations per clock cycle than a processor. The speed of a state-of-the-art multicore processor is in gigahertz and the speed of a state-of-the-art FPGA is in hundreds of megahertz. Also, a typical high-end FPGA has thousands of times more parallel channels than a multicore processor.

Traditional FPGA-based embedded software is written manually from text-based specification and requirements. This approach is time-consuming and error-prone, and there is little tracking to ensure that changes are correctly implemented [6]. A more systematic approach provided by software engineering could reduce these problems.

#### E. OUR SOFTWARE ENGINEERING METHODOLOGY

To develop specifications, we start with gathering high-level requirements in the form of novel ideas and questions. With proper domain knowledge, we can derive subrequirements from them. In requirements analysis, we use feature models and decision trees to explore design concepts and possible implementation technologies for the feasibility check. These design concepts and implementation technologies are in the form of models, and they can also be used for fine-tuning the requirements in the next requirements development iteration. During this phase, we treat software, firmware, and

hardware together, since a software component and a (reconfigurable) hardware component can often both achieve a design, although software tends to be more flexible and hardware tends to be faster [7]. The final products at the end of this stage should include requirements and design models as well as dataflow and control-flow architectures.

We can generate models by using specialized FPGA embedded software design tools. Non-specialized tools such as documentation, reports, tables, diagrams, and algorithms can also assist model building without the benefits of automatic code generation [8].

Next, we must decide what should be classified as software, what should be classified as firmware, and what should be classified as hardware. Software-and-hardware partitioning involves a diversity of applications, design styles and implementation technologies; ultimately it depends on human expert knowledge [7]. In this dissertation we propose using a tree of options to find possible mappings from functional components to the set of modalities {software, firmware, hardware}. When an optimal node (solution) is chosen, we can expand any component within a node into subcomponents, and then use the same methods to assign the subcomponents. When we have found the best assignment for the subcomponent search, we embed it in the original tree.

During the construction phase, we apply software and FPGA programming methodology, and perhaps additional hardware design, to implement the design. The process flow includes designing (using a hardware description language or a high-level graphical modeling tool), functional and timing simulations, doing synthesis, implementation and programming.

#### F. TOPICS COVERED FROM CHAPTERS II TO VIII

In Chapter II, we survey some important software-engineering methodologies in the fields of requirements engineering, embedded-system design, and concurrent-system design. We also discuss FPGA programming languages and FPGA design methodology. In Chapter III, we use an *OR* tree with embedded *ANDs* to partition

software/firmware/hardware, and then use the same methodology to map the optimal leaf-node to a design pattern if existing; otherwise, we synthesize a new design pattern. In Chapter IV, we present five example design patterns for reconfigurable computing based embedded systems: data alignment, post-de-serialization bits remapping, pre-serialization bits remapping, polyphase DFT filter banks and switch-and-filter. These patterns were used in implementing our case studies. In Chapter V, we present a case study using a Tektronix Digitizer/FPGA/DAC demo unit to digitize and process radiofrequency signals up to 6 gigahertz and then discuss the test results for this case study. In Chapter VI, we present a case study fora conventional Doppler radar receiver. In Chapter VII, we present a case study involving a Hidden Markov model (HMM). In Chapter VIII, we conclude the dissertation by stating our major contributions and suggest directions for future research.

#### II. PREVIOUS WORK

In this chapter we will survey current software engineering methodologies related to requirements engineering (RE), embedded-system design, hardware-and-software codesign (or concurrent system design), and field-programmable gate array (FPGA) design to lay the foundation for our research.

#### A. REQUIREMENTS ENGINEERING

#### 1. Requirements Development

Requirements development includes six key activities—elicitation, analysis, validation, negotiation, documentation and management [9]. Elicitation is to discover system requirements through consultation with stakeholders, and to establish a scope and boundary for the project. Analysis is to analyze requirements in detail and to identify possible conflicts and overlaps. Validation is to review or validate requirements for clarity, consistency, and completeness with stakeholders. Negotiation with stakeholders establishes which requirements are to be considered. Documentation is to write down agreed requirements at a certain level of detail for review, evaluation, and approval. Requirements management is an ongoing activity that starts from the moment the first requirement is elicited and ends only when the system is finally decommissioned [10]. Requirements management includes software-baseline definition, change control, and approval and status tracking. The baseline can be defined as a set of features agreed to be delivered to customers in a specific software version [11].

Some requirements engineering researchers use the term "specification" for "documentation" [12], combine analysis and negotiation into analysis activity, and treat management as a different topic. Based on this, requirements development includes four key activities—elicitation, analysis, specification and validation [10].

The scheduling for requirements engineering should not be less than one third of the entire project time, since much time is required to include research or exploration of new techniques [13].

#### 2. Rational Unified Process

To manage requirements effectively, we must have a well-defined software lifecycle development process. The waterfall model, introduced by Winston Royce in 1970 [14], requires complete and fully elaborated requirements before design, coding, testing, operation and maintenance. This is not practical since requirements change throughout the entire software lifecycle. The spiral model, introduced by Barry Boehm in 1988 [15], requires multiple risk analyses, validations and prototypes before a rigorous waterfall methodology is followed, and also has proven to be expensive and time-consuming.

In 1995, Philippe Kruchten [16] introduced the *iterative* approach. This divides a software project into multiple time-boxed iterations. An iteration is a sequence of activities, such as requirements, design, implementation, test, and integration, resulting in an executable of some type. Each iteration is based on prior iterations. Some benefits of the iterative process are early risk mitigation, early feedback, and analysis-paralysis avoidance.

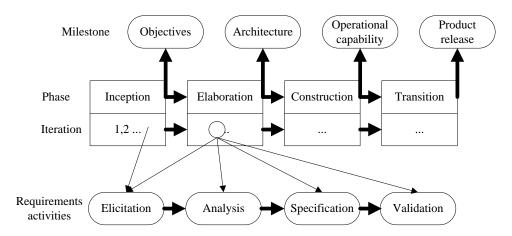

In 2003, Rational Software Corporation (a division of IBM) proposed the "rational unified process" for software lifecycle development. It is a sequence of inception, elaboration, construction, and transition. Each phase consists of one or more executable iterations of the software at that stage of development. Inception is to define the scope of project, and its milestone is the identification of actors and use cases. Elaboration is to plan project and specify features, and its milestone is the establishment of baseline architecture. Construction is to build the product, and its milestone is the building of initial operational capability. Transition is to deliver products to customers, and its milestone is the release of product. Each phase has multiple iterations. The number of iterations depends on the project size and agreement among stakeholders. The relationship between lifecycle phases, milestones and iterations are shown in Figure 1 [17].

Figure 1 Rational unified process lifecycle phases, milestones and iterations

## 3. Design-Based Requirements

The requirements and design activities must be iterative. Gestalt round-trip design, introduced by Grady Booch [18] in 1994, emphasizes the human characteristic of learning by completing [19]. In other words, the requirements at one iteration cause us to select certain design options, and the selected design options may in turn initiate new requirements. This is due to the fact that requirements are always changing and cannot be correctly defined until some design work is developed.

## 4. Test-Based Requirements

In 2008, Martin and Melnik proposed a Möebius strip approach for requirements-development [20]. A Möebius strip means that writing requirements and testing are closely interrelated. Writing requirements in the form of acceptance tests can reduce the number of pointless features and code and handle changes more efficiently. Every requirement must be testable with this approach.

## 5. Agile Software Development

In 2001, the Agile Alliance stated that software development should be focusing on (1) individuals and interactions over processes and tools, (2) working software over comprehensive documentation, (3) customer collaboration over contract negotiation, and (4) responding to change over following a plan [21]. With this approach, emphasis is

placed on the end result of working software rather than comprehensive documentation. In addition, the client is taken on-board as a member of the development team, so that missing requirements are discovered in the early software development stage.

## 6. Model-Driven Requirements Engineering

A model is a representation of a system that allows for investigation of the properties of the system and, in some cases, prediction of future outcomes. Software models come in many forms, such as use cases, diagrams, and statecharts [22].

Requirements can also be modeled, and the benefits of requirements modeling are: (1) allowing us to understand the product requirements precisely, (2) showing generalizations, (3) simplifying complex relationships between requirements, and (4) describing the context and background in which the product will be used.

There are different types of requirements models, such as business models, feature/goal models, analysis (use case) models, design models, implementation models and test models. A business model describes why a product is needed. A feature model describes the features of a product. A requirements analysis model explains the features in sufficient detail to define product specifications. A design model illustrates the architecture for the product. An implementation model describes the construction of the product. A test model describes how the product would be tested [23].

## 7. Model-Driven Development

Model-driven development (MDD) is a software engineering approach which uses models of high-level abstraction to create and evolve software. The goals of model-driven development are to simplify and formalize the various activities in software lifecycle [24]. According to Object Management Group (OMG), model-driven design can be realized by using model-driven architecture (MDA). Model-driven architecture specification consists of a definitive platform-independent model (PIM), plus one or more platform-specific models (PSMs) and sets of interface definitions, each describing how the base model is implemented on a different middleware platform.

## 8. Domain-Specific Modeling and Language

Domain-specific modeling (DSM) is a software engineering methodology for designing and developing software systems by using domain-specific modeling languages (DSL) to represent various features of the system [25]. Domain-specific languages support higher-level abstraction than general-purpose modeling languages, so they require less effort and fewer low-level details to specify a given system. Most domain-specific models and languages are created for a particular domain by a particular vendor with domain expertise; as a result, automatic quality code generation is made possible. As Booch pointed out in 2004, to achieve the full value of model-driven architecture, modeling concepts must map directly to domain concepts rather than computer technology concepts [26].

One example is hidden Markov model "toolbox" for MATLAB from MathWorks that supports inference and learning for hidden Markov models. This toolbox is designed for a specific domain (statistical inference) and the language is domain-specific with a higher-level of abstraction (e.g., TRANS representing transmission matrix and EMIS representing emission matrix); this model cannot be easily described by using a general-purpose Universal Modeling Language (UML).

The best practices put forth by the rational unified process (incremental and iterative), extreme programming (test-driven), agile development (client-oriented and design-based), and model-driven and domain-specific methodologies are used throughout the software-development lifecycle of our three case studies.

#### B. SOFTWARE ENGINEERING OF EMBEDDED SYSTEMS

An embedded system is hardware and software which forms a component of some larger system and which is expected to function without human intervention. Firmware is a software program or a set of instructions programmed on a reconfigurable hardware device. Software is associated with a computer system, firmware is associated with an embedded system, and both of them contain programming instructions and necessary documentation.

Microprocessors and FPGAs are two major kinds of programmable integrated circuits (ICs) in an embedded system. In this research, our embedded system contains FPGAs instead of microprocessors, so we will only survey the issues with FPGAs. Our rationale is explained in Section D, Chapter I.

Much embedded software is based on the traditional waterfall model, using "emphasis on fully elaborated documents as completion criteria for early requirements and design phases" [27]. Since code is written manually from text-based specifications and requirements, and fully elaborated documents are not possible for most projects, this approach is time-consuming and error-prone, and there is little tracking to ensure that changes are correctly implemented [6].

Model-based design allows concise representation of behavior at a high level of abstraction. It is a better choice for embedded software development since the entire system can be visualized graphically, which leads to easy comprehension of the system; its models can be validated and verified; and it is easier to refine models and track model changes than with text-based documents. Model-based design also creates a structure allowing for software reuse; options and performance can be evaluated and the outcome can be predicted; and code can be automatically generated from the fully tested specification for software development and rapid prototyping [28].

Some major specialized model-based embedded software design tools are Mathworks MATLAB/SIMULINK®, Synopsys Synphony Model Compiler®, Annapolis CoreFire®, and National Instruments LabView®. More general tools (such as documentations, reports, tables, diagrams, and algorithms) can also be used to assist model building without the benefits of automatic code generation [8].

# C. CONCURRENT SOFTWARE ENGINEERING OF EMBEDDED SYSTEMS

## 1. A Top-down Concurrent Design Process for an Embedded System

Creating an embedded system which meets its functional, performance, cost, and schedule goals is a hardware-and-software codesign problem, since the design of the hardware and software components influence each other [1]. We can define hardware-

and-software codesign as "meeting system level objectives by exploiting the synergism of hardware and software through their concurrent design" [29].