DUDLEY KNOX LIBRARY

NAVAL POSTGRADO ATA SCHOOL

MONTEREY, CALIFORNIA 95943-5002

# NAVAL POSTGRADUATE SCHOOL

Monterey, California

# THESIS

FIBER-OPTIC IMPLEMENTATION OF MIL STD-1553 A SERIAL BUS PROTOCOL

by

Robert Stanley Wester

March 1987

Advisor:

J.P. Powers

Approved for public release; distribution is unlimited.

| REPORT DOCUMENTATION PAGE                                                                                                                                               |                                     |                                           |                           |                       |           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------|---------------------------|-----------------------|-----------|--|

| 18 REPORT SECURITY CLASSIFICATION UNCLASSIFIED                                                                                                                          | 16 RESTRICTIVE MARKINGS             |                                           |                           |                       |           |  |

| 28 SECURITY CLASSIFICATION AUTHORITY                                                                                                                                    |                                     |                                           |                           | * *                   | roved for |  |

| 26 DECLASSIFICATION / DOWNGRADING SCHEDU                                                                                                                                | LE                                  | public release; distribution is unlimited |                           |                       |           |  |

| 4 PERFORMING ORGANIZATION REPORT NUMBE                                                                                                                                  | R(S)                                | S MONITORING C                            | ORGANIZATION RE           | PORT NUMBER(          | 5)        |  |

|                                                                                                                                                                         |                                     |                                           |                           |                       |           |  |

| 68 NAME OF PERFORMING ORGANIZATION                                                                                                                                      | 6b OFFICE SYMBOL (If applicable)    | 78 NAME OF MO                             | NITORING ORGA             | VIZATION              |           |  |

| Naval Postgraduate School                                                                                                                                               | 62                                  | Naval Pos                                 | stgraduate                | e School              |           |  |

| 6c ADDRESS (City, State, and 2IP Code)                                                                                                                                  |                                     | 76 ADDRESS (City                          | , State, and ZIP (        | (ode)                 |           |  |

| Monterey, CA 93943-5000                                                                                                                                                 |                                     | Monterey, CA 93943-5000                   |                           |                       |           |  |

| 8a NAME OF FUNDING SPONSORING ORGANIZATION                                                                                                                              | 8b OFFICE SYMBOL<br>(If applicable) | 9 PROCUREMENT                             | INSTRUMENT IDE            | NTIFICATION NU        | MBER      |  |

| 8c ADDRESS (City, State, and ZIP Code)                                                                                                                                  |                                     | 10 SOURCE OF FL                           |                           |                       |           |  |

|                                                                                                                                                                         |                                     | PROGRAM<br>ELEMENT NO                     | PROJECT<br>NO             | TASK<br>NO            | WORK UNIT |  |

|                                                                                                                                                                         |                                     |                                           |                           |                       |           |  |

| FIBER-OPTIC IMPLEMENTATIO                                                                                                                                               | N OF MIL STD-                       | -1553: A S                                | SERIAL BUS                | S PROTOCO             | L         |  |

| WESTER, Robert Stanley                                                                                                                                                  |                                     |                                           |                           |                       |           |  |

| Master's Thesis   13b Time COVERED   14 DATE OF REPORT (Year, Month, Day)   15 PAGE COUNT   1987 March   108                                                            |                                     |                                           |                           |                       |           |  |

| 6 SUPPLEMENTARY NOTATION                                                                                                                                                |                                     |                                           |                           |                       |           |  |

| COSATI CODES  18 SUBJECT TERMS (Continue on reverse if necessary and identify by block number)  FELD GROUP   SUB-GROUP   MIL STD-1553; Serial Data Bus Protocol; Fiber- |                                     |                                           |                           |                       |           |  |

| Optics; Micro Computer System Design; Loop  Interconnect Topology                                                                                                       |                                     |                                           |                           |                       |           |  |

| '9 ABSTRACT (Continue on reverse if necessary)                                                                                                                          |                                     | 1 00                                      |                           | <del></del>           |           |  |

| This thesis explores the design and implementation of a Fiber Optic Link for use in MIL STD-1553 environments. The discussion includes specific                         |                                     |                                           |                           |                       |           |  |

| hardware and software designs to demonstrate a basic fiber-optic imple-                                                                                                 |                                     |                                           |                           |                       |           |  |

| mentation of th standard. These designs are presented in sufficient detail to allow reconstruction with a minimum of effort. Results such as                            |                                     |                                           |                           |                       |           |  |

| Built-In-Test performance and Maximum Data Rates are included. The design                                                                                               |                                     |                                           |                           |                       |           |  |

| and associated fiber optic link provide a good prototype to be used for further research involving fiber optic solutions for serial data link                           |                                     |                                           |                           |                       |           |  |

| Local Area Networks.                                                                                                                                                    |                                     |                                           |                           |                       |           |  |

|                                                                                                                                                                         |                                     |                                           |                           |                       |           |  |

|                                                                                                                                                                         |                                     |                                           |                           |                       |           |  |

|                                                                                                                                                                         |                                     | r                                         |                           |                       |           |  |

| 20 OSTRIBUTION/AVAILABILITY OF ABSTRACT  SAME AS R                                                                                                                      | PT DTIC USERS                       | UNCLASSI                                  |                           | TION                  |           |  |

| Prof J. F. Powers                                                                                                                                                       |                                     | 226 TELEPHONE (IF<br>(408)646-2           | nclude Area Code)<br>2679 | 22c OFFICE SY<br>62Po | MBOL      |  |

Fiber-Optic Implementation of MIL STD-1553: A Serial Bus Protocol

by

Robert Stanley Wester Captain, United States Air Force B.A.E.E., Park College, MO., 1976

Submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

NAVAL POSTGRADUATE SCHOOL March 1987

#### ABSTRACT

This thesis explores the design and implementation of a fiber optic link for use in MIL STD-1553 environments. The discussion includes specific hardware and software designs to demonstrate a basic fiber-optic implementation of the standard. These designs are presented in sufficient detail to allow reconstruction with a minimum of effort. Results such as Built-In-Test performance and maximum data rates are included. The design and associated fiber optic link provide a good prototype to be used for further research involving fiber optic solutions for serial data link Local Area Networks.

Thes15 W481

# TABLE OF CONTENTS

| I.   | INTR | ODUCT  | ION                                                 | 9  |

|------|------|--------|-----------------------------------------------------|----|

| II.  | MIL  | STD-1  | .553                                                | 11 |

|      | Α.   | CHAR   | ACTERISTICS OF MIL STD-1553                         | 11 |

|      | В.   | COMM   | NAND AND DATA WORD FORMATS                          | 11 |

|      | C.   | MIL    | STD-1553 COMMUNICATIONS CHANNEL                     | 13 |

|      | D.   | А ТҮ   | PICAL MIL STD-1553 ARCHITECTURE (F-16)              | 15 |

|      | E.   | THE    | HARRIS HD-15530 MANCHESTER ENCODER/DECODER CHIP     | 17 |

| III. | SYST | 'EM DE | SIGN SUMMARY                                        | 20 |

|      | Α.   | SYST   | EM OVERVIEW                                         | 20 |

|      | В.   | INTE   | LLIGENT FRONT END (/C8748)                          | 20 |

|      | C.   | SYST   | EM BLOCK DIAGRAM SUMMARY                            | 22 |

| IV.  | DETA | ILED   | SYSTEM DESIGN                                       | 26 |

|      | Α.   | SPEC   | IFIC CIRCUIT DESIGNS                                | 26 |

|      |      | 1.     | Control Signal Generation                           | 27 |

|      |      | 2.     | Data Paths for Parallel Modes of Operation          | 31 |

|      |      | 3.     | Interrupt Generation Logic for the Receive Function | 33 |

|      |      | 4.     | Terminal Address Selection Circuitry                | 33 |

|      |      | 5.     | Serial Input/Output Logic                           | 33 |

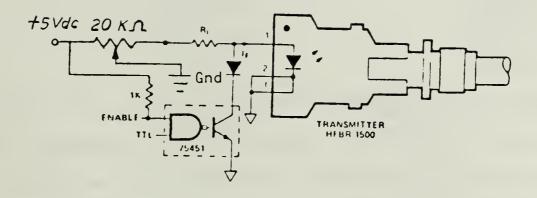

|      |      | 6.     | Fiber Optic Receiver/Driver Circuitry               | 36 |

|      | В.   | SPEC   | IFIC SOFTWARE ROUTINES                              | 36 |

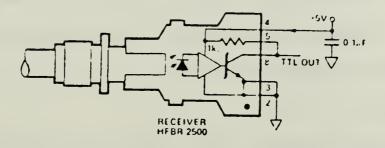

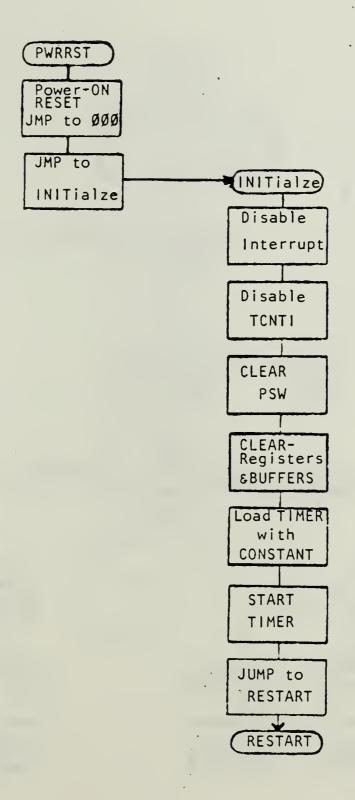

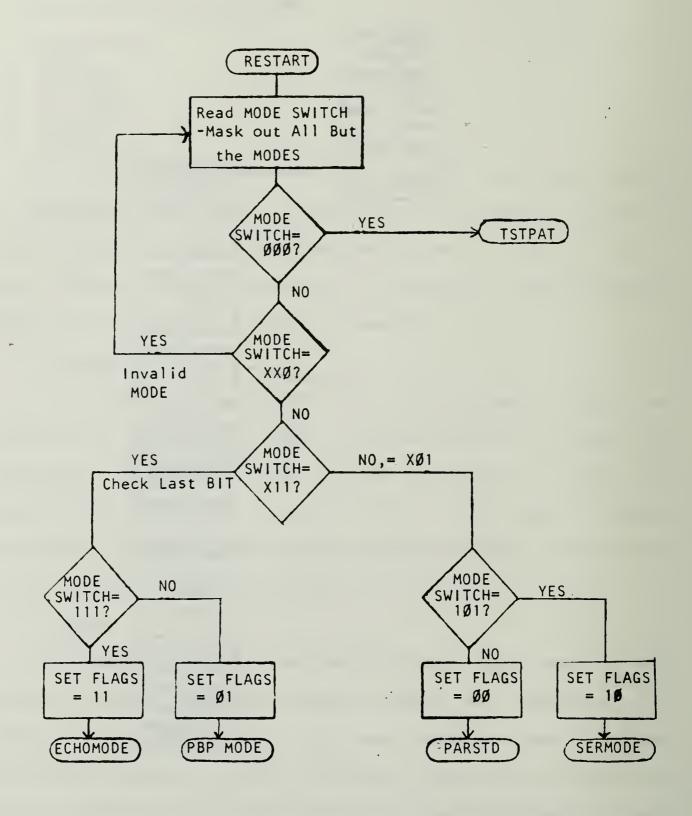

|      |      | 1.     | Restart/Init                                        | 38 |

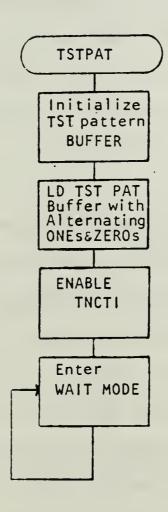

|      |      | 2.     | TSTPAT                                              | 38 |

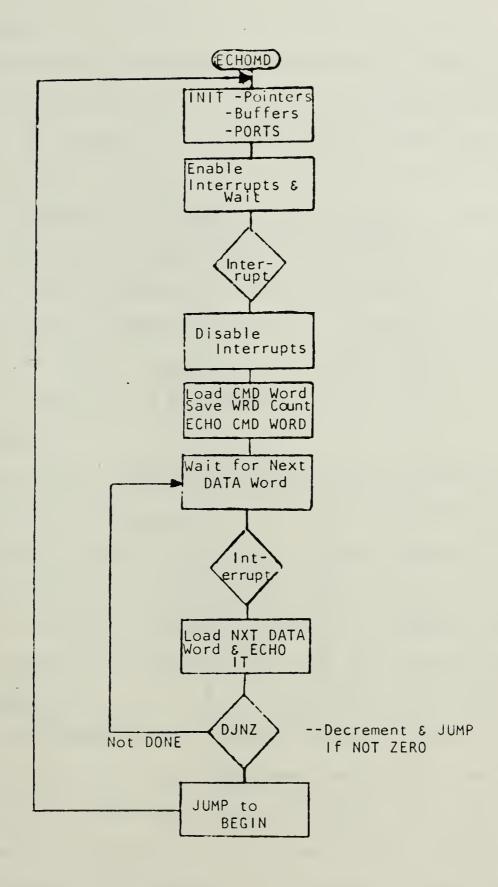

|      |      | 3.     | ECHOMODE                                            | 42 |

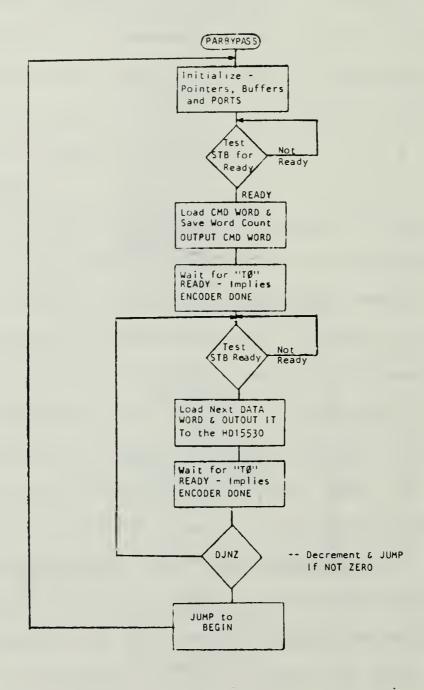

|         |      | 4.     | PARBYPASS                           | 42  |

|---------|------|--------|-------------------------------------|-----|

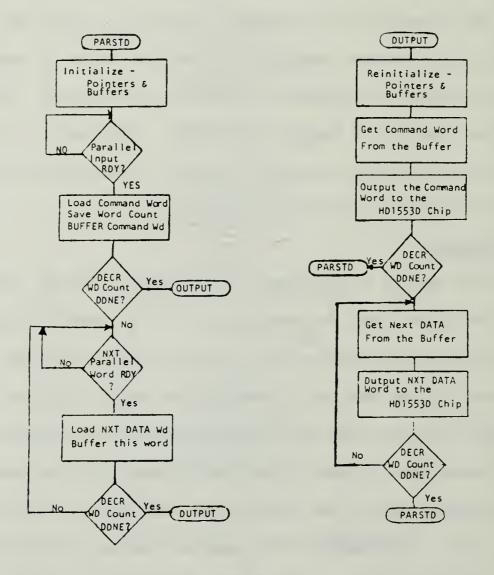

|         |      | 5.     | PARSTD                              | 45  |

|         |      | 6.     | SERMODE                             | 45  |

|         | С.   | INTE   | RFACING AND TESTING                 | 47  |

|         |      | 1.     | Z-8000 Evaluation Board             | 47  |

|         |      | 2.     | Parallel Interface Ports            | 47  |

|         |      | 3.     | Built-In-Test (BIT) Function        | 49  |

| ٧.      | DESI | GN DE' | VELOPMENT TOOLS                     | 53  |

|         | Α.   | THE I  | PROMPT-48 PROGRAMMER                | 54  |

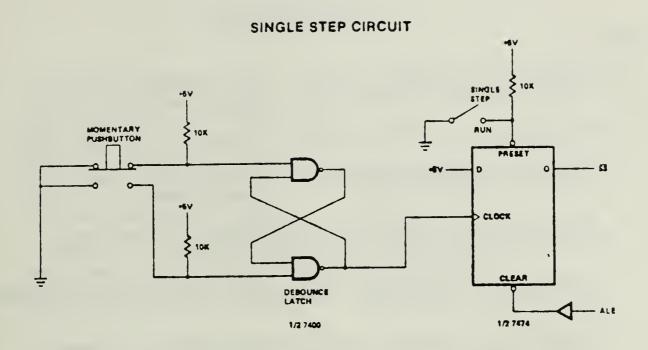

|         | В.   | SING   | LE STEP AND DISPLAY CARD            | 54  |

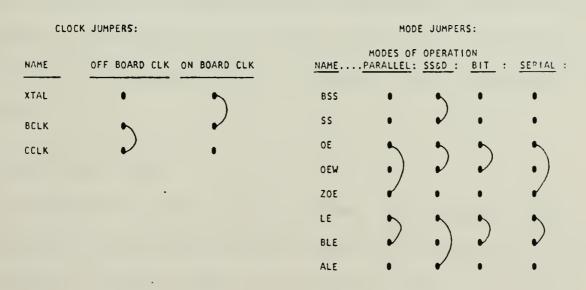

|         | C. ' | STRA   | PPING OPTIONS FOR TESTING           | 56  |

| VI.     | SYST | EM RE  | SULTS                               | 59  |

|         | Α.   | IIXAM  | MUM DATA RATE                       | 59  |

|         | В.   | INTE   | RFERENCE/EMANATION AND ISOLATION    | 61  |

|         | C.   | BUIL   | r-in-test (BIT) Results             | 62  |

| VII.    | CONC | LUSIO  | NS AND RECOMMENDATIONS              | 66  |

|         | Α.   | CONCI  | LUSIONS                             | 66  |

|         | В.   | RECO   | MMENDATIONS                         | 66  |

| APPENDI | X A: | MIL :  | STD-1553 CARD LAYOUT AND SCHEMATICS | 69  |

| APPENDI | Х В: | SOFT   | NARE LISTINGS for the C8748         | 72  |

| APPENDI | X C: | SING   | LE STEP AND DISPLAY CARD SCHEMATIC  | 104 |

| LIST OF | REFE | RENCE  | S                                   | 106 |

| INITIAL | DIST | RIBUT  | ION LIST                            | 107 |

# LIST OF FIGURES

| 1.   | MANCHESTER II BiPhase Encoding Scheme                                  | 12 |

|------|------------------------------------------------------------------------|----|

| 2.   | MIL STD-1553 Command and Data Word                                     | 12 |

| 3a.  | MIL STD-1553 Transformer Coupled Coaxial Cable for Serial Bus          | 14 |

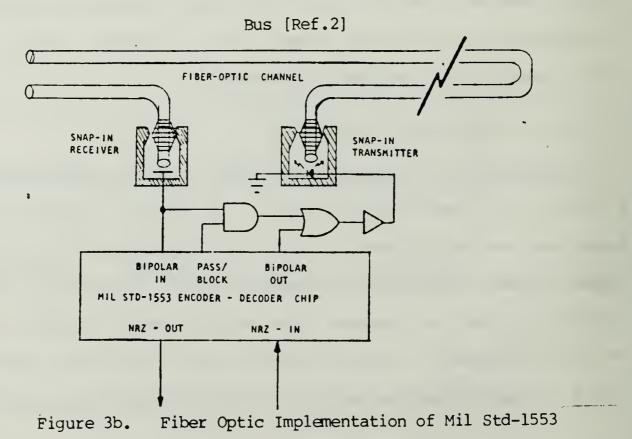

| 3b.  | Fiber Optic Implementation of Mil Std-1553                             | 14 |

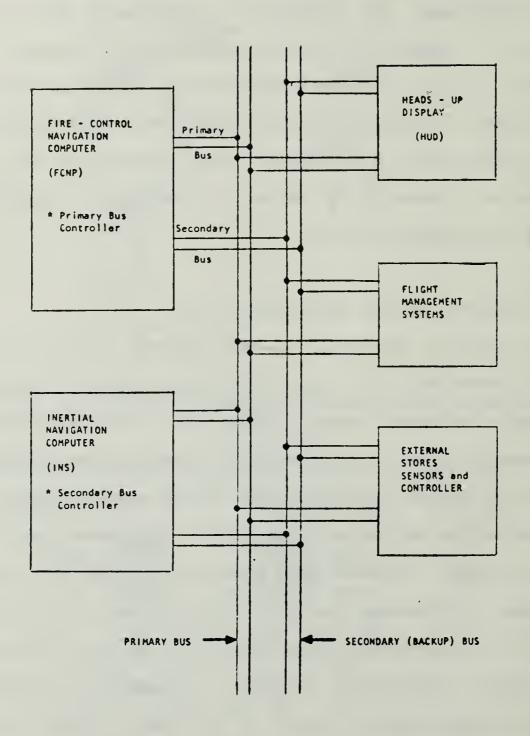

| 4.   | A Typical MIL STD-1553 Application - the F-16 Aircraft Avionics System | 16 |

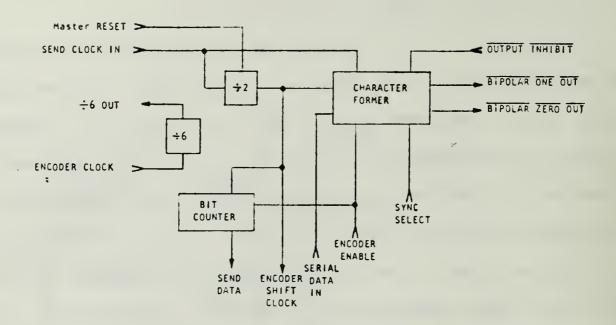

| 5.   | Harris HD-15530 Encoder                                                | 18 |

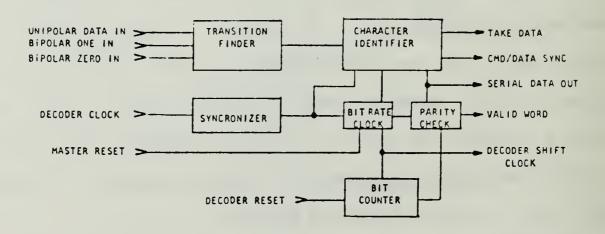

| 6.   | Harris HD-15530 Decoder                                                | 18 |

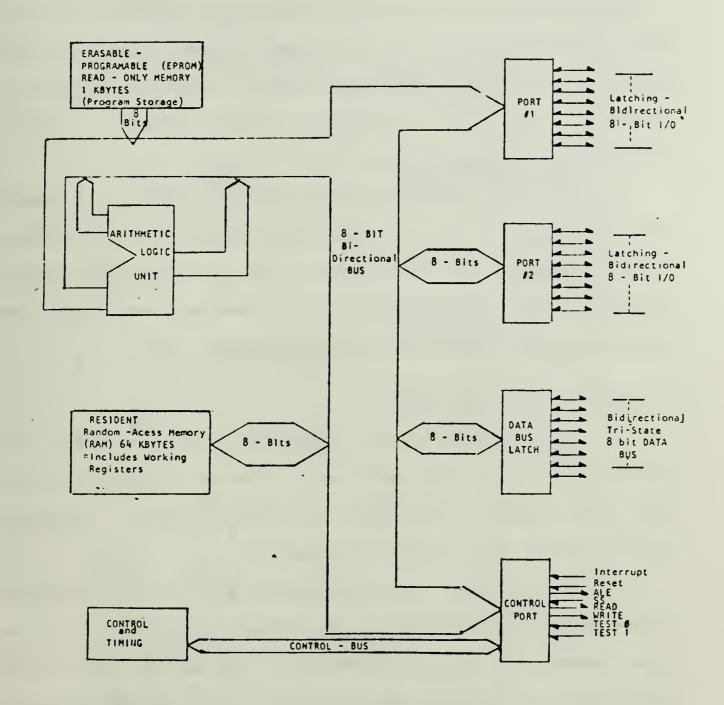

| 7.   | Block Diagram of the MC8748                                            | 21 |

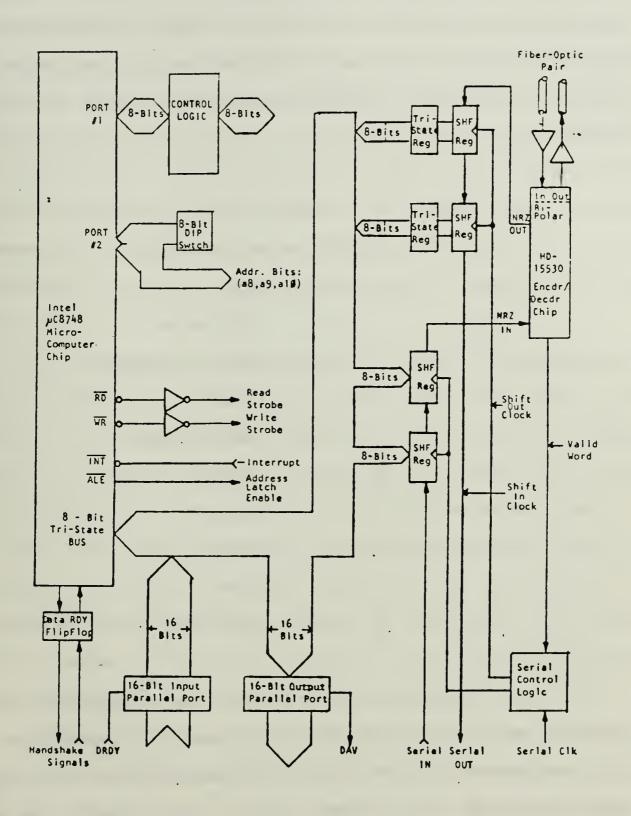

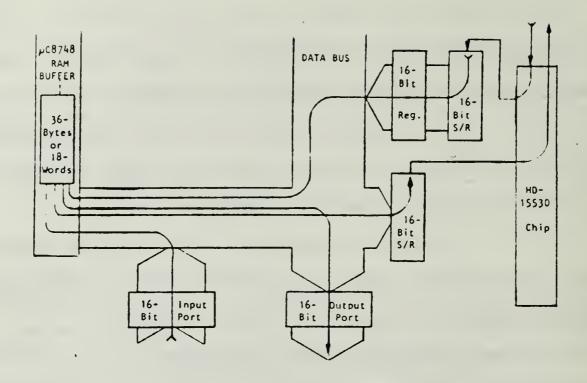

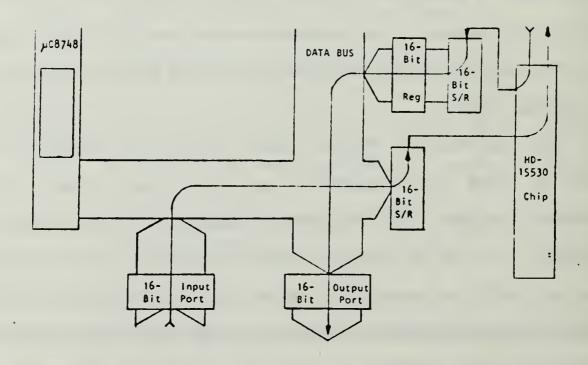

| 8.   | Block Diagram of the MIL STD-1553 Card Design                          | 23 |

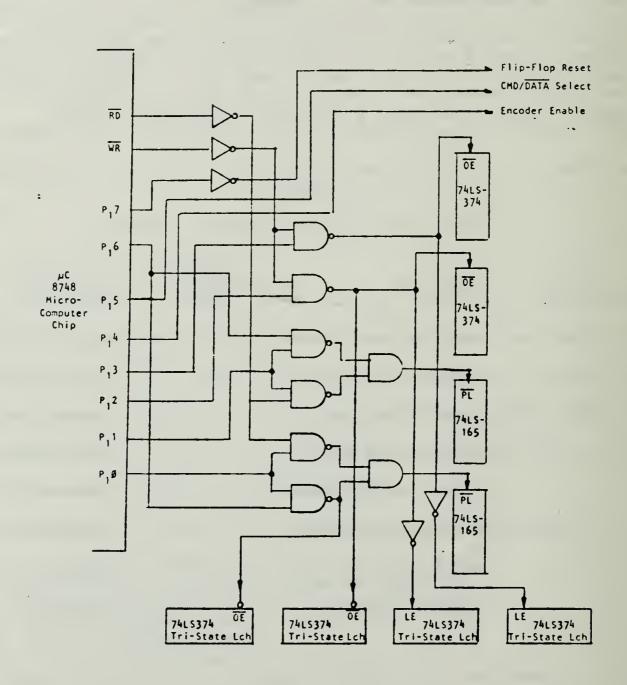

| 9.   | Control Logic                                                          | 28 |

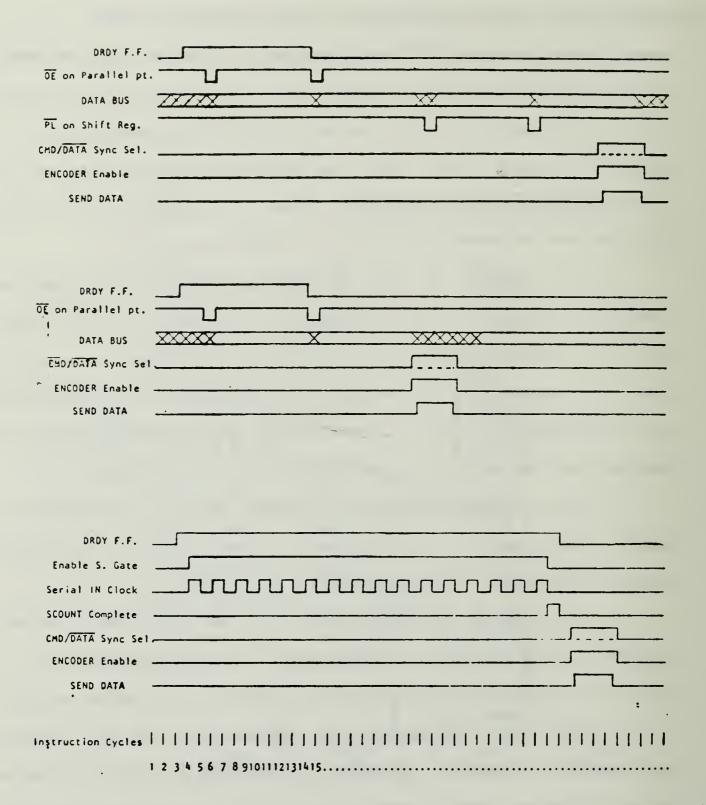

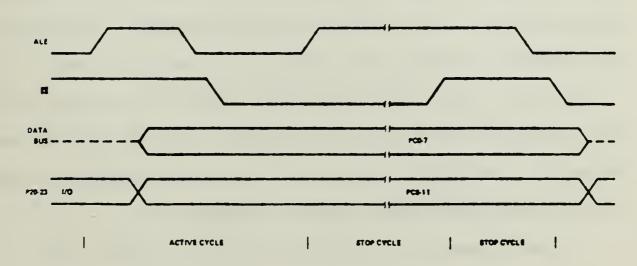

| 10.  | Timing Diagrams for Parallel and Serial Modes of Operation             | 30 |

| 11.  | Data Path for Parallel Standard Mode                                   | 32 |

| 12.  | Data Path for Parallel Bypass Mode                                     | 32 |

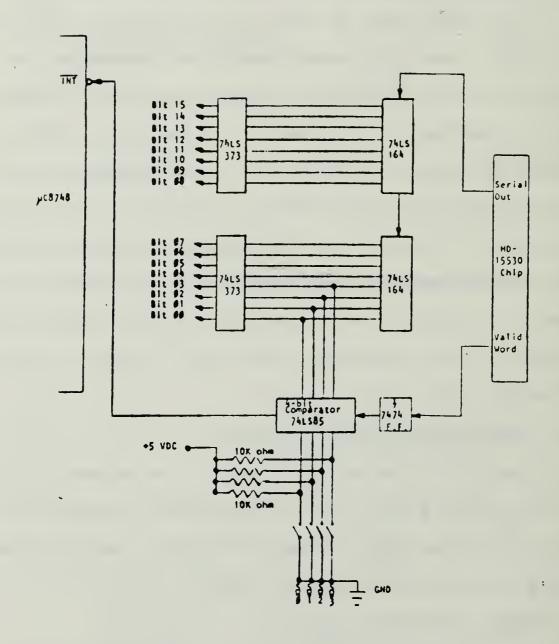

| 13.  | Terminal Address Selection and Interrupt Generation Circuits           | 34 |

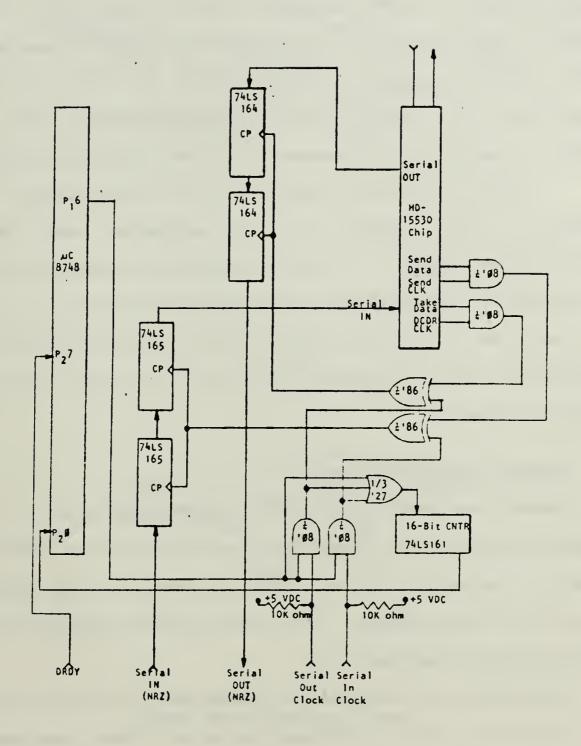

| 14.  | Serial Input/Output Logic and Data Paths                               | 35 |

| 15.  | Fiber Optics Receiver/Driver Circuitry                                 | 37 |

| 16a. | Flow Chart for the INIT Routine                                        | 39 |

| 16b. | Flow Chart for the RESTART Routine                                     | 40 |

| 17.  | Flow Chart for the TSTPAT Routine                                      | 41 |

| 18.  | Flow Chart for the ECHOMODE Routine                                    | 43 |

| 19. | Flow Chart for the ParBypass Routine                            | 44  |

|-----|-----------------------------------------------------------------|-----|

| 20. | Flow Chart for the ParStd Routine                               | 46  |

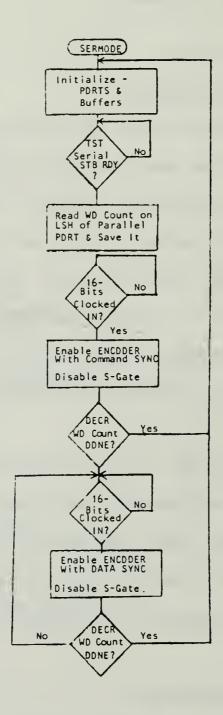

| 21. | Flow Chart for the SERMODE Routine                              | 48  |

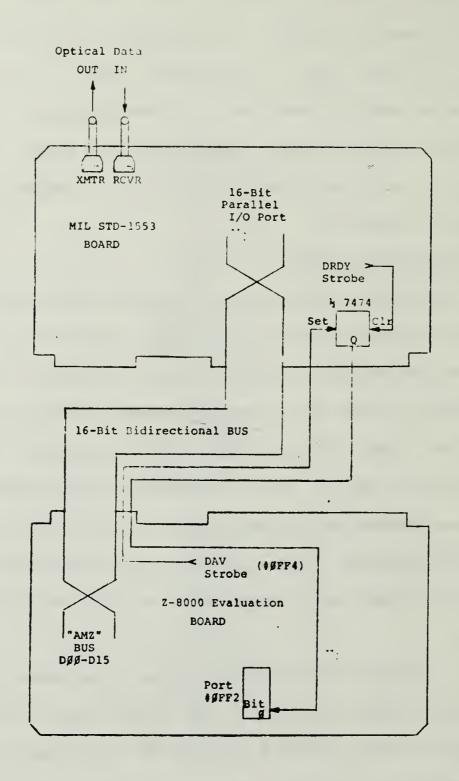

| 22. | Z-8000 Evaluation Board to MIL STD-1553 Card Parallel Interface | 50  |

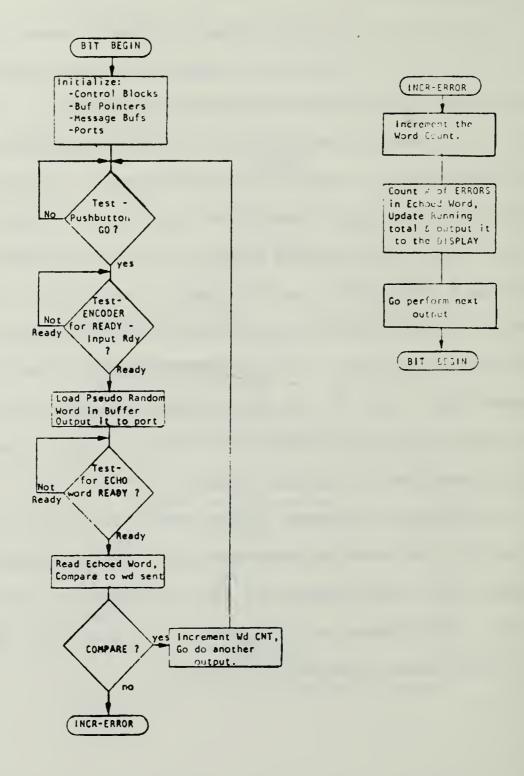

| 23. | Flow Chart for the Built-In-Test (BIT) Routine                  | 52  |

| 24. | Timing Diagram for the "Single Step and Display" Card           | 55  |

| 25. | Strapping Options for Testing                                   | 57  |

| 26. | Built-In-Test (BIT) Results                                     | 64  |

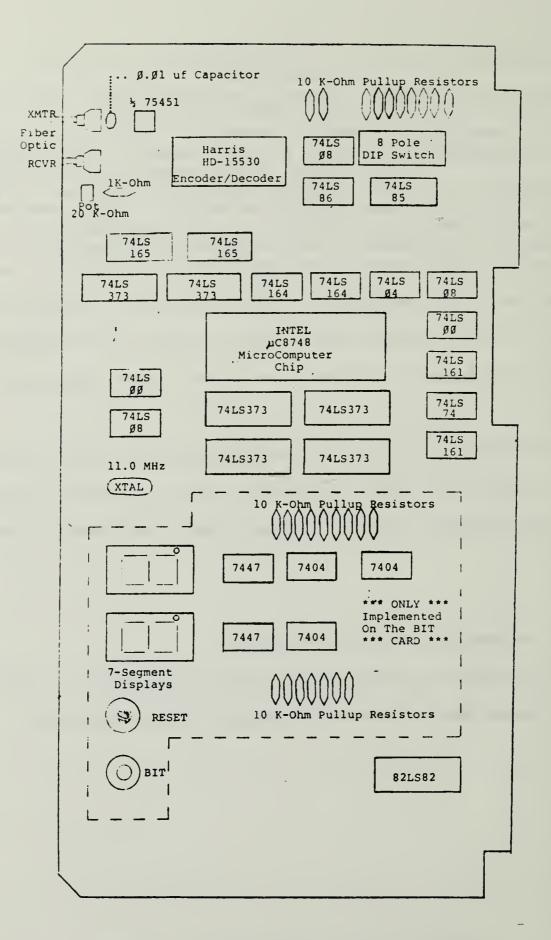

| Al. | MIL STD-1553 Card Chip Placement                                | 70  |

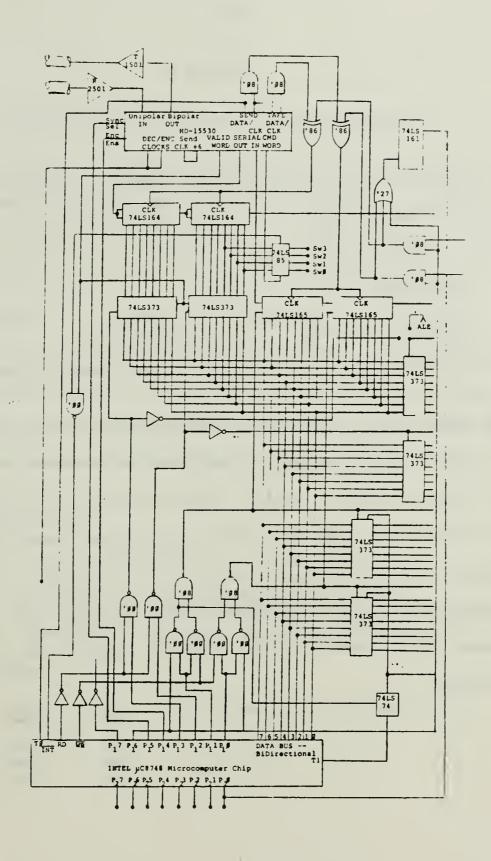

| A2. | Complete Circuit Schematic for MIL STD-1553 Card                | 71  |

| Cl. | Single Step and Display Card Schematic                          | 105 |

#### DEDICATION AND ACKNOWLEDGEMENT

This work is dedicated to the memory of my father, Robert Lee Wester, who passed away during my tenure at NPS. May God attend him.

I also wish to recognize those who provided critical support during the conduct of my graduate studies. Professor John Powers, my thesis advisor, rendered sound engineering advice and direction preventing excursions from the optimum path. John Glenn, Optics-Lab Manager, availed lab resources during around-the-clock check out sessions.

My wife, Gerri, and my children, Sharon, Richard, Joey, Russell, and Ryan generated abundant support and enthusiasm throughout my graduate studies, a KEY ingredient for success.

Major Ted Givins, Canadian Air Force, and his wife, Brenda, my good friends and neighbors, supplied warm words of encouragement and cookies. Brenda, my thesis typist, produced precise and timely drafts that defied correction.

Finally, I extend my gratitude to the U.S. Air Force for allowing me to attend a prestigious Engineering School. The Naval Postgraduate School curriculum builds character!

# I. INTRODUCTION

The subject of this thesis is the application of Fiber-Optics communications to a serial bus protocol known as Military Standard 1553 (Mil Std-1553) [Ref. 1]. Mil Std-1553 is a prime candidate for such an evolutionary step. It is widely used in weapon systems ranging from the F-16 fighter aircraft to the DIVAD gun system [Ref. 2]. The protocol has been around since 1973 and has currently been used on such weapon systems as the B-1B bomber and the Trident II submarine. Some unique benefits of will be discussed in the next chapter. A twisted shielded copper wire pair has been used to date for Mil Std-1553. It has been fabricated in such a way as to improve its noise immunity and has been coupled at each end via a matched transformer. Radio Frequency Interference and Electromagnetic Interference (RFI and EMI) have been issues, especially the Electromagnetic Pulse (EMP). data rate has been limited to one megabit per second to increase data integrity.

Fiber optics can be successfully used with Mil Std-1553 to virtually eliminate RFI and EMI problems and the data rate would be limited to the processing devices and not the communications channel itself. Thus the data rate could extend to fifty megabits per second or higher. Many other benefits of fiber optics will be discussed later.

The thrust of this effort is to demonstrate the implementation of Mil Std-1553 using fiber optics. This implementation is relatively basic but could be used as a model for further study. A fair amount of flexibility

has been included along with an intelligent front end (8748 microcomputer) to allow for any of a number of general applications. The design as it stands could be used on such applications as a Local Area Network (LAN) between engineering workstations, a plant control communications link, or a digital data acquisition system on board an airborne test bed. The system design will be discussed in sufficient detail to allow reconstruction with minimal effort.

# II. MIL STD-1553

#### A. CHARACTERISTICS OF MIL STD-1553

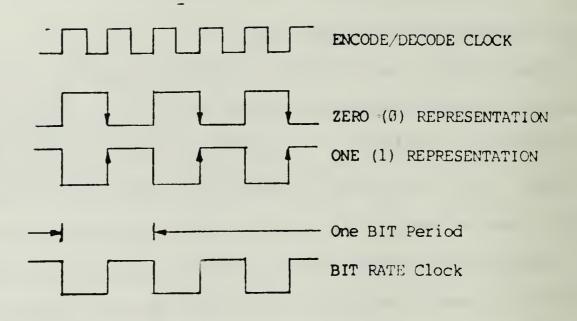

The protocol used in Mil Std-1553 is based on a Manchester II serially encoded BiPhase data stream. This encoding scheme was devised to allow for regeneration of the data clock directly from the data stream. The clock can be derived as the first harmonic of the serial data. Each encoded bit is formed in such a way as to contain a positive or negative going transition at the mid-bit position (see Figure 1). By detecting these transitions, the clock can be regenerated without a-priori knowledge of when the data stream started.

#### B. COMMAND AND DATA WORD FORMATS

As per Mil Std-1553, there are three types of word formats used. The Command and Status word formats are shown in Figure 2 [Ref 2]. The Data word format is also shown in Figure 2. As can be seen, each type of word has a unique type of synchronization pattern. This is referred to as Improper Manchester Sync. The sync pattern consists of a three bit period in which one and one-half bit periods are in one state and one and one-half bit periods are in one state and one and one-half bit periods are in the complementary state. This allows for easy discrimination between the "normal" serial data and the synchronization pattern. A free running clock is started at the beginning transition (whether positive or negative), and at each clock period the data stream is sampled. If the sampled stream indicates a higher low state for more than one bit period, an "improper Manchester" state is generated which is used to signal the beginning of a frame of data.

Figure 1. Manchester II BiPhase Encoding Scheme

| Bit Periods  | 1 2 3 | 4 5 6 7 8    | 9   | 10 11 12 13 | 14   15 16 | 17 18 19 | 20 |

|--------------|-------|--------------|-----|-------------|------------|----------|----|

|              |       |              |     |             |            |          |    |

| COMMAND WORD | SYNC  | TERM<br>ADDR | T/R | SubAddr     | Word       | Count    | P  |

|              |       |              |     |             |            |          |    |

|              |       |              |     |             |            |          |    |

| DATA WORD    | SYNC  | <b>-</b>     |     | — 16-Bit DA | TA         | -        | Р  |

Figure 2. Mil Std-1553 Command and Data Word [Ref. 1]

The Terminal address field represents the "from" terminal identification and the Sub-address field represents the "to" terminal identification. The "T/R" bit is used to pass a "token" in a token passing ring network. The Word Count field indicates the number of data words that are going to be sent with each Command word. The parity bit field is used to represent the "Odd" parity of the previous sixteen bits in the word. As can be seen in Figure 2, there can be 2<sup>5</sup> or 32 terminals addressed as well as 32 data words in each data block. Mil Std-1553 allows for several types of configurations. Ring networks can be established using the "T/R" token and Star networks can be implemented using the addressing fields.

Each Data word contains sixteen bits of binary data and is framed by the Data Sync and is error checked by the "Odd" parity bit in conjunction with the Manchester encoding scheme. The data is encoded and decoded in a "Non-Return to Zero" (NRZ) format. It can represent anything from ASCII characters to signed magnitude numbers.

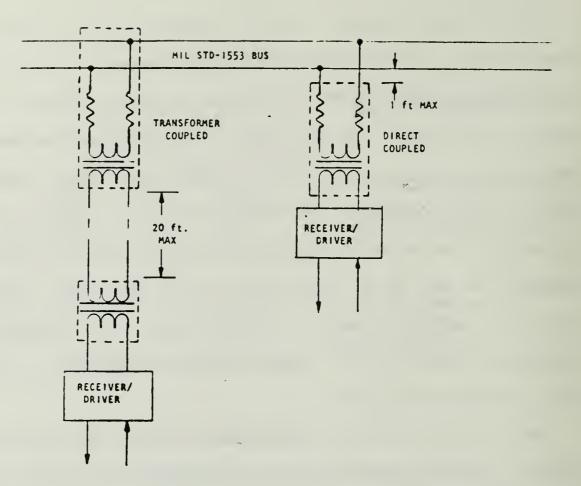

## C. MIL STD-1553 COMMUNICATIONS CHANNEL

As mentioned earlier, a twisted shielded coaxial cable has been used to date for the communications channel. The channel is excited using a transformer-coupled differential line driver/receiver pair as seen in Figure 3a. The transformer is a special type of "capacitively" excited device to provide for increased noise reduction and is "tuned" to the 1 MHz clock frequency. The driver/receiver pair excites the transformer with a 15 volt differential signal. Mil Std-1553 dictates very precise

Figure 3a. Mil Std-1553 Transformer Coupled Coaxial Cable for Serial

rise and fall times for this excitation in an attempt again to reduce the noise interference. The standard also specifies a particular "BNC" connector to allowfor the twisted shielded pair alignment. A very attractive alternative to this scheme would be, of course, fiber optics. Also included in Figure 3b is an "equivalent" fiber optic scheme which is greatly simplified and eliminates noise interference by optically isolating each communicating device. In addition, the bandwidth can exceed 1 MHz by factors of tens.

## D. A TYPICAL MIL STD-1553 ARCHITECTURE (F-16)

One particular application of the standard is the F-16 Digital Avionics System [Ref. 6]. A simplified block is shown in Figure 4. The Fire Control Navigation Computer (FCNP) acts as the Bus Controller in this star-type network. All intersystem communications are managed by the FCNP. A typical scenario might be for the Heads Up Display (HUD) to query the Inertial Navigation System (INS) for the present position. The HUD would request this data block from the FCNP. The FCNP would honor this request by directing the INS to ship this data block to the HUD. The INS would then ship this block directly to the HUD. In this scheme, each subsystem acknowledges receipt of a frame with a status word indicating proper/improper receipt of the frame, including the proper number of words received.

Figure 4. A Typical Mil Std-1553 Application The F-16 Aircraft Avionics System [Ref. 6]

#### E. THE HD-15530 MANCHESTER ENCODER/DECODER CHIP

In the late 1970s, Mil Std-1553 was implemented using approximately 30 small and medium scale integrated circuit chips. With the advent of Large Scale Integrated circuit (LSI) technology, the standard is increasingly being compacted into one or two LSI chips. With hundreds of thousands of transistors residing on a silicon wafer, the complexity of the standard can easily reside on one chip. In the early 1980s, several LSI implementations of the standard were being marketed. The HD15530 chip from Harris Semiconductor is one such implementation. It was incorporated in the design for this effort due to its availability. There are, in fact, many superior chips currently available [Ref. 1].

The HD15330 chip can functionally be broken down into two independent sections [Ref. 3]. The Encoder and the Decoder can operate completely independent of each other. They can be clocked at differing rates and enabled/disabled separately. The Encoder is shown in Figure 5. It accepts Serial NRZ data at the "Send Clock" rate and generates either bipolar one/zero Manchester data or unipolar data. It can generate either a Command/Status Sync or a Data Sync depending on the signal level at the "Command/Data" pin when the encoder is enabled. It requires a "Send Clock" at twice the desired data rate.

The "Decoder Clock" requires a clock at twelve times the data rate. Its internal circuitry contains a divide-by-six counter to conveniently derive the "Send Clock". The Decoder, as shown in Figure 6, accepts either unipolar or bipolar Manchester data with associated Sync and produces serial NRZ data with a Command or Data Sync indication. It also

Figure 5. Harris HD-15530 Encoder [Ref. 3]

Figure 6. Harris HD-15530 Decoder [Ref. 3]

provides for proper Mil Std-1553 decoding and detection via an internal bit rate clock, synchronizer, and parity checker. If the received word is proper in all respects, a "Valid Word" signal is generated. The serial NRZ data is clocked out at the "Decoder Shift Clock" rate.

The HD15530 chip can operate at a maximum data rate of 1.25 MHz. At this rate, the maximum "Encoder Clock" frequency is 15 MHz. The device is a CMOS chip and is compatible with standard TTL chip families. It uses a standard +5 VDC power source and with internal circuitry requires only one single phase clock. Both the Decoder and Encoder can be reset with "Master Reset".

## III. SYSTEM DESIGN SUMMARY

#### A. SYSTEM OVERVIEW

The intent of this effort was to demonstrate the feasibility of using fiber optics in many Mil Std-1553 architectures. Flexibility was incorporated in the design. For the purpose of initial verification and check-out, a "built in test" capability was incorporated.

Functionally, there are five modes of operation. Two are for testing/demonstration purposes and two are for parallel data input operation. The last is for serial data input operation.

To accomplish this generality and provide for ease of interfacing, an intelligent "front end" was designed. Availability of parts and development tools was a primary criterion.

# B. INTELLIGENT FRONT END CONTROL (/C8748)

In order to keep the chip count and development time to a minimum, a programmable controller was selected. The Intel 8748 microcomputer chip was readily available and provides most of the requisite facilities. It is not the optimum solution (see Conclusions and Recommendations) but allowed completion of this effort with reasonable resources.

A block diagram of the AC8748 is given in Figure 7 [Ref. 4]. As can be seen, it contains an Arithmetic Logic Unit (ALU), up to sixteen working registers in addition to an accumulator, various flags (C, AC, Z, FØ, and Fl), 64 bytes of Random Access Memory (RAM), and 1 kilobyte of Erasable Read Only Memory (EPROM) for Program Storage. It can handle one external interrupt and contains an internal programmable timer/counter

which can also interrupt. It contains internal circuitry to facilitate single step operation as an aid to program debugging.

Figure 7. Block Diagram of the /C8748 (Ref. 4)

There are two latching 8-bit Bidirectional Ports and one 8-bit Bidirectional Data Bus. Two Testable input pins are available as event sensors. The AC8748 has a power-down mode which can be utilized in

isolation type-scenarios. The chip can operate up to 6 MHz per memory cycle or be single stepped as mentioned above.

The instruction set is relatively flexible and efficient with 70% of the instructions requiring only one processor cycle (2.5 to 5.0 / Sec). There are data transfer instructions which can move data internally or externally. Accumulator operations include Arithmetic, Logical, Exchange, and bit manipulation functions.

In general, the /4C8748 satisfies all requirements of a general purpose computer. As such, it meets the requisites for this effort. Program development was tedious due to lack of user-friendly software development tools. An assembler, in-circuit emulator, and linker/loader would have reduced development time significantly.

## C. SYSTEM BLOCK DIAGRAM SUMMARY

The major components of the system design are the MC8748, the HD15530, control logic, data paths and the fiber optic interface. A high level block diagram of the design can be seen in Figure 8. A detailed circuit schematic can be studied in Appendix A.

The MC8748 provides data flow buffering and control. The HD15530 performs the Mil Std-1553 encoding and decoding. Control logic provides proper strobing and detection functions for the various ports and the HD15530 chip. The data paths provide either 8/16-bit parallel or serial data channels between the input/output interface, the MC8748, and the HD15530 chip. Fiber optic drivers and receivers convert the Mil Std-1553 encoded data to light that couples into the fiber optic snap-in link.

Figure 8. Block Diagram of Mil Std-1553 Card Design

There are five modes of operation as mentioned earlier. These modes of operation are provided by the software internal in the PC8748 EPROM. Each of the modes can be selected via a Dual In-line Package (DIP) switch located on the board. The Mode Selection Switch settings are indicated in Table 1.

TABLE 1

MODE SELECTION DIP SWITCH SETTINGS

| S <sub>8</sub> | S <sub>7</sub> | s <sub>6</sub> | S <sub>5</sub> | MODE                |

|----------------|----------------|----------------|----------------|---------------------|

| Ø              | Ø              | Ø              | Ø              | TEST Pattern        |

| Ø              | Ø              | Ø              | 1              | Parallel Standard   |

| Ø              | Ø              | 1              | Ø              | Invalid             |

| Ø              | Ø              | 1              | 1              | Parallel Bypass     |

| Ø              | 1              | Ø              | Ø              | Invalid             |

| Ø              | 1              | Ø              | 1              | Serial              |

| Ø              | 1              | 1              | Ø              | Invalid             |

| Ø              | 1              | 1              | 1              | Echo                |

| 1              | X              | Х              | Ø              | Built-In-Test (BIT) |

Testing and Demonstration can be accomplished using the Test Pattern generation mode on one board and the ECHO mode on a second board. In this configuration, a test pattern of alternating ones and zeros is transmitted across the fiber optic link to a second board. The second board in turn retransmits (echos) the pattern but swaps the addresses in the Command Word to allow receipt by the originating (test pattern generator) board. In this way, using an oscilloscope and the "Single

Step and Display" plug-in card (to be discussed later), program debugging and hardware check-out can be performed. Additionally, the drive current potentiometer for the fiber optic driver can be adjusted to the optimum level to ensure accurate reception while maintaining minimum drive current on the driver to increase the life of the fiber optic driver LED.

There are two modes of operation for parallel data transfers. One is the Parallel Standard mode in which the parallel data is buffered internally in the MC8748. Up to 12 hex or 18 decimal 16-bit words can be buffered in this way to allow slower devices to interface to the fiber optic link.

The second parallel mode bypasses the MC8748 by transferring the 16-bit parallel data directly to and from the I/O registers for the HD15530 chip. This is a much faster mode because the delay is related directly to the HD15530 encoding time and not the MC8748 buffering time. The MC8748 controls the transfer by simple handshaking techniques.

The Serial mode allows serial Non-Return-to-Zero (NRZ) data to be clocked in directly to and from the HD15530 chip I/O registers at an independent rate. The /4C8748 controls the transfer by sensing when 16 bits of serial data have been clocked in or out and then enabling the appropriate ports.

In either of the parallel modes and in the serial mode, the number of words to be transferred should reside on the least significant half (LSH) of the parallel port prior to enabling the /C8748 for transfer initiation.

# IV. DETAILED SYSTEM DESIGN

The detailed discussion of the hardware circuitry, software routines, and interfacing circuitry will be presented here. The intent is to explain the peculiarities of the design that are not inherently obvious.

As mentioned in System Design Summary, the system design can be segregated into three areas: hardware circuit design, software routine development, and interface logic. These categories will be expanded upon now.

#### A. SPECIFIC CIRCUIT DESIGNS

The hardware circuitry used in the design is predominantly Transistor-Transistor Logic (TTL) with the exception of the /C8748, the HD15530, and the fiber optic drivers and receivers. All devices are either TTL or TTL-compatible. Both the /C8748 and HD15530 chips were discussed earlier. They will be included here only in the context of how they were used to implement the system design.

The hardware circuitry that requires specific description are:

- 1. Control Signal Generation Logic

- 2. Data Paths for the parallel modes of operation

- 3. Interrupt generation logic for the receive function

- 4. Terminal Address Selection circuitry

- 5. Serial Input/Output logic

- 6. Fiber optic driver/receiver circuitry

Timing diagrams for some of the above will be included in the discussions to clarify their operation.

## 1. Control Signal Generation

The primary function of the Control Logic is to manage the operation of the serial and parallel ports in conjunction with the HD15530 encoder/decoder chip. A schematic of this circuit is given in Figure 9. As can be seen from Figure 9, Port 1 on the /C8748 provides excitation for the control logic. Each bit on this port initiates a specific function and Table 2 provides a definition for them.

TABLE 2

AC8748 PORT 1 AND PORT 2 SIGNAL DEFINITIONS

| Port 1 Bit No. | <u>Definition</u>      | Port 2 Bit No. | <u>Definition</u>  |

|----------------|------------------------|----------------|--------------------|

| Ø              | LSH Input Port Control | Ø              | Address Bit A      |

| 1              | MSH Input Port Control | 1              | Address Bit A      |

| 2              | LSH Shift Req Latch    | 2              | Address Bit A      |

| 3              | MSH Shift Req Latch    | 3              | Mode Switch 8      |

| 4              | Encoder Enable/Disable | 4              | Mode Switch 7      |

| 5              | CMD/DATA SYNC Select   | 5              | Mode Switch 6      |

| 6              | Serial Gate Control    | 6              | Mode Switch 5      |

| 7              | Flip Flop control      | 7              | Ser/Par RDY Strobe |

There are four classes of functions that will be discussed. In particular, control of the 16-bit parallel input port, the parallel-to-serial shift register latches for the HD15530 chip, the enabling and sync pattern selection function, and control of the Serial Input/Output mode data stream are managed by Port 1 of the /4C8748.

Parallel data input latching is accomplished by Port 1 bits zero and one. The software performs a logical "OR" function to turn these

Figure 9. Control Logic

bits "on" or "off". It then executes an "Input to Accumulator from the Bus" (INS A, BUS) to generate a "read" pulse. This pulse is "ANDed" with

Port 1 bits 0 or 1 to perform the latching function. This sequence of events loads the parallel data iteratively into the internal AC8748 buffer area for the Parallel Standard mode. In the Parallel Bypass mode, Port 1 bits 0 and 1 and bit 6 are set to one to simultaneously read and latch the parallel data from the parallel port directly to the parallel-to-serial shift register latches for input into the HD15530 chip.

The complement of this sequence is performed when data are received by the HD15530 chip and output to the parallel port. Port 1 bits 2 and 3 in conjunction with a "read" pulse are used to perform this function. Command/Data Sync selection and Encoder enable functions are also accomplished via Port 1. Bit 5 on the port is used to select the desired Sync type and Bit 4 enables the Encoder on the HD15530.

Timing diagrams are given in Figure 10 for all the functions above. Note that Port 1 is "Strobed" on and off by the instruction sequence "ANL Pl,#00; ORL Pl desired bit; ANL Pl,#00".

It is critical to clear the Port with an "ANL Pl,00" after each sequence to prevent two devices from trying to write simultaneously. In the serial mode, data are transferred in and out of the system exclusive of the NC8748 Bus. Handshaking and control functions are, however, performed by the NC8748. Specifically, Port 1 bit 6 enables or disables the Serial Control gates to pass or block the serial data stream. Port 1 bit 7 is used to detect when 16 bits of serial data have been shifted in or out.

Figure 10. Timing Diagrams for Parallel and Serial Modes of Operation

The T0 and T1 test inputs on the /UC8748 are used to sense the state of the HD15530 chip. T0 monitors the "Encoder Complete" state and T1 detects when a word has been received and decoded by the Decoder. On Port 2 bit 7 both the Parallel Input and Serial Input Strobes are monitored. By a series of Rotate Left thru Carry (RLC) and Jump if Not Carry (JNC) instructions, this bit is tested for ready.

Port 2 is also used to decode the desired mode of operation by reading the Switch positions on bits 6, 5, 4, and 3. Table 1 defines this relationship.

# 2. Data Paths for Parallel Modes of Operation

There are two modes of operation for the Parallel Input/Output functions. Figure 11 indicates the data path for the Parallel Standard mode and Figure 12 defines the data path for the Parallel Bypass mode. For both modes of operation, the Word Count must appear on the LSH of the parallel port along with the Subaddress field for each first (command) word. This information is read into the /4C8748 and used to manage the data transfer sequence.

For the Parallel Standard mode, all data is buffered in the /4C8748 on input and transferred out, in correct order, for the transmission sequence. For this mode of operation, the word count must not exceed 12 hex or 18 decimal or data will be lost. For the Parallel Bypass mode, only the command word (first word) is read into the /4C8748. All data words are transferred directly to the input Shift Register for the HD15530 chip. For this reason, data transfers are performed faster

Figure 11. Data Path for Parallel Standard Mode

Figure 12. Data Path for Parallel ByPass Mode

and the word count could extend to FF hex or 256 decimal. In this implementation however, the word count is limited to 20 hex or 32 decimal words to conform to Mil Std-1553.

## 3. Interrupt generation logic for the receive function

When a command word is received with the proper terminal address, an interrupt is generated. Special circuitry was designed to perform this function, alleviating the AC8748 from this task. Figure 13 indicates how the correct terminal address is detected. A comparator (74LS85) is used to compare the terminal address bits of a received command word with the switch settings on the upper 4 of the DIP switch. It is only enabled during receipt of a command word and therefore eliminates detection of an improper terminal address during a data word reception. The "A=B" signal triggers an interrupt on the AC8748. The interrupt remains cleared by application of the Command/Data NOT signal. Figure 13 shows this relationship.

# 4. Terminal Address Selection Circuitry

Figure 13 also shows this circuitry. The resistors are used to "pull-up" the input pins on Port 2 of the / "C8748. The "ON" side of these switches are grounded. Thus, to select a specific terminal address, the complement of the address is manually selected.

# 5. Serial Input/Output Logic

This circuit is indicated in Figure 14. Two Serial Control gates are used to pass or block the input or output stream. Port 1 bit 6 controls this gate. The "Exclusive OR" gates (74LS86) allow clocking of the serial data either by the HD15530 chip (in all modes) or by the Serial Input/Output operation; the AC8748 controls who clocks data.

Figure 13. Terminal Address Selection and Interrupt Generation Circuits

Figure 14. Serial Input/Output Logic and Data Paths

# 6. Fiber Optic Receiver/Driver Circuitry

The fiber optic front end was designed using a Hewlett-Packard HFBR1501/HFBR2501 transmitter/receiver snap-in optical link. This was chosen because of availability as well as performance characteristics. This link has a bandwidth which exceeds the Mil Std-1553 l MHz requirement. Fabrication of the cable was relatively simple and the snap-in connectors ensured reasonable alignment and optical coupling.

Figure 15 gives the circuit design used in this effort. This is similar to one suggested in the Application Note 1009 from Hewlett-Packard [Ref. 5]. One minor change was incorporated to allow for adjustment of forward current across the Light Emitting Diode (LED). This was done to allow for "tuning" of the intensity on the LED to match the optical coupling characteristics of the link as well as to prolong the life of the LED.

## B. SPECIFIC SOFTWARE ROUTINES

Program development for this effort was performed manually. Top down design was accomplished followed by flow charting, coding, assembly, and finally, linking and loading (EPROM programming). This process was tedious and time consuming. More user-friendly software development tools would have been beneficial.

The software can functionally be broken down into six routines. Each of the routines will be discussed along with their associated flow charts. Five of the routines are for the five modes of operation. The remaining routine performs the Restart and Initialization functions.

Fiber Optics Driver Circuit

Fiber Optics Receiver Circuit

Figure 15. Fiber Optics Receiver/Driver Circuitry [Ref. 5]

Specifically, the routines are:

- 1. Restart/Init

- 2. TSTPAT

- ECHOMODE

- 4. Par ByPass

- 5. Par Std

- 6. SerMode

Each routine is independent and forms a module. Each module, except the Restart/Init and TSTPAT routines, have a corresponding Interrupt Service Routine. To facilitate understanding and be succinct, only a brief discussion of each module will be presented. Complete program listings with comments are included in Appendix B.

## l. Restart/Init

This module performs memory and port initialization as well as mode selection functions. All memory is cleared and Port 1 is zeroed. The Timer/Counter constant is loaded and the Mode Switch is read. The selected mode causes the flags FØ and F1 to be set or cleared appropriately. Control is then passed to the selected mode routine. Flow charts are shown in Figure 16a and 16b.

#### 2. TSTPAT

This module generates a test pattern of alternating ones (ls) and zeros (Øs) with an appropriate terminal address and command word. As implemented here, sixteen data words are transmitted each time the Timer/Counter interrupt occurs. This mode of operation is useful for hardware checkout as well as fiber optic link connectivity analysis. Used in conjunction with the EchoMode on a second board, a complete loop can be evaluated for proper operation. A flow chart is given in Figure 17.

Figure 16a. Flow Chart for the INIT Routine

Figure 16b. Flow Chart for the RESTART Routine

Figure 17. Flow Chart for the TSTPAT Routine

#### 3. ECHOMODE

As mentioned above, this mode of operation could be used to test a complete fiber optic link loop. It could also be used to boost an optical signal on a extended link in a relay fashion. The module basically detects a command word addressed to it and echos the word along with associated data words back to the originating device (in this implementation), or to a third party board (if the Terminal address was changed). It could also be used in a delay-insertion loop configuration. A flow chart is included in Figure 18.

### 4. ParBypass

This is the least complex and fastest mode of operation. Data is not buffered in the AC8748 but passed directly to the Shift Register for input to the HD15530 chip. This module does, however, read in the command word and mask out the Word count. It saves the word count in a register for use as an event counter. The parallel bypass process begins by loading the 16-bit input port with a command word containing the terminal address and the number of words to transfer. The AC8748 reads in the command word and extracts the word count. It transmits the command word via the HD15530 chip, and then enters a wait mode pending loading of the next (first) data word. Upon detection of the next data word, it transfers the word directly to the HD15530 Shift Register and enables the encoder with a Data Sync. This process iterates until the word count is exhausted. It then returns and waits for the next sequence. A flow chart is given in Figure 19.

Figure 18. Flow Chart for the ECHOMODE Routine

Figure 19. Flow Chart for the ParBypass Routine

#### 5. ParStd

Data Buffering is provided for in this module. Parallel data is read into a buffer area within the AC8748 and transmitted out after the entire block is buffered. The sequence begins by reading the command word, masking out the word count and saving it in the buffer. The buffer pointer is incremented and the next (first) data word is read in and buffered. This process iterates until the word count is exhausted. The maximum word count is limited to 18 decimal 16-bit words. This is due to the limited memory on board the AC8748. This mode of operation is useful when the external parallel device is slower than the fiber optic link. A flow chart is given in Figure 20.

#### 6. SerMode

There may be a requirement to provide for Serial input/output of data to the fiber link. An example might be a First-In-First-Out (FIFO) chip which can be loaded and read serially (such as the AMD 2813 FIFO). This module allows such an interface. The serial data can be directly loaded into or read from the Shift Registers by an external device. A point to recognize is that the word count must still be read on the LSH of the parallel port. The addition of one chip to the design could eliminate this peculiarity. The sequence begins by latching the word count on the parallel port. The AC8748 reads the word count and saves it in a register. The AC8748 then enables the Serial Control Input Strobe gate and awaits the loading of 16 bits of serial data. It then activates the HD15530 encoder with a Command sync, decrements the word count, and waits for the next 16-bit data word. Then the encoder is enabled with a data sync and the module returns for the next serial data word.

Figure 20. Flow Chart for the ParStd Routine

This process continues until the word count is exhausted. Following this, the module returns to the beginning for the next serial sequence. A flow chart is given in Figure 21.

#### C. INTERFACING AND TESTING

#### 1. Z-8000 Evaluation Board

A means of demonstrating and verifying the completed design was needed. To address this issue the Zilog Z-8000 Evaluation Board from Advanced Micro-Devices (AMD-Z8000) was used. The Z-8000 Evaluation Board provided the requisite parallel I/O port and could operate at speeds fast enough to exercise the design properly. Resident on board was also a Line-by-Line Assembler for program development. It provides an RS232 port to interface to a dumb terminal for entry and display. A Commodore VIC-20 was configured to perform like a dumb terminal and interfaced to the Evaluation board.

The characteristics of the Evaluation board include: a Z-8000 16-bit microcomputer chip operating at 4 MHz; 8 kilobytes of RAM; up to 12 kilobytes of EPROM where the monitor and Line-by-Line Assembler resides; two programmable Serial I/O ports; and a 24-bit programmable I/O port. Additionally, it plugs into the Intel Multibus on which the design was based.

#### 2. Parallel Interface Ports

The system design was accomplished on an Intel Multibus Prototype board using power, clock and databus lines to conform with the bus. As such, the 16-bit parallel I/O port was interfaced to the Multibus bus on the specified Data Bus lines. Additionally, the Constant Bus Clock pin

Figure 21. Flow Chart for the SERMODE Routine

was utilized to provide a clocking source to the /4C8748 and the HD15530 chip. The Z-8000 board had to be interfaced to this bus to act like a standard Multibus Card. To accomplish this, a plug-in card was fabricated to take 16 lines from the Z-8000 Evaluation board's parallel port on P3 to the data bus on the Multibus back plane. Handshaking was provided via additional pins on the Multibus address bus. This is summarized in Figure 22.

## 3. Built-In-Test Function

One possible use for the MIL STD-1553 board could be connectivity analysis of a fiber optic link. An example would be the validation of a newly installed branch on an existing Local Area Network (LAN). It might be impractical to use two workstations on the existing network to check out the new branch on the LAN. The Built-In-Test function (BIT) incorporated on one of the MIL STD-1553 boards answers this need. Because the complete design was built on one multi-bus prototype board, it could be portable. With a battery pack to power the board, remote checkout of a fiber optic branch would be relatively simple as well as thorough.

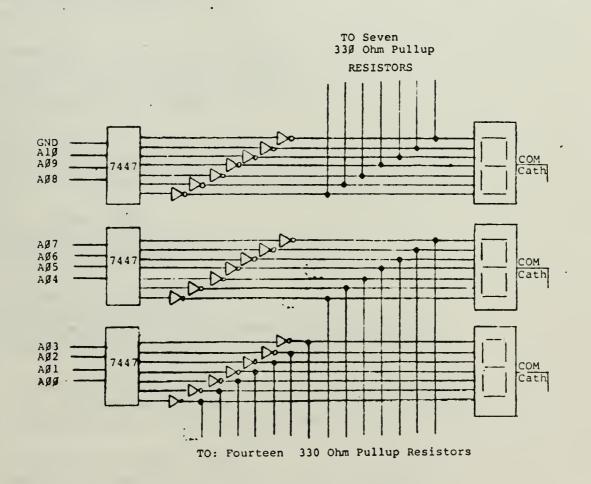

To accomplish the BIT function, two seven-segment displays along with decoder/drivers were built on one of the boards. The inputs to the decoder/drivers were connected to the Least Significant Half (LSH) latch of the parallel output port. The Output Enable (OE) of this latch was strapped in the "on" state. The Latch Enable (LE) was strapped to port 1 bit 7 of the /4C8748. Also included on this board was a momentary switch which was strapped to port 2 bit seven of the /4C8748. This circuitry is

Figure 22. Z-8000 Evaluation Board to Mil Std-1553 Card Parallel Interface

quite similar to the display portion of the Single Step and Display card given in Appendix C.

A flow chart of the BIT software routine is shown in Figure 23. As can be seen from the figure, the sequence of events begins by reading a pseudo-random byte from the free-running timer/counter. The Terminal Address byte is then concatenated with the pseudo-random byte to form a 16-bit Command Word for output to the HD15530 Encoder. Then the Encoder is enabled to transmit this Command Word across the fiber optic link. At this time a wait mode is entered pending arrival of the echoed word from a second board configured in the "Echo Mode". Upon arrival of the echoed word the BIT sequence reads the pseudo-random byte and compares it to the original byte transmitted. If the two bytes compare, a "word counter" is incremented and output to the seven segment displays. The software routine then enters a loop pending detection of closure of the momentary switch, at which time the sequence repeats.

By performing the above, a fiber optic link can be evaluated for connectivity. The procedure described above could be accomplished by technicians with minimal experience and verifies proper operation at a link with a fair degree of confidence. This capability was used to arrive at the results presented in Chapter VI.

Figure 23. Flow Chart for the Built-In-Test (BIT) Routine

#### V. DESIGN DEVELOPMENT TOOLS

Any task undertaken with this degree of complexity requires tools and aids to make the job manageable. More efficient tools and aids usually yield quicker and more accurate results. As much of this effort was accomplished while separated from the academic environment with its laboratory and tools, support equipment had to either be borrowed, bought, or fabricated. The first item to be procured JDR Instruments Dual Trace Oscilloscope. This, by far, was the most critical tool. Another critical tool was the Intel Prompt-48 programmer to "burn" the software into the /4C8748. The NPS staff graciously loaned this item for an extended period of time. Late in the design stages, it became evident that some sort of single step and display device was required to debug the software and check out the hardware. MCS-48 Family of Single Chip MicroComputers User's Guide [Ref. 4] provided a single step circuit for use with the MC8748. This circuit was incorporated on a plug-in card containing seven-segment displays and decoder/drivers. The plug-in card interfaced to the Mil Std-1553 cards via the Multibus backplane to provide single step and display capability. The final tool was to incorporate strapping options in the design to allow the plug-in card to access the data bus and address bus of the NC8748. More efficient tools are available and would have reduced the development time considerably. For example, an Assembler with a linking loader that would interface to the Prompt-48 and download assembled and linked code (machine code) for programming the MC8748 would have been

beneficial. A Logic State Analyzer would also have been helpful. Discussion of the available tools and their utilization follows.

#### A. THE PROMPT-48 PROGRAMMER

This unit allows for entry of the assembled machine code into its internal memory. This can be accomplished a couple of ways. The quickest and easiest is to load the memory with the machine code from a preprogrammed /4C8748. This is useful in latter stages of development when only minor changes and additions to the code are required. If none of the original program exists, then entry of the machine code can be done using the keypad functions. This method is tedious at best. Once the coding has started, new codes should be placed so as to not overwrite the existing code. This requires sufficient allocation for each program module to permit future modifications without overwriting existing code which would require a manual relinking and loading. Once the code is resident in the Prompt-48 memory, it can be viewed and edited and finally programmed into the target /4C8748.

# B. SINGLE STEP AND DISPLAY CARD

As mentioned in Chapter II, the C8748 design facilitates single stepping through program memory. The Single Step function can be accomplished as mentioned above. Figure 24 shows this circuit along with three-seven segment LED displays with the requisite BCD to Seven Segment Decoders/Drivers (7447). With this circuit, the next address, which appears on the databus and port 2, can be displayed and executed one instruction at a time. The timing diagram for this circuit is also given in Figure 24. This card became very useful late in the development for

#

Figure 24. Timing Diagram for the "Single Step and Display" Card [Ref. 4]

debugging the software and verifying the hardware. For example, a module could be single stepped through until the interrupts were enabled. At that time, an interrupt could be simulated by momentarily grounding the interrupt pin and then single stepping could resume to verify proper Interrupt Service Routine execution.

#### C. STRAPPING OPTIONS FOR TESTING

In order to use the plug-in card with a Mil Std-1553 card, the Mil Std-1553 card has to be strapped to allow the Address Latch Enable (ALE) signal to latch the address into the Most Significant Half (MSH) of the parallel port to display this address on the plug-in card for Single Step and Display. Additionally, the Output Enable for the MSH of the parallel port has to be tied low to allow for continuous display. Further, the Single Step pin on the AC8748, which would normally float high, should be strapped to the Single Step output pin on the plug-in card.

When the Single Step and Display card is not being used, the ALE strap should be removed and the parallel latch strobe strap should be connected. The Single Step pin on the / C8748 should be allowed to "float". This relationship is shown in Figure 25.

In normal operation, the following conditions should exist:

- 1. ALE unconnected

- 2. Single Step unconnected

- 3. Parallel Latch Strobe (MSH) should be strapped

The most valuable tool was the Single Step and Display plug-in card, since program debugging was possible with this card. The Prompt-48 was

Figure 25. Strapping Options for Testing

essential for programming the /UC8748 after the code was developed. The oscilloscope was very useful in verifying hardware operation.

During development, the fiber optic link was disabled to prevent damage and proper operation was restored once the hardware and software designs were complete. A copper wire was used to link the two cards' Mil Std-1553 interfaces for testing purposes.

#### VI. SYSTEM RESULTS

The goal of this study was to demonstrate the implementation of Mil Std-1553 using a fiber optic link. This goal was achieved with qualifications. The first qualification is that strict compliance to Mil Std-1553 could not be achieved in some modes of operation. For example, in the Parallel Standard mode, only 18 words could be transferred due to the limitation of the internal RAM on the AC8748. Another example of non-compliance is the requirement for Status word to be transmitted not more than 3 microseconds after receipt of a frame of data. This capability was not included from the start in an attempt to limit the scope of this effort and thus to limit the time required to complete it. Several other Mil Std-1553 requirements were waived to facilitate reasonable time to completion and completion with limited resources.

The concepts of fiber optic implementation of Mil Std-1553 were sufficiently demonstrated to validate the feasibility of this approach. BiPolar Manchester II encoded data with proper sync and parity bit were successfully transferred over a fiber optic link in sufficient quantity and quality to demonstrate few or no barriers to full development of this concept.

#### A. MAXIMUM DATA RATE

As mentioned in the text, the fastest data transfer rates can be accomplished in the Parallel Bypass mode and the slowest rates appear in the Parallel Standard Mode. The slower rates are caused by the

requirement to divert the data into a buffer storage area internal to the /uC8748. Several additional instruction executions are required as can be seen from the program listings and flow charts. Handshaking requirements are doubled as can be seen from the control circuitry. The Serial mode transfer rate is comparable to the Parallel Bypass mode. Essentially, the same number and types of control signals exist in these two modes. The number of instructions in the critical loops are roughly equal except that in the Serial mode fewer instructions are needed due to hardware that handles some of the functions.

The maximum rates, therefore, will be based on the Parallel Bypass mode. Table 3 contains the maximum data rates for calculated and observed rates. The observed data rates are slower because both the \(^{12}\cap{C8748}\) and the HD15530 chip were not clocked at their maximum rates. The calculated data rates are based on assumed maximum clocking rates for these devices and the number of instruction cycles required (worst case) times the minimum instruction times.

TABLE 3

MAXIMUM DATA RATES (CALCULATED AND OBSERVED)

| Unit                 | Maximum Data Rate<br>Calculated/Specified | <u>Observed</u>   |

|----------------------|-------------------------------------------|-------------------|

| / <sup>1</sup> C8748 | 147 Kilobits/sec                          | 134 Kilobits/sec  |

| HD-15530             | 1.56 Megabits/sec                         | 1.36 Megabits/sec |

| HFBR 0500 Link       | 5 Megabits/sec                            | 1.36 Megabits/sec |

| Total System:        | 147 kilobits/sec                          | 134 Kilobits/sec  |

The maximum data rates are not affected by either the HD15530 chip nor the fiber optic link because these devices are rated at higher than the requisite 1 Megabit data rate.

#### B. INTERFERENCE/EMANATION AND ISOLATION

The greatest advantage of fiber optics lies in their ability to be immune to RFI and EMI. An added benefit involves total electrical isolation. A further benefit is the extremely high data rates offered by fiber optics. The coupled benefits of high data rates, RFI and EMI immunity, and electrical isolation suggest that fiber optic communication channels approach the ideal communications channel. Prior to fiber optics, it was not possible to route communication links through fuel tanks, in close proximity to generators and high power equipment, or in water of any kind (underwater cables are hermetically sealed). Fiber optic links are unaffected by these environments. The mere weight of copper wire (large enough to carry information) is much greater than the weight of a fiber optic link capable of carrying significantly more information per unit of time.

Another area in which optical fibers proves superior to copper wire is data security. A typical copper wire channel carrying digital data can be tapped without making any contact with the conductor itself. In fact, many copper wire channels radiate in free space enough to be detected and compromised at a considerable distance. This is referred to as compromising emanations. Fiber optics on the other hand cannot be easily tapped nor do they radiate in free space in the RF spectrum.

Applications which require high data security are already incorporating fiber optics because the alternative copper wire approach requires RFI shielding and physical security efforts which are very expensive compared to the improved data security payoff.

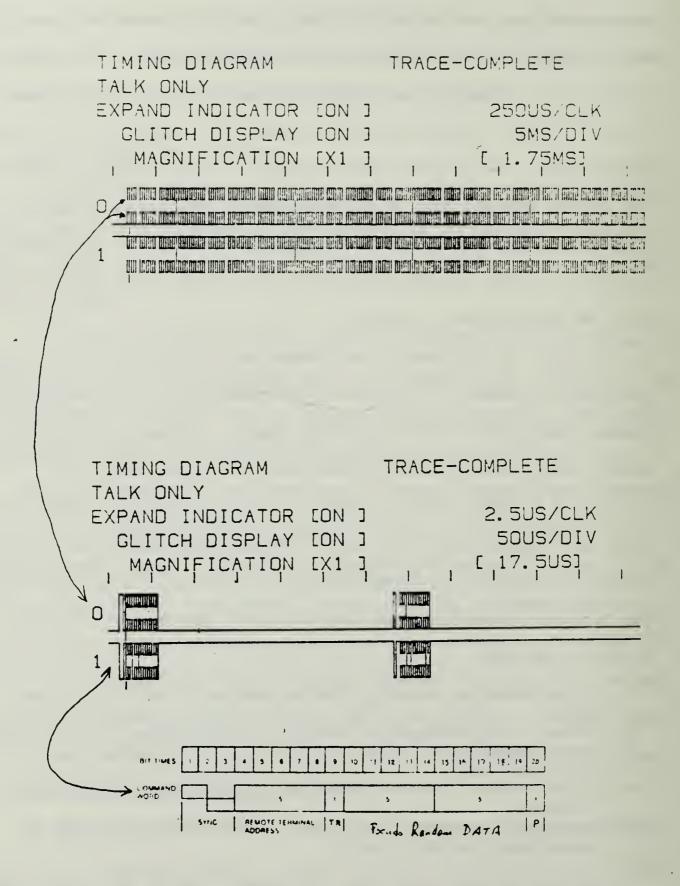

#### C. BUILT-IN-TEST (BIT) RESULTS

As mentioned in Chapter IV, the BIT capability was used to obtain some results that graphically demonstrate the operation of the design. The configuration required to obtain the results will be briefly described here.

To establish a complete loop, one MIL STD-1553 board was placed in the "Echo Mode" configuration and the second board (containing the seven-segment displays) was set up for the BIT function. Two optical fibers were used to interconnect the board to provide a closed loop.

When the push button was depressed (or held) a pseudo-random byte was concatenated with the Terminal Address to form a Command Word containing pseudo-random data. The word was transmitted across the link to the "Echo Mode" board. This board, in turn, echoed the word back to the originating board completing the circuit transfer. If both the transmitted Command Word and the echoed Command Word compared, the word count was incremented and displayed. When the pushbutton was held down a continuous stream of Command Words containing pseudo-random data were transmitted, echoed, and compared.

A means of plotting some results for inclusion here was desired. This was accomplished using a Hewlett-Packard 1641 (HP1641) Logic State Analyzer interfaced with a plotter via the Hewlett-Packard Bus (HPIB).

Two of the input channels of the HP1641 were connected to the transmit and receive pins on the HD15530 chip. The HP1641 External Clock input was connected to the HD15530 clock for synchronization. The HP1641 was triggered by connecting its External Trigger input to the Interrupt pin on the /4C8748. This was done to detect the arrival of the echoed Command Word. The trigger would occur only if the echoed word contained the correct Terminal Address and was properly received as a Command Word with correct parity and Manchester Bipolar encoding. A high degree of confidence in the proper operation of both cards using optical fibers could be demonstrated in this way.

The plot of the results are presented in Figure 26. Each pulse indicated on Channel Ø represents the transmission of a pseudo-random Command Word from the transmitting board. Channel 1 indicates the receipt of a properly echoed Command Word from the echoing board.

As can be seen from the Figure for this particular sample period there were approximately 115 20-bit Command Words containing 8 bits of random data successfully transmitted and echoed back. As mentioned above the following conditions must exist to have generated each of the 115 pulses in the plot:

- 1. Proper encoding, decoding, and re-encoding of all 20 bits per word.

- 2. Correct Parity generation, detection, and checking of all 20 bits.

- 3. Proper regeneration of the bit clock on both receiving ends of the fiber link.

- 4. Proper Terminal Address generation and detection on both ends (4 bits).

- 5. Successful generation, detection, and comparison of 8 bits of random data per 20-bit word.

There were no data "drop-outs" indicated in any of the plots produced during the design validation tests performed. This result should be

Figure 26 Built-In-Test (BIT) Results

qualified by the following. The validation test was performed using two MIL STD-1553 cards - one in the Echo Mode and one in the "BIT" mode. Two HFBR0500 Series Snap-In Optical Fiber Links were used that were each approximately 20 feet long. The forward current across both HFBR1501 transmitters was adjusted to match the characteristics of the optical fibers to ensure reliable optical transmission and reception on both ends of the link. The two MIL STD-1553 cards were powered by separate power supplies with no common ground connected. Thus, the boards were optically isolated.

A simple procedure was used to match the HFBR1501 transmitters to the optical fibers. An oscilloscope probe was placed on the "Valid Word" pin of the HD15530 chip to sense the receipt of a correctly encoded Manchester word containing the proper parity bit. Then one board was placed in the "Test Pattern Generation" mode and the second board in the "Echo" mode. The forward current potentiometers on both boards were adjusted to ensure proper reception of the 16 words transmitted and echoed by the TSTPAT software routine. Once this was accomplished, the plots mentioned above were generated and the results obtained.

#### VII. CONCLUSIONS AND RECOMMENDATIONS

#### A. CONCLUSIONS

Fiber optic implementation of Mil Std-1553 has been accomplished in this effort in a relatively non-rigorous fashion. The basic concepts, however, have been demonstrated tenaciously. A relatively sound application of the standard has been implemented. Some general conclusions can be drawn from this study.

- 1. Implementation of Mil Std-1553 using fiber optics in airborne avionics is a reasonable approach.

- 2. The requisite fiber optic interface is simple and lends itself to many general applications.

- 3. The physical handling of the fiber optic cable during the course of this study was not overly sensitive—therefore, fiber optic cable installations can survive reasonable human environments. The critical parameter when handling fiber optics is the bending radius. Once this bending radius parameter is exceeded, cracking of the plastic or glass medium sets in and performance begins to degrade.

- 4. The data rate requirement of Mil Std-1553 (1 MBps) can be met and exceeded using fiber optics.

- 5. Data security applications requirements can be readily addressed with fiber optics.

- 6. Fiber optic cables are relatively light and therefore lend themselves to weight-critical applications such as space.

#### B. RECOMMENDATIONS

As mentioned above, the design tested was a relatively non-rigorous approach. Because it was non-rigorous, the conclusions drawn above are reasonable. Throughout this study, several design alternatives surfaced. They are summarized below.

1. The AC8748 was acceptable for the purposes of this effort. It was a limiting factor in a few ways. First, the 8-bit wide data bus required a double read and write to transfer 16-bit words. Second, in the Parallel Standard mode, the buffer storage allocation was less than called for in Mil Std-1553. Third, the program execution time was one of the contributors to a slower data rate.

Recommendation: For higher speed data transfer environments, an alternative 16-bit microcomputer chip with more internal RAM should be selected.

2. A Very Large Scale Integration (VLSI) implementation of this design is well within current technology. The size, weight, and power consumption could be significantly reduced with VLSI technology. More intelligence could be designed in to incorporate all of the functions of Mil Std-1553. This would also facilitate much higher data transfer rates.

Recommendation: Develop and fabricate a custom VLSI implementation of this design using CAD/CAM technology for further study.

3. The fiber optic cable used in this design was single mode plastic core large diameter fiber. Much higher data rates and reliability could be achieved using small diameter glass fibers with laser excitation devices. Fifty megabit data rates are currently being achieved with higher quality fibers and driver/receivers.

Recommendation: For military and industrial applications, the use of higher quality fibers and drivers/receivers is suggested. The cost of these items is steadily falling because production techniques are rapidly improving.

4. The design as presented here is functional and could be used in general Local Area Networks as it exists. The data block size could be easily increased from 32 sixteen-bit words to 256 sixteen-bit words in either the Parallel Bypass mode or the Serial mode.

Recommendation: Consider using this design or a similar design for Local Area Networks environments that are susceptible to RFI and/or EMI.

#### APPENDIX A

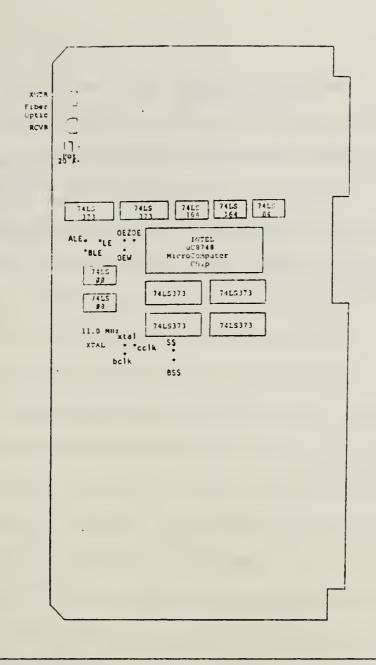

### MIL STD 1553 CARD LAYOUT AND DISCUSSION

The integrated circuits and discrete components used in the design were mounted on an INTEL Prototype board in a particular fashion. The intent was to keep the Mil Std-1553 peculiar components on one side of the board to allow expansion and customizing the design for particular applications. As an example, the Built-In-Test (BIT) function was added on one of the Mil Std-1553 cards. Figure Al gives this arrangement. Note that the BIT function components are shown in the dashed area of the figure.

The remaining area might be used to incorporate a First-In-First-Out (FIFO) buffer in a Multibus environment or any of a number of other uses.

The Mil Std-1553 peculiar components were also placed in such a way as to:

- 1. Minimize the data bus line lengths.

- 2. Isolate the clocking circuitry from other sensitive components.

- 3. Reduce much of the locally generated noise interactions.

Figure Al. Mil Std-1553 Card Chip Placement

Figure A2. Complete Card Schematic for Mil Std-1553 Card

#### APPENDIX B

## SOFTWARE LISTINGS: /4C8748 MICROCOMPUTER CHIP

This Appendix contains the complete assembled listings for all of the software routines resident in the on-chip EPROM of the /C8748. It is organized in the following format:

- 1. A brief synopsis of the routine.

- 2. A definition for each of the variables used.

- 3. The beginning and ending hexidecimal addresses for the routine.

The intent here is to permit easy replication of any or all of the modes of operation as desired. If only one or two modes are implemented, it may be appropriate to "re-link" the various routines to provide more cohesive and compact code and room in the program memory for additional software.

As mentioned in the "RECOMMENDATIONS" section, more user-friendly development tools would reduce software buildup and checkout time significantly.

### Synopsis:

Entry into this routine is accomplished via a "power-on" restart or "reset". When power is first applied, the /\(^1\)C8748 begins program execution at location "00" hexidecimal. At this location, a jump to the initialization routine was placed. At location 003 hexidecimal, the /\(^1\)C8748 expects to find the external interrupt service routine. A jump to the interrupt service routine was placed here. The /\(^1\)C8748 expects to find the Timer/Counter interrupt service routine at location 007 hexidecimal. The actual interrupt service routine was placed here to generate the test pattern words for the TSTPAT routine.

#### Variable Definitions:

INIT - Title of the initialization routine.

EXTINT - Location of the external interrupt service routine.

INTERPT - Title of the interrupt handling routine

TIMINT - Title of the Timer/Counter interrupt Service Routine

NXTWD - Location of the "wait for encoder done" loop.

## Routine Linkage:

| Name    | Begin | End | (addresses are in hexidecimal) |

|---------|-------|-----|--------------------------------|

| PWRRST: | 000   | ØØ1 |                                |

| EXTINT: | 003   | ØØ4 |                                |

| TIMINT: | 007   | Ø39 |                                |

### **PWRRST**

| addr       | opcode/addr | label  | mnemonic         | Comments                      |

|------------|-------------|--------|------------------|-------------------------------|

| 000<br>002 | 0440        | PWRRST | JMP INIT         | JMP to INIT Routine           |

| 003<br>005 | 4400        | EXTINT | JMP INTERPT      | JMP to External INIT Routine  |

| 007        | 65          | TIMINT | STOP TIMER       | Timer Interrupt Routine       |

| 008        | D5          |        | SEL RBl          | Select Register Bank 1        |

| 009        | B9ØE        |        | MOV Rl',#ØE      | Load Reg 1 with # of Words    |

| ØØB        | B820        |        | MOV RØ',#20      | Load Reg Ø With Buffer Addr   |

| ØØD        | 9900        |        | ANL P1, #00      | Clear Port 1                  |

| ØØF        | FØ          |        | MOV A, @Rع       | Get Low Byte of Command Word  |