ער זיין גריין גריין אר מיעס עראיין גריין גריין גריין גריין גריינט אראין גריין גר

# NAVAL POSTGRADUATE SCHOOL Monterey, California

# THE FORMAL SPECIFICATION OF COMPUTER SYSTEMS

by

Klaus Karrasch December 1987

Thesis Advisor:

Daniel Davis

T239027

Approved for public release; distribution is unlimited.

# ICLASSIFIED

|                                                                                      | REPORT DOCU                  | MENTATION                                      | PAGE                      |                         |          |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------|------------------------------|------------------------------------------------|---------------------------|-------------------------|----------|--|--|--|--|--|--|--|

| PORT SECURITY CLASSIFICATION                                                         |                              | 16 RESTRICTIVE MARKINGS                        |                           |                         |          |  |  |  |  |  |  |  |

| Lassified                                                                            | 3 DISTRIBUTION               | 3 DISTRIBUTION / AVAILABILITY OF REPORT        |                           |                         |          |  |  |  |  |  |  |  |

|                                                                                      |                              |                                                | for publi                 |                         | <b>;</b> |  |  |  |  |  |  |  |

| CLASSIFICATION / DOWNGRADING SCHEDU                                                  |                              | ion is un                                      |                           | -                       |          |  |  |  |  |  |  |  |

| FORMING ORGANIZATION REPORT NUMBE                                                    | R(S)                         | 5 MONITORING ORGANIZATION REPORT NUMBER(S)     |                           |                         |          |  |  |  |  |  |  |  |

| ME OF PERFORMING ORGANIZATION                                                        | 60 OFFICE SYMBOL             | 78 NAME OF MONITORING ORGANIZATION             |                           |                         |          |  |  |  |  |  |  |  |

| 1 Postgraduate School                                                                | (if applicable)<br>Code 52   | Naval Postgraduate School                      |                           |                         |          |  |  |  |  |  |  |  |

| DRESS (City, State, and ZIP Code)                                                    | L                            | 7b ADDRESS (City, State, and ZIP Code)         |                           |                         |          |  |  |  |  |  |  |  |

| erey, California 9394                                                                | 3 - 5000                     | Monterey, California 93943-5000                |                           |                         |          |  |  |  |  |  |  |  |

| ME OF FUNDING / SPONSORING                                                           | BD OFFICE SYMBOL             | 9 PROCUREMENT                                  | INSTRUMENT ID             | ENTIFICATION N          | IMBER    |  |  |  |  |  |  |  |

| GANIZATION                                                                           | (if applicable)              | 9 PROCUREMENT INSTRUMENT IDENTIFICATION NUMBER |                           |                         |          |  |  |  |  |  |  |  |

| DRESS (City, State, and ZIP Code)                                                    |                              | 10 SOURCE OF FUNDING NUMBERS                   |                           |                         |          |  |  |  |  |  |  |  |

|                                                                                      |                              | PROGRAM<br>ELEMENT NO                          |                           |                         |          |  |  |  |  |  |  |  |

| SONAL AUTHOR(S)<br>asch, Klaus<br>PE OF REPORT<br>er's Thesis<br>PLEMENTARY NOTATION |                              | 14 DATE OF REPO<br>1987 Dec                    | at (Year, Month)<br>ember | 0ay) 15 PAGE<br>129     | COUNT    |  |  |  |  |  |  |  |

|                                                                                      |                              |                                                |                           |                         |          |  |  |  |  |  |  |  |

| COSATI CODES                                                                         | 18 SUBJECT TERMS             |                                                |                           |                         |          |  |  |  |  |  |  |  |

| D GROUP SUB-GROUP                                                                    | Formal Speci<br>Computer Res | sources, Ti                                    | Petri net<br>ming of C    | , Abstrac<br>Computer S | Systems  |  |  |  |  |  |  |  |

|                                                                                      |                              |                                                |                           |                         |          |  |  |  |  |  |  |  |

| abstracted compute                                                                   | ntroduction<br>r resources   | of form<br>, both p                            | hysical                   | and logic               | cal,     |  |  |  |  |  |  |  |

| there is the poss<br>made toward deve                                                |                              |                                                |                           |                         |          |  |  |  |  |  |  |  |

| portability and                                                                      | reusability                  | costs                                          | of compu                  | ting sys                | stem     |  |  |  |  |  |  |  |

| components. Still,                                                                   | the current                  | methodolo                                      | gy is on                  | ly concer               | rned     |  |  |  |  |  |  |  |

| RIBUTION / AVAILABILITY OF ABSTRACT                                                  |                              | 21 ABSTRACT SECURITY CLASSIFICATION            |                           |                         |          |  |  |  |  |  |  |  |

| CLASSIFIED/UNLIMITED SAME AS RI                                                      | DTIC USERS                   |                                                |                           |                         |          |  |  |  |  |  |  |  |

| E. Daniel Davis                                                                      |                              | (408) 646-3091 Code 52DV                       |                           |                         |          |  |  |  |  |  |  |  |

|                                                                                      | ledition may be used u       |                                                |                           | CLASSIFICATION          |          |  |  |  |  |  |  |  |

|                                                                                      | All other editions are o     | bsolete                                        | UNCL                      | ASSIFIED                |          |  |  |  |  |  |  |  |

19. ABSTRACT (continued)

with the static functional properties of resources and not their timing properties. This places limitations on the generality of the method. This study describes a way to formally specify the timing of computer systems by combining ideas of both semantic algebras and Petri Nets.

S-N 0102- LF- 014- 6601

Approved for public release; distribution is unlimited.

The Formal Specification of Computer Systems using Petri Nets

by

Klaus Karrasch Lieutenant, Federal German Navy

Submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN COMPUTER SCIENCE from the

NAVAL POSTGRADUATE SCHOOL

December 1987

#### ABSTRACT

1 153

21

With the introduction of formal specification of abstracted computer resources, both physical and logical, there is the possibility that a major step forward can be made toward developing a methodology for reducing the portability and reusability costs of computing system components. Still, the current methodology is only concerned with the static functional properties of resources and not their timing properties. This places limitations on the generality of the method. This study describes a way to formally specify the timing of computer systems by combining ideas of both semantic algebras and Petri Nets.

# TABLE OF CONTENTS

-

| Ι.    | INTE | RODUCTION                                          | 7 |

|-------|------|----------------------------------------------------|---|

| 11.   | BACK | <pre><ground< td=""><td>_</td></ground<></pre>     | _ |

|       | Α.   |                                                    | 0 |

|       |      | 1. Syntax versus Semantics 14                      |   |

|       | в.   | PETRI NETS                                         |   |

|       |      | 1. Terminology of Petri Nets                       |   |

|       |      | 2. Properties of Petri Nets                        | 1 |

|       |      | 3. Modeling with Petri Nets                        | З |

|       |      |                                                    | _ |

| 111.  |      | E PROBLEM OF TIMING SPECIFICATION                  | _ |

|       |      | GENERAL PROBLEMS                                   | - |

|       | в.   | SPECIFIC PROBLEMS OF INTEREST                      |   |

|       |      | 1. Order of Evaluations of Functions 2             |   |

|       |      | 2. Parallel Processing of Parts of Functions . 2   |   |

|       |      | 3. Mutual Exclusion                                |   |

|       |      | 4. Data Flow                                       | 8 |

| 1.1/  | 4001 | LICATIONS OF PETRI NETS TO THE TIMING IN FORMAL    |   |

| 1 V . | APPL |                                                    | ~ |

|       |      | SPECIFICATIONS                                     |   |

|       | Α.   | GENERAL APPROACH                                   |   |

|       | в.   | NOTION OF SUBNETS                                  |   |

|       | C.   | COMBINING NETS                                     |   |

|       |      | 1. Coupling of Nets                                |   |

|       |      | 2. Extensions of Nets                              |   |

|       |      | 3. Net Selection                                   |   |

|       | D.   | TYPING OF NET ELEMENTS                             |   |

|       |      | 1. Typed Places                                    |   |

|       |      | 2. Typed Tokens                                    | 8 |

|       |      | 3. Typed Tokens in Typed Places                    | 8 |

|       | E.   | SYNTAX                                             | 9 |

|       |      | 1. Places                                          | 1 |

|       |      | 2. Transitions                                     | з |

|       |      | 3. Properties                                      | 4 |

|       |      | 4. Initialization                                  | 5 |

|       |      |                                                    |   |

| ۷.    |      | ABSTRACT PROCESSOR TIMING SPECIFICATION 40         |   |

|       | Α.   | ATOMIC NETS                                        | 7 |

|       | в.   | MODELING OF MEMORY AND REGISTER ACCESS TIMING . 44 | 8 |

|       | с.   | MODELING OF INSTRUCTION FETCH AND EXECUTION        |   |

|       |      | TIMING                                             | 7 |

|       | D.   | MODELING OF INTERRUPTS                             | 5 |

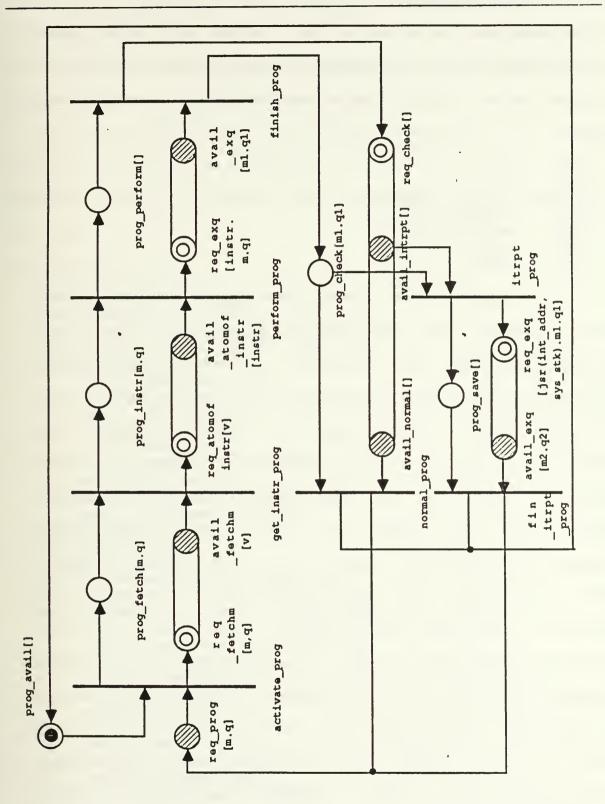

|       | Ε.   | EXECUTION OF PROGRAMS                              |   |

|       |      |                                                    |   |

| VI.   |      | 1ARY AND CONCLUSION                                |   |

|       | Α.   | ADVANTAGES                                         |   |

|       |      | 1. Ability to State Asynchronuous Timing 75        |   |

|       |      | 2. Ability to Show Dataflow in a System 7!         | 5 |

|          |      | Abili |      |     |     |      |      |      |    |     |    |     |    |    |   |   |   |   | 75  |

|----------|------|-------|------|-----|-----|------|------|------|----|-----|----|-----|----|----|---|---|---|---|-----|

|          | 4.   | Abili | ity  | to  | Мо  | del  | Mut  | ua l | E  | xcl | us | ior | n  |    |   |   |   | • | 75  |

| в.       | DISA | DVAN  | ΓAGE | S   | •   | • •  | • •  | •    | •  | • • | •  |     |    |    |   |   |   |   | 76  |

|          | 1.   | Compl | lexi | ty  | •   | • •  | • •  | •    | •  | • • |    |     |    |    |   |   |   |   | 76  |

|          |      | Diffi |      |     |     |      |      |      |    |     |    |     |    |    |   |   |   |   | 76  |

| с.       | FURT | HER F | RESE | ARC | СН  | TOP  | ICS  | •    | •  | • • |    |     |    |    | 0 |   |   |   | 76  |

|          |      |       |      |     |     |      |      |      |    |     |    |     |    |    |   |   |   |   |     |

| APPENDIX |      |       |      |     |     |      |      |      |    |     |    |     |    |    |   |   |   |   |     |

|          |      | THE A | ABST | RAC | СТ  | PROC | CESS | SOR  | •  | • • |    |     |    |    |   | • |   | • | 78  |

|          |      |       |      |     |     |      |      |      |    |     |    |     |    |    |   |   |   |   |     |

| APPENDIX | B:   | COMPL | JETE | SF  | PEC | IFIC | CAT  | ON   | OF | A   | SU | BSI | ΞT | OF | - |   |   |   |     |

|          |      | THE A | ABST | RAC | СТ  | PROC | CESS | SOR  | •  |     |    | •   |    | •  | • |   |   | • | 112 |

|          |      |       |      |     |     |      |      |      |    |     |    |     |    |    |   |   |   |   |     |

| LIST OF  | REFE | RENCE | ES . |     | •   | • •  | • •  | •    |    |     | •  |     |    |    |   | ٠ | • |   | 126 |

|          |      |       |      |     |     |      |      |      |    |     |    |     |    |    |   |   |   |   |     |

| INITIAL  | DIST | RIBUI | ΓΙΟΝ | L   | ST  | •    |      | •    | •  |     |    | •   |    | •  | • | • |   | • | 128 |

# I. INTRODUCTION

computer systems has been a critical issue Timing in throughout the evolution of computers. The most obvious areas where timing is of great concern are operating systems, distributed systems and real-time systems. In the most other timing of a computer program is taken for granted areas. we assume a simple sequential execution of this since program. But we have to realize that, when we consider the program and the machine on which it has to run as a whole, a computer system, we have to deal also with the i.e. internal timing of the hardware. Even though high level provided us with the means to programming languages have software from one system to another, we still find these programs may not work properly because of timing problems. These timing problems are normally caused by different implementations of computer resources. So It would be very helpful to have a way of comparing computer systems and predicting problems in timing when programs are transferred. It would even be much better to have specifications of computer systems that could be used to design transferrable programs in the first place.

There is ongoing research at the Naval Postgraduate School on the formal specifications of computer systems that is mainly intended to overcome the increasing costs of

computer software resulting from problems with portability and reusability of programs. The first result of this research project has been the development of a formal specification methodology by Davis (1984). This methodology was successfully used to write a formal specification of an Abstract Processor by Yurchak (1984).1 This work was followed by several extensions of the Abstract Processor and related work by Hunter (1985) and Zang (1985). The research performed at the Naval Postgraduate School is part of a relatively new branch of computer science: the Science of Computing System Design which is concerned with a formal approach to the specification and description of computer systems. This thesis follows the direction of previous work done in this field. Its objective is to formally specify timing in computer systems. Even though there has been considerable interest in timing, our approach will emphasize two aspects of the problem:

- We want to develop a formal way to specify timing to achieve the benefits of the rigorous foundation of a formal description.

- We want to specify abstracted resources which include both hardware and software with a unified approach.

Throughout this thesis the term "computer resources" is used in a sense that combines all hardware and software building blocks of computer systems: memory, registers, data types, instructions, etc.. Also the special aspect we are

<sup>&</sup>lt;sup>1</sup>An edited version of the specification of the Abstract Processor is included in Appendix A

concerned with is time as a computer resource. Computer resources can be either pure physical or they can be an abstract type. A memory cell belongs to the physical category while a specific data type belongs to the abstract category. The means to deal with these differences is abstraction. Specifying computer resources as abstractions in a mathematical way also allows us to compare different specifications and implementations.

Within this work we will emphasize a practical viewpoint. Even though in applying pure mathematical concepts to computer systems we realize that computers are in no way ideal: as every piece of hardware is finite (especially the memory) and an event in the computer is never instantaneous but will take a certain amount of time. In this context, for example, the term "digital computer" is misleading since there are many undefined states between those defined "0" and "1".

Therefore the goal of this thesis is to provide a methodology for the rigorous specification of timing:

- to evaluate the time behavior of systems which leads to the exhibition of possible places in system where parallelism could be used,

- to give a better understanding of the dynamic aspect of computer resources in time, and

- to find time critical situations in a system.

# II. BACKGROUND

# A. FORMAL SPECIFICATION

The idea of specifying a system formally is to deal with physical and abstract computer resources as abstractions to support our major concerns with portability and reusability. In this sense we deal with computer resources as abstractions which we want to describe such that the functions and the properties of a resource are stated in a mathematical way to support precision and provability. Studies in this direction have been conducted by many researchers (Goguen (1978). Guttag (1978), Bergstra (1983), and Davis (1984)). As a short introduction to this work we would like to present some key they were used in the first formal issues here as specification of the Abstract Processor.

The formal specification of the Abstract Processor is based on the method of algebraic specification which consists of two parts: the interface specification and the constraints specification. The interface specification declares operands and the operators that can be applied to them, so information for syntactic constructions and type checking are provided. The constraints specification is a set of properties that define constraints on the operations. These properties are stated by equations that associate the same meaning to pairs of expressions of the specification. As an example the

specification of the computer resource "boolean" is shown in

Figure 2.1.

```

Resource boolean is

Operands

bool

Operators

not: bool -> bool;

and: bool,bool -> bool;

true: -> bool;

false: -> bool;

Properties

not(true()) = false();

not(not(x)) = x;

```

```

not(not(x)) = x;

and(true(),x) = x;

and(false(),x) = false();

```

end boolean;

Figure 2.1: Specification for Resource "boolean"

Figure 2.1 illustrates the definition of one operand type (bool) and the operations (not, and, true, false) that are allowed with this operand. The operations are stated as functions with their input and output. Note here that the constants resembling "true" and "false" are obtained from the nullary operator functions with no input ("true()" and "false()"). Up to this point only the interface part is considered. The meaning of the specification is indirectly in the form of equations that state that certain expressions must be treated identically to other expressions. The above equations use "x" as a free variable, i.e. "x" stands for any

expression that can represent an operand of type "bool". So far this computer resource "boolean" is an abstract data type in the traditional meaning. But computer resources also consists of physical resources which are very similar to abstract data types in their specification. Figure 2.2 provides an example of specifying a physical computer resource to indicate the memory state of the Abstract Processor. For simplicity only the operands for initialization, fetching and storing are presented. The first interesting fact to note in this specification is that it states that the resource "amstate" is an extension of the previously defined specifications of the resources "boolean", "memaddress", and "regaddress", i.e. all operands, operators, and properties defined in these specifications can be used to specify "amstate" without further explanations. The operand "state" has in this example four operators to initialize the processor, to fetch from memory and registers, and to store to memory and registers. The properties for these operations are shown by equations that indicate their relations among Note that this example uses the term "undefined" to them. indicate an error or don't care condition (the attempt to fetch the contents of an register or memory address of a new initialized processor is illegal).

The basic step in becoming familiar with formal specifications is to consider the well-known constructs of abstract data types: a class of objects together with a set

of operations that may be applied to these objects. This approach can also be applied to physical computer resources.

```

Resource amstate is

```

```

Extension of

boolean,

memaddress,

```

regaddress,

# Operands

state;

```

Operators

```

```

fetchm: memaddr,state -> val;

fetchr: regaddr,state -> val;

storem: val,memaddr,state -> state;

storer: val,regaddr,state -> state;

initam: -> state;

```

# Properties

```

fetchm(a, initam()) is undefined;

storem(fetchm(a, q), a, q) = q;

implies(eqmemaddr(a1, a2),

fetchm(a1, storem(v, a2, q)) = v)

= true();

implies(not(eqmemaddr(a1, a2),

fetchm(a1, storem(v, a2, q)) = fetchm(a1, q))

= true();

fetchr(r, initam()) is undefined;

```

```

storer(fetchr(r,q),r,q) = q;

implies(eqregaddr(r1,r2),

fetchr(r1,storer(v,r2,q)) = v)

= true();

implies(not(eqregaddr(r1,r2),

fetchr(r1,storer(v,r2,q)) = fetchr(r1,q))

= true();

```

end amstate;

Figure 2.2: Specification of "amstate"

Then we have concrete algebras which describe an aggregate of operations and sets of values where the sets are the source for arguments and result types of each operation. This is a system in which there are sets and operations that are applied to elements of the sets such that the results of the operators stay in the system. When construct a we system, specification of such a we attempt to create a specification that serves as templates for the sets and operators in a concrete algebra and axioms which state provable equations about the values and operations. With such have something which describes the a specification we resource abstractly and precisely without restricting it to a specific concrete algebra, i.e. there can be many algebras that are implementations of a single specification. They are considered as the class of algebras uniquely associated to that specification.

# 1. Syntax versus Semantics

We refer to the syntax of description as the "form" of the description and to semantics as the "meaning" of the description.

The meaning is always determined by associating form to real objects. Basically the syntactic part describes legal expressions that can be formed with the operators in the specification. These expressions are called **formal terms**. The constraint part specifies that certain formal terms are to be considered equivalent. The meaning of specifications is

established by associating certain concrete algebras to the specification. There algebras represent the "real object". Operational expressions in the concrete algebras are called **actual terms**. Semantics are defined by a correspondence between properties of formal terms and actual terms. A real object is a realization of the abstract object defined by a specification under three conditions as they are stated in Davis and Yurchak (1984):

- Condition 1:

For each operand type of the specification there is a corresponding set of values in the real object and to each operator in the specification there is a corresponding operation in the real object that is defined on values that correspond to the operand types of the operator.

- Condition 2: In the correspondence between formal terms and actual terms, two formal terms are provably equal if and only if their corresponding actual terms have the same value.

- Condition 3: To every value of the real object there must correspond some formal term whose corresponding actual term has that value.

These conditions provide us with a powerful insight: given a formal specification of some resources there can be different implementation in the real world (as they probably are on different machines), but as long as the implementations satisfy the above conditions they are equivalent. This is a very important property when the issue of portability is concerned.

Still an formal specification despite its abstract view of resources has to deal with the real world: for

example there is nothing like true infinite memory so that a defined operator like "nextmemaddr" (to obtain the memory address of the next instruction to be executed) will eventually exceed the physical implemented memory of a system. The "undefined" has been introduced in the formal specifications to act like a safeguard. It indicates that there is no interpretation in the realization for this term.

# B. PETRI NETS

Petri Nets are tools for the study of systems through modeling. The Petri Net theory has been originally introduced by Carl Adam Petri in his doctoral dissertation (1962). Further studies of A. W. Hold and Jack B. Dennis helped to develop this theory.

# 1. Terminology of Petri Nets

From Peterson (1981) a basic Petri Net is defined as a five-tuple M = (P,T,I,O,m) which is composed out of the following parts:

- a set of places P

- a set of transitions T

- an input function l

- an output function O

- a marking vector m

The function l is a mapping from a transition t, to a collection of input places  $O(t_s)$  and the function O is a mapping of a transition t, to a collection of output places  $I(t_s)$ , the marking vector m indicates the number of tokens

preset in each place. In this general form, developed by C.A. Petri, a place can hold more than one token at a time.<sup>2</sup>

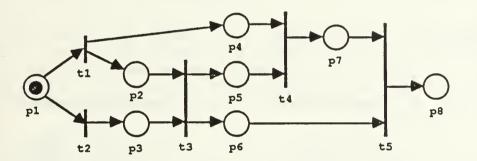

As an example, the following net structure is presented here and Figure 2.3 shows its corresponding graph in the common symbology of Petri Net graphs where circles indicate places, bars indicate transitions, and arrows show the connections between places and transitions:

```

M = (P, T, I, 0, m)

P = \{p_1, p_2, p_3, p_4, p_5, p_6, p_7, p_8\}

T = \{t_1, t_2, t_3, t_4, t_5\}

m = (1, 0, 0, 0, 0, 0, 0, 0)

I(t_1) = \{p_1\} \qquad 0(t_1) = \{p_2, p_4\}

I(t_2) = \{p_1\} \qquad 0(t_2) = \{p_3\}

I(t_3) = \{p_2, p_3\} \qquad 0(t_3) = \{p_5, p_6\}

I(t_4) = \{p_4, p_5\} \qquad 0(t_4) = \{p_7\}

I(t_5) = \{p_6, p_7\} \qquad 0(t_5) = \{p_8\}

```

Figure 2.3: Graph of Petri Net

The following Petri Net terminology is used in this thesis:

- place = a construct for modeling conditions of the system

- event = actions that take place in the system

- token = a construct used to indicate that a condition holds (a true condition)

<sup>2</sup> The reader is referred here to the BAG theory

- transition = the process of recognizing true preconditions, the occurrence of an event, and making the postconditions hold

- concurrency = two or more events depending on different

preconditions can occur in any order

- conflict = only one of two or more events depending on at least one common precondition can occur

To give a simple description of Petri Nets we can say the following: An event occurs (a transition is initiated or enabled) when all of its preconditions hold. The effect of the occurrence is that the tokens of the preconditions are "used" for the event and then distributed to the postconditions.

The following constructors can be recognized in Petri Nets:

- simple transitions = there is one precondition and whenever this condition holds the event occurs so that the token from the precondition is removed and after the occurrence of the event the token is moved to the postcondition so that this condition now holds (Figure 2.4).

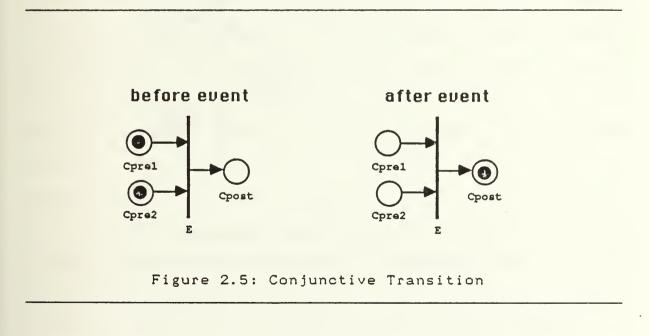

- conjunctive transitions = there are two or more preconditions that all have to hold in order for the event to occur. All tokens of the preconditions are used and after the occurrence of the event only one token is moved to the postcondition to indicate that it now holds (Figure 2.5).

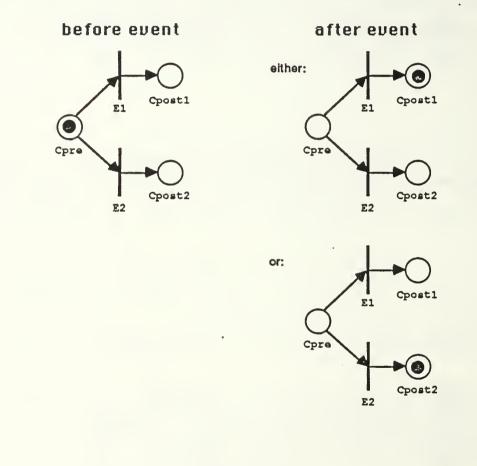

- disjunctive transitions = one precondition is connected to two or more events and when this precondition holds one of the events will occur and will move the token from the precondition to the postcondition of that event that occurred. The selection of the event to occur is non=deterministic (Figure 2.6).

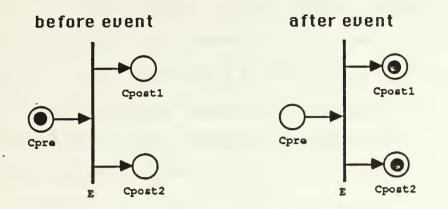

- distributive transitions = there is one precondition and when this holds the connected event will occur. It will remove the token from the precondition and it to all postconditions so that every postcondition of this event will have a token (Figure 2.7).

- complex transitions = combinations of the above simple constructs of Petri Nets.

Figure 2.4: Simple Transition

Figure 2.6: Disjunctive Transition

Figure 2.7: Distributive Transition

# 2. Properties of Petri Nets

Petri Nets by their nature are well suited to model asynchronuous processes, i.e. where the progress of a process is controlled by conditions and events and not by some kind of fixed clock. This means that in some part of the net there can be waiting for a condition to start an event, even the case that a process cannot continue because of a missing condition. Suppose an event is modeled as a conjunctive transition as indicated in Figure 2.5. If the precondition C,... is never true the process will stop at this point. The "flow" of the progress can always be observed by the state of the condition places in the system. The occurrence of events is recognizable by the changing of the preconditions and postconditions.

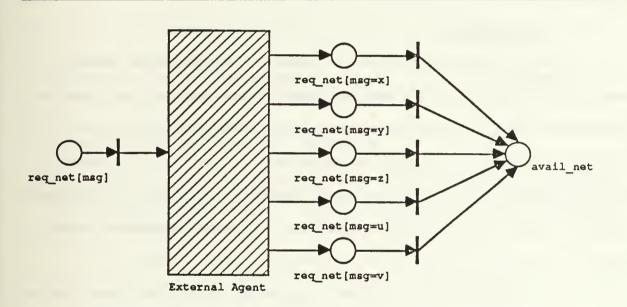

The discussion of disjunctive events has shown an important property of Petri Nets: their non-deterministic nature, i.e. we have under normal circumstances to force a distributive construct in one or the other direction. This is a major obstacle when we have to model some kind of decision making in a Petri Net. One way to get around this problem is the construct (introduced by Peterson (1981)) of an "external agent" which provides appropriate TRUE or FALSE places at decision points in the net. Here by the intervention of the "external agent" the process proceeds in the direction of the TRUE or FALSE place. In general, one can think of "external as CASE-constructs in high-level programming agents" languages such that, dependent on the value of an argument, one and only one action is taken by setting the according place in the net. We will discuss this topic further in Chapter IV.

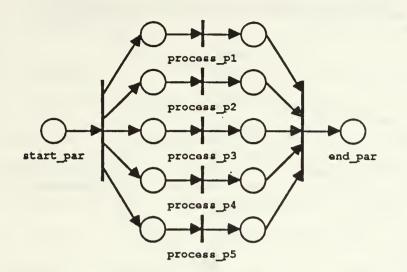

When we look at the conjunctive and distributive constructs we observe that by combining them we can build a distributive construct which "fans" out into several holding places and then combines again with a conjunctive construct. In this way, we have able to introduce **parallelism** into Petri Nets. Figure 2.8 shows the graph of a process that fans out into five processes which then merge again into one process. This capability of Petri Nets is very powerful and convenient in specifying computer resources.

Figure 2.8: Parallelism with Petri Nets

# 3. Modeling with Petri Nets

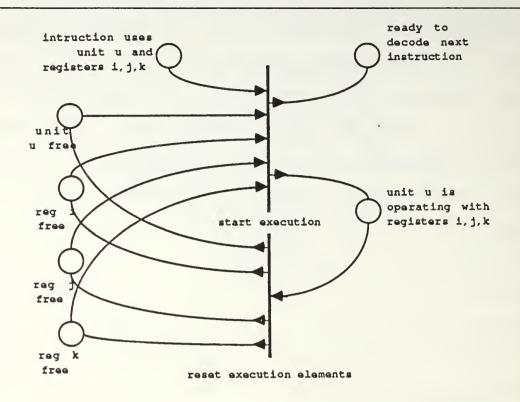

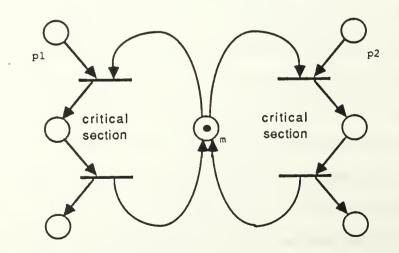

Modeling with Petri Nets has been widely used in very different areas: computer software, computer hardware, chemical reactions, queuing theory, political systems, etc.. Two examples as they are presented by Peterson (1981) are given to illustrate this modeling work: a portion of a Petri Net showing a control unit of a computer with multiple registers and functional units as an example for modeling computer hardware (Figure 2.9) and a Petri Net dealing with the mutual exclusion problem as example for modeling computer software (Figure 2.10).

In our approach we want to exploit the ease and the properties of Petri Nets for modeling the combination of computer hardware and software as they operate in time.

Figure 2.9: Computer Control Unit

Figure 2.10: Mutual Exclusion

# 111. THE PROBLEM OF TIMING SPECIFICATION

# A. GENERAL PROBLEMS

Why are we so concerned about the timing of a system? Time is an important resource in computer systems that must be managed carefully. There is almost always the possibility that if we invest more of other resources we are able to reduce the amount of time a piece of work will need. Everybody remembers a mathematical problem like this: if it takes one unit to accomplish a task in x hours how many hours will it take y units to do the same task? In this very simple problem the increase of other resources (e.g. units) will reduce the needed time for the task linearly. In computer systems we could save time by implementing more CPUs, disk drives, arithmetic units, etc.. But since more hardware costs more money and the control of additional resources uses time by itself we have to be very careful in determining the resources we need and how we use them. The following example shows the danger of mismanaging computer resources: a computer task that requires some resources (e.g. disks) would waste them if it holds more than it needed at times when it actually does not need them and so prohibits other tasks from using them.

The formal specification as described in the specification of the Abstract Processor is only concerned

with static computer resources, i.e the timing properties are implied by the functional relations between components of the system. The static specification is purely functional. For example, operands must be evaluated before a function is applied but there is no way of indicating the order of evaluation. The dynamic computer resources are those that express an ordering of resources in time, mutual exclusion and concurrency. Instead of assuming some ordering in the use of computer resources we want to be able to explicitly state and define the timing of a system.

The goal is to specify the required timing properties precisely to a desired degree which for example is sufficient to evaluate the system for time and cost efficiency. The relation between time and cost depends on the nature of the system: there is much more emphasis on time in system that are very time critical (e.g. real-time systems) and not so much on systems that are purely problem solvers.

The basis of this work is to show whether such a methodology for specifying timing properties can be based on the theory of Petri Nets and how well the special cases of timing in computer system resources can be expressed in terms of Petri Nets.

# B. SPECIFIC PROBLEMS OF INTEREST

#### 1. Order of Evaluations of Functions

Given a function  $f(x_1, x_2, ..., x_n)$  we only require that x<sub>1</sub> to x<sub>n</sub> are evaluated before f can be applied.<sup>3</sup> There is no statement that the evaluation of x<sub>1</sub> has to be started first or what evaluation has to be completed first.

# 2. Parallel Processing of Parts of Functions

Considering again our function  $f(x_1, x_2, ..., x_n)$  we want to state explicitly which evaluations have to performed in parallel and which in sequence. Why do we want to do so? Following our purpose, in the specification we want to describe timing in a way which is as exact and detailed as a timing diagram used to construct hardware.

# 3. Mutual Exclusion

A major problem that arises with parallelism is mutual exclusion, i.e. a computer resource can only be used by one process at a time and the use of the resource has to have a certain entry and exit point to preserve the integrity of the resource.

Consider a simple computer with a memory unit which retrieves and stores data on request via a specified interface (Memory Buffer Register and Memory Address Register). This is parallelism even in simple computers since the memory is independent from the CPU. So we have to make

<sup>&</sup>lt;sup>3</sup>Even if x is a constant it has still to be evaluated, i.e. its value has to be retrieved

sure that only one request is handled by the memory unit at a time and that the next one is handled when the first one is finished. We want to be able to explicitly state those properties in the specification of timing systems.

4. Data Flow

During the course of a process in time certain data has to be available in order for the process to proceed. Some data is changed, other data is not needed anymore. Here we have the problem of how to model data flow by means of Petri Nets.

To make this point more clear let us consider the execution of following instruction: SUB R1,R2 (subtract the contents of register 1 from the contents of register 2 and store the result in register 2). During the execution we have to retrieve the identities of the registers from the instruction (i.e. the instruction has to be decoded) then their contents both have to be available before we can perform the subtraction. At this point of the execution we do not need the identity of the first register anymore, but the one for the second since it is not only a source for the operation but also the destination. Thus, we have to have some mechanism in our methodology to state data which is available during the course of the execution.

# IV. APPLICATIONS OF PETRI NETS TO THE TIMING IN FORMAL

#### SPECIFICATIONS

In previous work computer resources have been formally specified using basically the algebraic specification approach. In essence, this is a type of functional specification. The question we address here is can functional specification be extended, using Petri Net theory, to provide for the specification of timing properties.

# A. GENERAL APPROACH

Given a general function  $f(x_1, x_2, \ldots, x_n)$  what are the stages of evaluation for this function?

- the evaluation of  $f(x_1, x_2, ..., x_n)$  must have been requested from somewhere and by this the evaluation gets into a requested stage

- for all x<sub>i</sub>, 1 <= i <= n, the evaluation is requested which starts for all x<sub>i</sub> a new process with the same stages as described here

- once all x, are evaluated and their results are available to our function f it can be evaluated in a processing stage

- when the evaluation is completed and the result is available the process is completed

Note the similarity to the "natural" way a human being would calculate this function: if we were to calculate  $sum(sin(x^2), sqrt(y))$  we had to calculate the square root of y and we had to square x and take the sine of it and then we would apply the sum-function to the intermediate results.

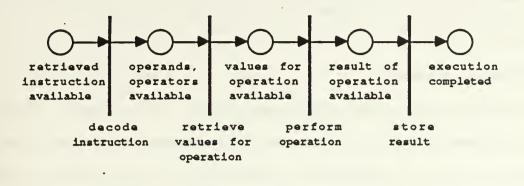

However, this example exhibits a problem for our very general approach: how do we know what the values of x and y are and how do we know that e.g. "sqrt" means "take the square root". Therefore there must be some decoding and retrieval steps in between which determine what the parts of the function expression mean. This is exactly the case when we consider computer instructions: e.g. given an instruction like "ADD R1 M2 R3" which means "add the contents of register 1 to the contents of memory address 2 and store the result in register 3". Here the following steps have to be performed:

- The instruction has to be decoded (we assume that at this stage the instruction is already retrieved): i.e. the components of the instruction (operator and operands) must be made available to the further evaluation.

- Up to this stage only the names (i.e. the symbolic addresses) of the operands are available and so the next step is to retrieve the values of the operands.

- Now that the operator and the values of the operands are available the operation designated by the operator can be performed.

- When the result is available it can be stored into the location which expressed by the third operand.

Figure 4.1 shows the corresponding graph of a Petri Net describing the above steps. In this example we see an approach to describe the execution of an instruction in a sequential manner. Suppose we had a machine that could perform retrieval of values and operation in parallels, how could we describe that certain steps could be performed in parallel and how could we mark points in time where the process can only proceed if some results are available?

Figure 4.1: Simple Instruction Execution Net

This is the point where we can use the properties of Petri Nets: if we model requests and availabilities as places of Petri Nets and the actions on requests and availabilities as transitions and connect them accordingly we are in a position to model the evaluation of a function or the execution of an instruction.

Up to this point there is nothing new in our methodology since modeling with Petri Nets is common practice and has been done for a long time. The question to be ask now is does a methodology based on Petri Nets provide the means to specify the specific problems of computer systems and their components in a way that is consistent with the formal specification of the static properties we have seen in the specification of the Abstract Processor.

In addition we not only want to look at the timing of systems in an isolated fashion, but also we want to combine the specification of static properties, as introduced in the

specification of the Abstract Processor, with the specification of dynamic properties of such a system. With this combination we can specify systems completely.

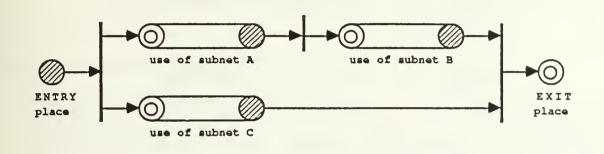

# B. NOTION OF SUBNETS

Now that we have Petri Nets as a tool we can model simple timing systems using our methodology. However, we would like to simplify and eliminate redundancy: if we use the same structure in a net several times, it would be better to have this structure defined once and reference this definition wherever we need it in our system (Figure 4.2). As an example, suppose we realize that a structure to make the contents of a certain memory address available to the process appears several times in our system. By defining this retrieval-function as a subnet we are in a position to use it everywhere in the system simply by setting its ENTRY-place (in our example with a request for value of a specified register) and we obtain the result (the value of the specified register) at its EXIT-place. This works even for the case that the subnet specifies a computer resource that has to be accessed observing mutual exclusion.

The major question that has to be asked here is how can we model such a subnet that has the ability to "sense" where it has been invoked and so can return its results to that location in the system. Computer language constructs like procedures or functions use a return address which is saved with the call of the procedure/function to determine the

location in the program which has to be executed after the procedure/function is finished. Our model of using Petri Nets is different in this aspect: despite the fact that it shows the dynamic behavior of a system, its structure is static and does not change in time and so all connections between nets and subnets are established. Since we have to know all these

# Figure 4.2: Symbology of Subnets

connections we are able to provide for each connection an entry-place which is connected to the net internally by disjunctive events such that only one can be "fired" at a time. The "firing" of those events lets a path-place hold that indicates the entry-place which triggered the event. This path-place decides what exit-place is set when the internal net provides the result.

This definition of a subnet is a very powerful shortcut for keeping descriptions of systems limited. It resembles a function construct in a high-level programming language: it is been "called" by setting its request-place, does its

supposed work and "returns" the result as the available-

place.

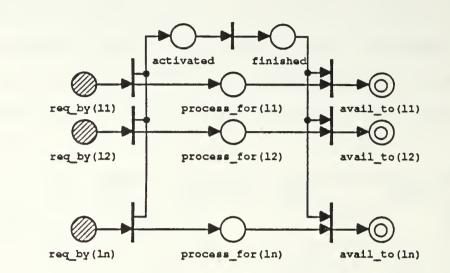

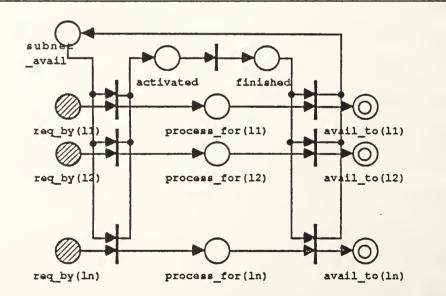

Figure 4.3: Generalized Subnet without Mutual Exclusion

Figure 4.4: Generalized Subnet with Mutual Exclusion

We have to show that our methodology is capable of defining subnets and introducing them into other nets.

C. COMBINING NETS

With the introduction of subnets we are in need of rules and guidelines on how we can combine a collection of small nets and subnets into a timing system.

#### 1. Coupling of Nets

In the preceding paragraph we have assumed that nets are connected by entry and exit places, but generally, we have two possibilities to connect nets:

- Coupling by places: to connect two nets the first net outputs to a EXIT-place that is read by the second net as an ENTRY-place. In the special case that we use subnets in our specification we request the subnet by place (the ENTRY-place of the subnet) and obtain the result by a place (the EXIT-place of the subnet).

- Coupling by events: events are shared between nets and when the ENTRY-event "fires" the requested net is invoked and signals the availability of the result by "firing" its EXIT-event.

We have chosen the coupling of nets by places because

of the following reasons:

- The request for a subnet submitted by a place allows the requested subnet more "liberty" to react on the request only when it is ready to do so since the pending request as a "loaded" place remains until it is used by the net, where as in event-coupling the saving requests had to be done in a more complicated way.

- The coupling of nets by places resembles the way events like interrupts are processed in real machines, here the interrupt does not interrupt the execution of instructions at any time, but a status "interrupt" is set and this status is checked between the execution of instructions and acted upon.

# 2. Extensions of Nets

To make our methodology consistent we need to state what other nets we are going to use in this net. There is a close similarity to INCLUDE, USE or WITH constructs of highlevel programming languages or the EXTEND construct of the formal specification. In the specification of timing the mentioning of a net to be the extension of another means that the parent net is going to use the extended net as a subnet in the specification.

# 3. Net Selection

Due to the non-deterministic nature of Petri Nets we do not have a traditional net construct which can make decisions on truth or falseness and directs the path in the net accordingly. A proposed solution for this problem by Peterson (1981) is to use "external agents" as they were presented in Chapter 2. This construct is able to examine a status or data on a given condition and make the decision whether the condition is fulfilled. With the outcome of the decision a path to a place representing true or the place representing false is set. By extending this idea we able to think of "external agents" as a CASE-statement where one and only way through the net is chosen according to a condition (see Figure 4.5).

#### D. TYPING OF NET ELEMENTS

In the traditional Petri Net theory we have tokens to indicate the flow through the net and to mark holding places.

So the "firing" of an event consists in collecting a token from each of the connected input places, performing the designated action and distributing a token to each connected output place. This is not enough when we want to describe the flow of data in time. Also we want to be able to state specifically what kinds of data, what types of data are being requested, available or transferred at a certain point in the timing of a system.

Figure 4.5: Net Selection by "external agents"

How can we show the presence of data in our methodology? On first sight we have two possibilities: either we introduce a typed place or a typed token. Both of these constructs could indicate the presence of certain data. So we to examine both methods under the consideration which of them suits our goal better to develop a practical and understandable methodology.

### 1. Typed Places

When we introduce a concept of typed places we still have the original meaning of the tokens to indicate the holding of a place. The presence of data of a certain type must be accomplished by means that have to obey the type of the place. The events still react on the presence of tokens in the places.

#### 2. Typed Tokens

This alternative considers a token as a construct that carries an actual piece of data according to the type of the token. We can imagine tokens as a message residing in the places. The events now can be modeled by picking up a message from each connected input placed, performing their designated actions, and distributing a message to every connected output place.

So now we can look at places in a net as constructs that can receive token-messages from events, keep them and send them to events. The actions performed by events consist of picking up message-tokens from places, changing and creating message-tokens and sending them to places.

# 3. Typed Tokens in Typed Places

Both concepts above exhibit some disadvantages:

- Pure place typing needs some external mechanism to establish the presence of data.

- Pure token typing allows a message-token to be sent to every place in the net since there no protection from receiving message-tokens of the wrong type.

This leads to the idea of combining both typing schemes. With this concept we restrict places in the net to accept only tokens of a certain type and the tokens are actually typed messages. One small problem does arise here: what if we want in some situations the token to have its original meaning only to indicate its presence without any data? This reminds of a message without contents. As a solution we introduce following typing convention:

- A place declared to be of a certain type or collection of types can only accommodate tokens that are messages of this type or collection of types.

- A place declared to be of no type can only accommodate tokens which are "empty" messages.

- An event will collect typed token-messages from the connected typed input-places, perform its designated action and output typed token-messages to the connected typed output-places.

With this typing scheme we are now in a situation to specify data flow in time by means of typed tokens and places. Although we have based our work on Petri Nets we see that our concept has become more general and now reminds of a general message passing system.

# E. SYNTAX

Since our approach includes the existing specification methodology of the static computer resources, we have to carefully develop a new syntax which expresses both the static and dynamic properties of the systems to be specified.

The following syntax has been introduced with the specification of the Abstract Processor by Davis and Yurchak (1985):

Resource <name> is Operand Types <operand types> Operators <operators> Properties <properties>

The following requirements have to be fulfilled by the syntax we want to develop:

- It has to have the ability to express both the static and dynamic properties of system properties where the static part should be left in the form as introduced by Davis and Yurchak (1984).

- The form of the syntax should be as simple and easy to understand as possible.

- The chosen names of the constructs of the syntax should be self-explanatory and suggest the intended meaning to the user.

- It has to provide a precise and unambiguous way to specify the system.

Another point to consider is that we want to follow certain accepted design principles, especially that of Information Hiding as it is done e.g. in the ADA package construct where there is a Package Interface (to provide the user of the package with all the information necessary to use the package and nothing else) and a Package Body (the implementation of the package).

Before we finalize the syntax for the dynamic specification of a system we need to say something about how the dynamic properties of static objects are described in

40

-

places and transitions. Places reflect the of terms conditions on the execution of the static functions, whereas transitions are used to describe changes in these conditions during the execution of the static functions. Some of these places and transitions are generic. i.e. they apply to any function. For example, a function is always requested by a place and becomes activated by an activate-transition. This does not prevent us from defining additional places and transitions when they are needed for a specification. We are going to use an uniform notation to indicate the connection between the statement of the dynamic properties and the static properties. Given an operator storem : val. memaddr. state -> state we will use internal places names that are preceded by storem\_ (e.g. storem\_activated) and transition names that are followed by \_storem (e.g. activate\_storem). We also reserve standard notations for entry and exit places of subnets: entry places are always preceded by req (e.g. req\_storem for "request a store in memory") and exit places are always preceded by avail (e.g. avail storem for "result of store in memory is available). We reverse the order of attaching the name of the function because we want to emphasize that a subnet represents a transition that is specified in detail.

# 1. Places

There are three types of places we want to distinguish in our syntax:

- internal places, which names and definitions are only known and accessible within the net they are defined in; the purpose is to build the internal structure of the net

- entry places, which names and definition are also known and accessible to those nets which are declared to be extensions of this net; they provide an interface to invoke this net

- exit places, which names and definitions are known and accessible to those nets which are declared to be extensions of this net; they provide an interface to obtain the results from the invocation of this net

We have chosen the following syntax to describe places in our specification:

#### place\_name(netlabel)[message\_type].

A place\_name is the distinct name of a place in the described net. In the case that a place is either an entry or exit place the rule applies that their names are known to those nets which are declared to be extensions of this net. If a net has multiple entry or exit places the parameter netlabel can be attached in parentheses to describe this fact where netlabel indicates a location in the system. As we have said a place is able to accommodate a certain kind of message so the type of the message the place can hold in brackets is part of the place description. The following description of places are legal (compare with the static specification for "fetchr" and "storem" in Chapter II):

- storem\_activated[val.memaddr.state]; a place of the name "storem\_activated" which can hold messages that consist of data of type val, memaddr and state

- fetchr\_avail[]; a place of the "fetchm\_avail" which can only hold empty messages

- req\_pushstk(netlabel)[val.stkaddr.state]; places of the name "req\_pushstk" which are distinguished by the parameter "netlabel", all of them able to hold messages which contain data of types val, stkaddr and state.

## 2. Transitions

Our methodology defines transitions as the process of collecting a message from each connected input place and sending messages to every connected output place. So we want to state what kind of messages are received and transmitted. The following syntax is used to describe transitions: transition name:input messages -> output messages.

The transition\_name is a distinct name for the transition in the net and is not known outside the net. Input and output messages are of the above form where multiple messages are separated by commas. The following examples are legal description of transitions:

- perform\_storem: [val.memaddr.state] -> [state]; the transition of the name "perform\_storem" takes a message which contains data of type val, memaddr and state as input and outputs a message containing data of type state

- finish\_fetchr: [val],[] -> [val],[]; the transition of the name "finish\_fetchr" takes two messages as input where one consists of data of type val and the other is an empty message and outputs again two messages of same type

Note that the description of transitions only declares them in terms of their capabilities to accept and to transmit certain kinds of messages and does not show any internal action of the transition. The reason for this is to present the transitions as building blocks of the net in form of a mapping function which is general enough to provide

information about its interface and nothing more. The internal actions are described as the properties of the net. This does not necessarily means that a transition is instantaneous, rather the complexity of the internal actions determine the duration of the transition. But every complex transition can be modeled as a net with entry and exit places such that the internal transitions become instantaneous.

#### 3. Properties

Now that we have described the building blocks of a net we need to connect them in order to describe the intended timing of a system. The following form is chosen for the syntax of the properties of the net:

#### transition\_name(place\_names[message\_data) =>

place\_names[message\_data]; This form shows how places and transitions are connected and how the transfer of message elements occurs between them. Here are some examples of legal property descriptions:

#### - perform\_fetchm(fetchm\_activated[m.q]) =>

fetchm\_completed[v]; the transition "perform\_fetchm" occurs when there is a message in the place "fetchm\_activated". The message is taken from the place in such a way that all message elements (memaddr m and state q) are available to the transition. Then the action of getting the memory contents is performed and the resulting value v is transmitted as a message to the place "fetchm\_completed"

# - perform\_storer(storer\_activated[v.r.q]) => storer\_completed[q1]; the transition "perform\_storer" occurs when there is a message in the place "storer\_activated" in such a way that the message is taken from the place in such a way that its message elements (value v, regaddr r and state q) are available to the transition. The action of storing the value v in

# register r is performed and the new state q1 is transmitted as a message to the place "storer\_completed"

Functionally, the internal actions performed by transitions follow the rules stated as static properties for the functions involved.

## 4. Initialization

In some kinds of nets we have an internal circuit of places in order to act as a synchronization mechanism (as illustrated in Figure 4.4 to provide mutual exclusion). They have to be initiated somehow i.e. a message has to be placed in at least one of these places since they are not provided with messages from outside the net. We going to describe this initialization by using the symbol "=>" used to indicate the placement of a message into a place. The following is an example of an initialization:

=> fetchm\_avail[]; the place "fetchm\_avail" is loaded with an empty message

The initialization of a place is a one-time action at the beginning of system start and provides the necessary conditions to get a process going. It can be viewed as establishing the initial state of a computer system when it is turned on.

#### V. THE ABSTRACT PROCESSOR TIMING SPECIFICATION

In this chapter we want to present some examples on how specific problems of timing in computer system can be modeled using the methodology in a top-down fashion. The examples resemble a variety of computer system timing problems to test the use of Petri Nets in specifying the timing properties. In Appendix B a complete specification of the static and dynamic properties of a reduced Abstract Processor is presented. We have chosen to use the Abstract Processor as the object to be specified in timing considerations because of the following reasons:

- to emphasis this work as the logical step following the work of specifying static properties of systems,

- by specifying a non-existent, abstracted processor we intentionally leave the issue of the actual implementation untouched since we stated that by whatever means the specification is implemented the processor will have the specified properties,

- to emphasize our intention of specifying what the user of a processor wants to achieve and not how it is implemented as compared to a traditional processor design approach that is dominated by engineering and implementation issues.

Also we want to show how well our methodology can deal with the special aspects of timing in computer systems. The special aspects we are concerned with are mutual exclusion, interrupt processing and concurrency. Despite the fact that the Abstract Processor is in its static part specified as a simple single processor during this work we have realized

that even there, a lot of potential concurrency can be detected.

Whenever we refer to actual implementation we do this with the intention to give one example of how the specification could be realized. Once again we emphasize that the methodology stated in this work is only concerned with what is available in a system and not with the how it is implemented. We want to remind the reader that the methodology developed here is intended to be general. That is, it can be equally applied to the specification of computer resources that may be implemented in hardware, software or firmware. With this in mind we have look at the timing specification not as a blueprint by which a system can be build directly but rather as formally stated requirements a system has to fullfil no matter what approach is chosen for the implementation .

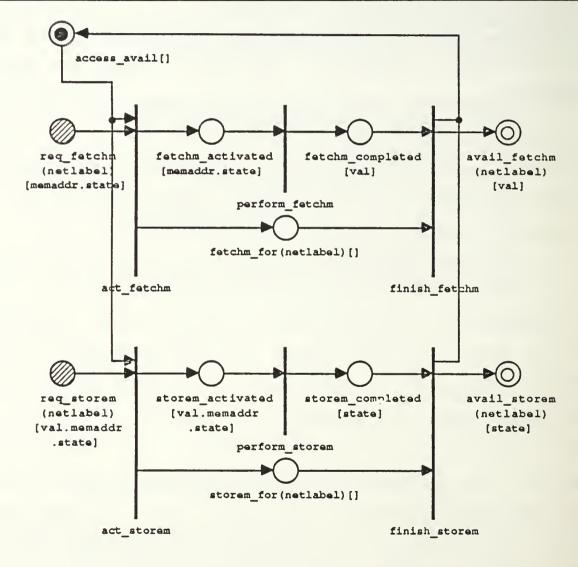

# A. ATOMIC NETS

One feature of the methodology is it forces the specifier to focus on the essential nature of the system components. When we consider these essential components as actions in a system that are not further divisible we can speak of atomic actions which we want to specify as atomic nets in our methodology. Such nets will use no other net in their specification and so can be considered as building blocks of a system. In general they represent the elementary actions in a system. The Abstract Processor consists of several such

elementary actions and to illustrate this idea, we will show how the actions of store operations and fetch operations can be described with atomic nets.

#### B. MODELING OF MEMORY AND REGISTER ACCESS TIMING

The first question we have to ask when we want to specify the access of memory or registers is what kind of information do we have to have available to perform an access and what information we obtain after the access has been made. In order to perform an access the address of the memory cell or register has to be available. Depending whether a store or a fetch has to be performed, we either have to provide a value for this process or we obtain a value from the process. Also, to indicate the current contents of the register or memory cell we have to indicate the process for accessing the state of the processor. In case of a store access we obtain a new state as the result of the process since the change of a memory cell or register also changes the state.

At this stage we have established the components of any process dealing with the access of memory or registers. We anticipate that accesses to memory and registers will be made from various places in the system, so we provide a netlabel for every entry and exit place. In terms of our specification methodology can now define the entry and exit places of the subnet:

- the fetching of the contents of a memory cell is requested by providing message which consists of the

memory address and the state to the following entry

place: req\_fetchm(netlabel)[memaddr.state];

- We obtain as a result a corresponding message containing the value from the exit place: avail\_fetchm(netlabel)[val];

- similarly we state the entry and exit places for fetching the contents of a register: req\_fetchr(netlabel)[regaddr.state]; as the entry place and avail\_fetchr(netlabel)[val]; as the exit place

- the storing of a value into a memory cell is requested by providing a message which consists of the value to be stored, the memory address and the state to the following entry place: req\_storem(netlabel)[val.memaddr.state];

- We receive as a result a corresponding new state from the exit place: avail\_storem(netlabel)[state];

- similarly we define the entry and exit places for storing values into registers; req\_storer(netlabel)[val.regaddr.state]; as the entry place and avail\_storer(netlabel)[state]; as the exit place.

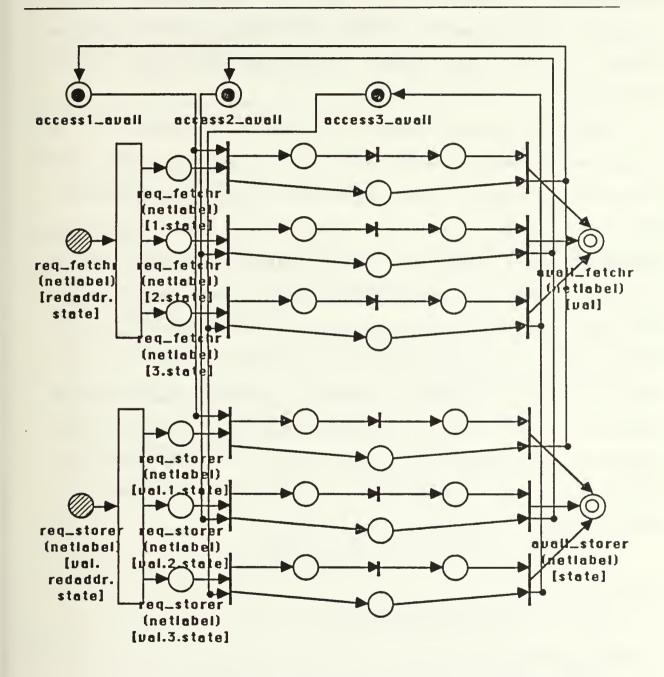

To show the versatility of the proposed methodology we will specify memory and register access differently: we are going to specify memory access in a way that allows only one access to one memory cell at a time (an implementation for this method might be a single memory unit allowing only one access at a time). On the other hand we might want to able to access registers in parallel. These requirements determine the internal structure of resulting specification.

Considering the above requirements on how we have to specify the system we realize that we have to construct the specification to deal with memory accesses and accesses to each register separately.

As the next step we are going to specify the memory accesses. Since we know from our requirements that only one access at a time is allowed to the memory we have to provide a mutual exclusion mechanism in our specification that makes sure that the memory is not accessed by more than one request at a time.

From Figure 5.1 we see that from any system location indicated by a netlabel a message in an entry place to request a memory access can only trigger a transition to activate the process when the process is available. Since there is only one empty message to indicate the availability of the net only one request can be honored at a time. The availability is restored when the access is completed. Also we see that the internal places "processed\_for" serve as traffic signs to direct the results to the appropriate exit places. Drawing the picture of the net can be helpful to the process of specifying net just as flow charts can be helpful in programming tasks, but our intention is primarily to state a formal specification. The following is the dynamic part of the memory access specification expressed in precise syntax:

entry places

req\_fetchm(netlabel)[memaddr.state];

req\_storem(netlabel)[val.memaddr.state];

exit places

avail\_fetchm(netlabel)[val];

avail\_storem(netlabel)[state];

internal places

access\_avail[];

fetchm\_for(netlabel)[];

fetchm\_activated[memaddr.state];

fetchm\_completed[val]; storem\_for(netlabel)[]; storem activated[val.memaddr.state]; storem completed[state]; initial state => access avail[]; transitions act fetchm: [memaddr.state],[] -> [memaddr.state],[]; perform\_fetchm: [memaddr.state] -> [val]; finish\_fetchm: [val],[] -> [val],[]; act storem: [val.memaddr.state],[] -> [val.memaddr.state],[]; perform storem: [val.memaddr.state] -> [state]; finish\_storem: [state],[] -> [state],[]; properties act fetchm(req fetchm(l1)[m.q], access\_avail[]) => fetchm\_for(l1)[], fetchm\_activated[m.q]; perform fetchm(fetchm activated[m.q]) => fetchm\_completed[v]; finish fetchm(fetch completed[v], fetchm for(11)[]) => avail\_fetchm(l1)[v], access\_avail[]; act\_storem(req\_storem(l1)[v.m.q], access\_avail[]) => storem\_for(|1)[], storem\_activated[v.m.q]; perform storem(storem activated[v.m.q]) => storem\_completed[q1]; finish\_storem(storem\_completed[q1], storem\_for(l1)[]) => avail storem(l1)[q1], access\_avail[]; When we look at the requirements of the register accesses that above design for memory accesses is not we see the suitable for register access if we want to allow for concurrent access to registers. So we have to find a way to express the properties of register accesses. Looking closely again at the requirements we realize that each register has the same access policies as the whole memory we specified before. This leads us to the fact that every register has to have its own specification. For the sake of simplicity let us say that our system has three registers with register addresses 1,2 and 3. We could now define three different nets each for the access of a certain register. There is one problem though: whenever a register access is requested from somewhere in the system, the proper net for the register to be accessed has to be addressed. So we want to have the decision about which register net is meant centralized in one place in the system. Therefore we employ some decision

Figure 5.1: Petri Net Graph for Memory Access

mechanism to select the right register access net. In this case the graph drawn out in Figure 5.2 of the net might confuse more than it helps. We try to specify the register

Figure 5.2: Petri Net Graph for Register Access

access just by direct reasoning. Still, the graph in Figure 5.2 illustrates that, despite the fact that each register can be accessed independently from the other registers, only oneaccess to a register is allowed at a time because of the separate "access\_avail" places for each register. These places prohibit any access to a register until it is available.

Again, we can anticipate that access to registers will be requested by several locations in the system. So we can state the entry and exit places as we have in the memory example. Next we already found out that there three independent register access nets and we can use again this structure for internal places and transitions we used in the memory access net. But how do we state that the net for register 1 is used when there is an access request for register 1 and only this net? The indication that a certain register is going to be accessed is the register address contained in the request message. Now instead of a name of the register address we state the actual value of it when we specify the properties:

entry places

req\_fetchr(netlabel)[regaddr.state];

req\_storer(netlabel)[val.regaddr.state];

exit places avail\_fetchr(netlabel)[val]; avail\_storer(netlabel)[state];

internal places

access1\_avail[];

fetchr1\_activated[regaddr.state];

fetchr1\_completed[val];

storer1\_activated[val.regaddr.state];

storer1\_completed[state];

```

access2_avail[];

fetchr2 activated[regaddr.state];

fetchr2 completed[val];

storer2 activated[val.regaddr.state];

storer2 completed[state];

access3_avail[];

fetchr3_activated[regaddr.state];

fetchr3_completed[val];

storer3_activated[val.regaddr.state];

storer3 completed[state];

fetchr for(netlabel)[];

storer for(netlabel)[];

initial state

=> access1 avail[];

=> access2 avail[];

=> access3_avail[];

transitions

act_fetchr1: [regaddr.state],[] -> [regaddr.state],[];

perform_fetchr1: [regaddr.state] -> [val];

finish_fetchr1: [val],[] -> [val],[];

act storer1: [val.regaddr.state],[] ->

[val.regaddr.state],[];

perform storer1: [val.regaddr.state] -> [state];

finish storer1: [state],[] -> [state],[];

act fetchr2: [regaddr.state],[] -> [regaddr.state],[];

perform fetchr2: [regaddr.state] -> [val];

finish_fetchr2: [val],[] -> [val],[];

act_storer2: [val.regaddr.state],[] ->

[val.regaddr.state],[];

perform_storer2: [val.regaddr.state] -> [state];

finish_storer2: [state],[] -> [state],[];

act_fetchr3: [regaddr.state],[] -> [regaddr.state],[];

perform fetchr3: [regaddr.state] -> [val]:

finish_fetchr3: [val],[] -> [val],[];

act storer3: [val.regaddr.state],[] ->

[val.regaddr.state],[];

perform_storer3: [val.regaddr.state] -> [state];

finish_storer3: [state],[] -> [state],[];

properties

act_fetchri(req_fetchr(l1)[1.q], access1_avail[]) =>

fetchr_for(l1)[],fetchr1_activated[1.q];

perform_fetchri(fetchri_activated[i.q]) =>

fetchr1 completed[v]:

finish_fetchr1(fetch1_completed[v], fetchr for(l1)[]) =>

avail_fetchr(l1)[v], access1_avail[];

```

```

act_storer1(req_storer(l1)[v.1.q], access1_avail[]) =>

storer_for(l1)[], storer1_activated[v.1.q];

perform_storer1(storer1_activated[v.1.q]) =>

storer1 completed[q1];

finish storer1(storer1 completed[q1], storer for(11)[])

=> avail storer(11)[q1], access1 avail[];

act_fetchr2(req_fetchr(l1)[2.q], access2_avail[]) =>

fetchr for(11)[],fetchr2 activated[2.q];

perform fetchr2(fetchr2 activated[2.q]) =>

fetchr2 completed[v];

finish_fetchr2(fetch2_completed[v], fetchr_for(l1)[]) =>

avail_fetchr(l1)[v], access2_avail[];

act storer2(req storer(11)[v.2.q], access2 avail[]) =>

storer for(11)[], storer2 activated[v.2.q];

perform_storer2(storer2_activated[v.2.q]) =>

storer2 completed[q1];

finish_storer2(storer2_completed[q1], storer_for(11)[])

=> avail_storer(11)[q1], access2_avail[];

act_fetchr3(req_fetchr(l1)[3.q], access3_avail[]) =>

fetchr for(11)[],fetchr3 activated[3.q];

perform_fetchr3(fetchr3_activated[3.q]) =>

fetchr3 completed[v];

finish_fetchr3(fetch3_completed[v], fetchr_for(11)[]) =>

avail_fetchr(l1)[v], access3 avail[];

act_storer3(req_storer(11)[v.3.q], access3_avail[]) =>

storer_for(l1)[], storer3_activated[v.3.q];

perform_storer3(storer3_activated[v.3.q]) =>

storer3_completed[q1];

finish_storer3(storer3_completed[q1], storer_for(l1)[])

=> avail_storer(11)[q1], access3_avail[];

```

We see that even specifications of simple resources become large and complex and the drawing the net is even more complex. Here we realize the real benefit of the introduction of subnets: once these subnets are specified we can use their properties everywhere in our system simply by stating the entry and exit places of the subnets in the net we want to specify. Those nets using subnets are actually extensions of the subnets. The next section will illustrate these facts in detail.

# C. MODELING OF INSTRUCTION FETCH AND EXECUTION TIMING

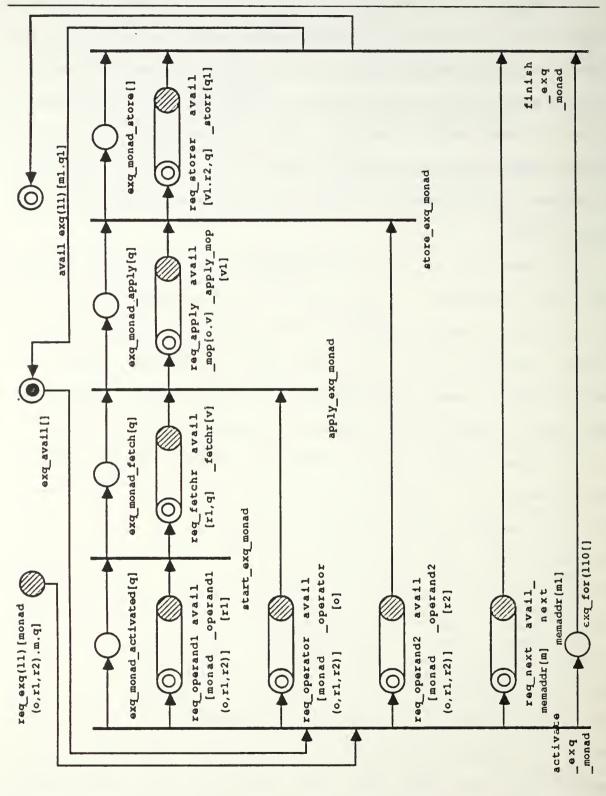

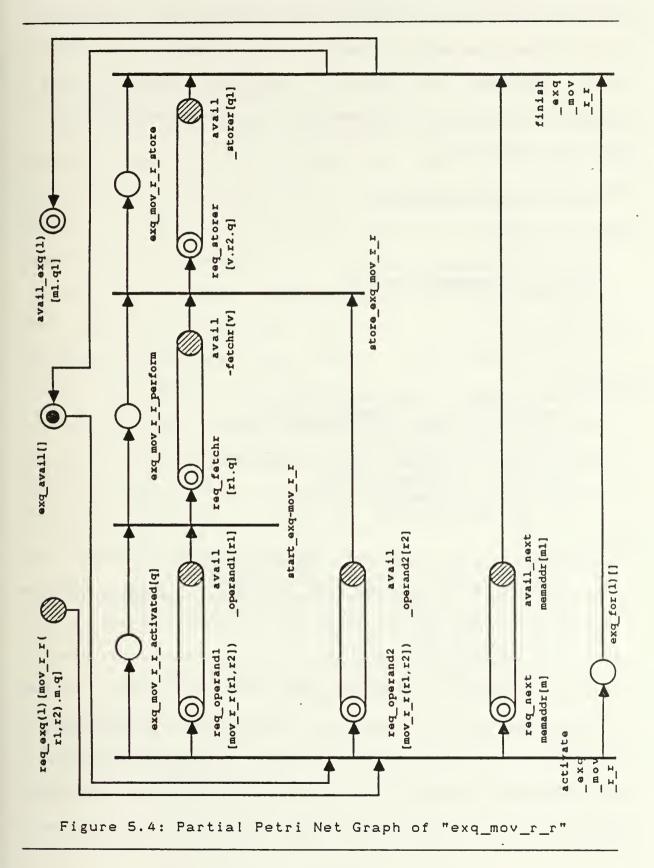

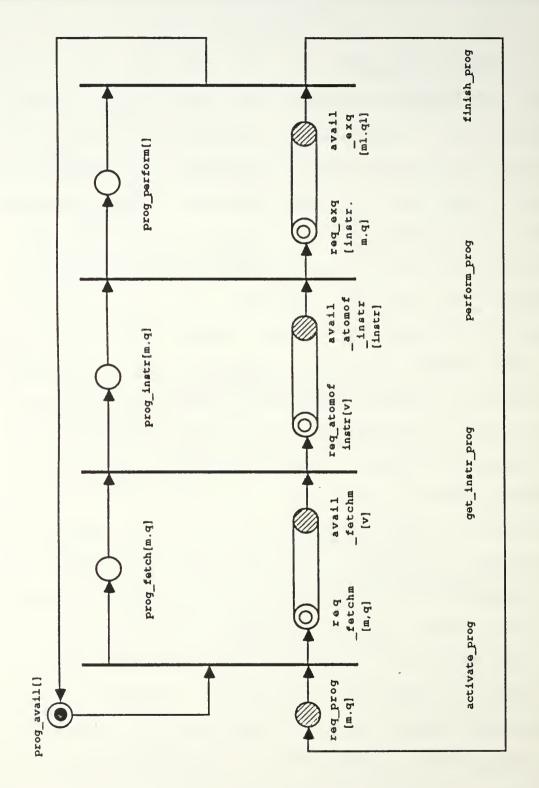

From the static specification of the Abstract Processor we see that there are two operands "prog" and "exq" which are responsible for the process of executing programs. The process is kept going by corecursive calls between those two operators.

Even though those two processes are very closely connected by corecursive calls we want to consider them separately and start with specifying the "exq" process.

The "exq" process needs information about the instruction executed, the current memory address, and the state of to be the processor. After the process has finished it returns the new state. This determines the contents of the messages the entry and exit places of this net have to accommodate. Still have to decide what kind of execution unit we want to we specify. We want to specify that only one execution unit can be performed at a time. This means that we have to provide mutual exclusion for the use of this net. We can do this the same way as we provided for memory accesses. We can accomplish that by providing a distinct entry place and exit place indicated by netlabels. Now we are in a position to specify the entry and exit places:

- req\_exq(netlabel)[instr.memaddr.state]; as the entry

place

- avail\_exq(netlabel)[memaddr.state]; as the exit place

At this point we have to look closely at the actions an execution on an instruction has to accomplish: retrieval of