# **Calhoun: The NPS Institutional Archive**

# **DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

2006-06

# ELINT signal processing on reconfigurable computers for detection and classification of LPI Emitters

Brown, Dane A.

Monterey California. Naval Postgraduate School

http://hdl.handle.net/10945/2785

Downloaded from NPS Archive: Calhoun

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

# THESIS

# ELINT SIGNAL PROCESSING ON RECONFIGURABLE COMPUTERS FOR DETECTION AND CLASSIFICATION OF LPI EMITTERS

by

Dane A. Brown

June 2006

Thesis Advisor: Second Reader: Douglas J. Fouts Herschel H. Loomis, Jr.

Approved for public release; distribution is unlimited

| <b>REPORT DOCUMENTATION PAGE</b> Form Approved OMB No. 0704-018                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                      |                                              |         | OMB No. 0704-0188 |                              |                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|-------------------|------------------------------|-------------------------------------|

| Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington DC 20503.                                                                                                                                                                                 |                                                                                                                                                                                                      |                                              |         |                   |                              |                                     |

| 1. AGENCY USE ONLY (Leave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | blank)                                                                                                                                                                                               | <b>2. REPORT DATE</b><br>June 2006           | 3. REF  | PORT TY           | PE AND DATE<br>Master's Thes |                                     |

| <ul><li>4. TITLE AND SUBTITLE:<br/>Computers for Detection and Class</li><li>6. AUTHOR(S) Dane A. Brown</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                      | Γ Signal Processing on<br>n of LPI Emitters  | Reconfi | igurable          | 5. FUNDING N                 | IUMBERS                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES)       8. PERFORMING         Center for Joint Services Electronic Warfare       ORGANIZATION REPORT         Naval Postgraduate School       NUMBER |                                              |         |                   |                              |                                     |

| 9. SPONSORING /MONITORING AGENCY NAME(S) AND ADDRESS(ES)       10. SPONSORING/MONITORING         National Security Agency       AGENCY REPORT NUMBER         Fort Meade, MD       AGENCY REPORT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |                                              |         |                   |                              |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>11. SUPPLEMENTARY NOTES</b> The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government.    |                                              |         |                   |                              |                                     |

| 12a. DISTRIBUTION / AVAILABILITY STATEMENT       12b. DISTRIBUTION CODE         Approved for public release; distribution is unlimited       12b. DISTRIBUTION CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |                                              |         |                   |                              |                                     |

| <b>13. ABSTRACT (maximum 200 words)</b><br>This thesis describes the implementation of an ELINT algorithm for the detection and classification of Low Probability of Intercept (LPI) signals. The algorithm was coded in the C programming language and executed on a Field Programmable Gate Array based reconfigurable computer; the SRC-6 manufactured by SRC Computers, Inc. Specifically, this thesis focuses on the preprocessing stage of an LPI signal processing algorithm. This stage receives a detected signal that has been run through a Quadrature Mirror Filter Bank and outputs the preprocessed signal for classification by a neural network. A major value of this study comes from comparing the performance of the reconfigurable computer to that of supercomputers and embedded systems that are currently used to solve the signal processing needs of the United States Navy. |                                                                                                                                                                                                      |                                              |         |                   |                              |                                     |

| <b>14. SUBJECT TERMS</b> C Programming, Field Programmable Gate Array (FPGA), <b>15. NUMBER OF</b> Hardware Description Language (HDL), Programmable Logic Device (PLD), Radar, Reconfigurable <b>16. NUMBER OF</b> Computing, Signal Processing, Verilog HDL (VHDL)       105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                      |                                              |         |                   |                              |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10 5                                                                                                                                                                                                 |                                              |         |                   |                              | 16. PRICE CODE                      |

| 17. SECURITY<br>CLASSIFICATION OF<br>REPORT<br>Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                      | CURITY<br>SIFICATION OF THIS<br>Unclassified | s C     | BSTRAG            | ICATION OF                   | 20. LIMITATION<br>OF ABSTRACT<br>UL |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                      | Chelusonieu                                  |         | 0110              |                              | ard Form 298 (Rev. 2-89)            |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

#### Approved for public release; distribution is unlimited

# ELINT SIGNAL PROCESSING ON RECONFIGURABLE COMPUTERS FOR DETECTION AND CLASSIFICATION OF LPI EMITTERS

Dane A. Brown Ensign, United States Navy B.S., United States Naval Academy, 2005

Submitted in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

# NAVAL POSTGRADUATE SCHOOL June 2006

Author: Dane A. Brown

Approved by:

Douglas J. Fouts Thesis Advisor

Herschel H. Loomis, Jr. Second Reader

Jeffrey B. Knorr Chairman, Department of Electrical and Computer Engineering

# ABSTRACT

This thesis describes the implementation of an ELINT algorithm for the detection and classification of Low Probability of Intercept (LPI) signals. The algorithm was coded in the C programming language and executed on a Field Programmable Gate Array based reconfigurable computer; the SRC-6 manufactured by SRC Computers, Inc. Specifically, this thesis focuses on the preprocessing stage of an LPI signal processing algorithm. This stage receives a detected signal that has been run through a Quadrature Mirror Filter Bank and outputs the preprocessed signal for classification by a neural network. A major value of this study comes from comparing the performance of the reconfigurable computer to that of supercomputers and embedded systems that are currently used to solve the signal processing needs of the United States Navy.

# TABLE OF CONTENTS

| I.   | INTI | RODU   | CTION                                 | 1  |

|------|------|--------|---------------------------------------|----|

|      | А.   | BAC    | CKGROUND                              | 1  |

|      | В.   | OBJ    | ECTIVE                                | 2  |

|      | C.   | REL    | ATED WORK                             | 3  |

|      | D.   | THE    | ESIS ORGANIZATION                     | 3  |

| II.  | SRC  | -6 OVE | ERVIEW                                | 5  |

|      | А.   | INT    | RODUCTION                             | 5  |

|      | В.   | HAR    | RDWARE                                | 5  |

|      |      | 1.     | Microprocessor                        | 5  |

|      |      | 2.     | MAP Board                             | 5  |

|      |      |        | a. MAP Organization                   | 5  |

|      |      |        | b. Control Logic                      | 6  |

|      |      |        | c. Memory                             | 7  |

|      |      |        | <i>d. FPGA</i>                        | 9  |

|      | C.   | SOF    | TWARE                                 | 11 |

|      |      | 1.     | Software Environment                  | 11 |

|      |      |        | a. Linux Operating System             | 11 |

|      |      |        | b. Languages                          |    |

|      |      |        | c. File Types                         | 12 |

|      |      |        | d. Editing Programs                   | 13 |

|      |      | 2.     | Compilation                           | 14 |

|      | D.   | SUM    | 1MARY                                 | 15 |

| III. | PRO  |        | STAGES                                |    |

|      | А.   | INT    | RODUCTION                             | 17 |

|      | В.   | DET    | TECTION                               | 18 |

|      |      | 1.     | Detection Techniques                  | 18 |

|      |      |        | a. Time-Frequency                     | 19 |

|      |      |        | b. Bifrequency                        |    |

|      |      | 2.     | ELINT Algorithms                      | 19 |

|      |      |        | a. Wigner-Ville Distribution          |    |

|      |      |        | b. Quadrature Mirror Filter Bank Tree | 20 |

|      |      |        | c. Cyclostationary Signal Processing  |    |

|      | C.   |        | PROCESSING                            |    |

|      | D.   | NEU    | JRAL NETWORK CLASSIFICATION           |    |

|      |      | 1.     | Autonomous Classification Methods     |    |

|      |      | 2.     | Recognized Modulations                |    |

|      |      |        | a. FMCW Modulations                   |    |

|      |      |        | b. BPSK Modulations                   |    |

|      |      |        | c. Polyphase Modulations              |    |

|      |      |        | d. Polytime Modulations               | 24 |

|      |                                           | 3. Modulation Results           | 24 |

|------|-------------------------------------------|---------------------------------|----|

|      | Е.                                        | SUMMARY                         | 25 |

| IV.  | PRE                                       | PROCESSING                      | 27 |

|      | A.                                        | INTRODUCTION                    | 27 |

|      | B.                                        | CROPPING                        | 28 |

|      |                                           | 1. Standard Cropping            | 28 |

|      |                                           | 2. Black-Cropping               |    |

|      | C.                                        | THRESHOLDING                    |    |

|      | D.                                        | BINARIZATION                    | 29 |

|      | E.                                        | RESIZING                        | 29 |

|      | F.                                        | SUMMARY                         | 30 |

| V.   | ALC                                       | GORITHM PORTING                 | 31 |

|      | A.                                        | INTRODUCTION                    | 31 |

|      |                                           | 1. Purpose                      | 31 |

|      |                                           | 2. Procedure                    |    |

|      | B.                                        | MATLAB CODE                     |    |

|      | C.                                        | STANDARD C CODE                 |    |

|      | D.                                        | SRC C CODE                      |    |

|      |                                           | 1. Main Program                 |    |

|      |                                           | 2. Subroutine                   |    |

|      |                                           | 3. Make File                    |    |

|      | Е.                                        | SUMMARY                         |    |

| VI.  | PER                                       | FORMANCE ANALYSIS               | 43 |

|      | A.                                        | INTRODUCTION                    |    |

|      | B.                                        | EXECUTION TIMES                 |    |

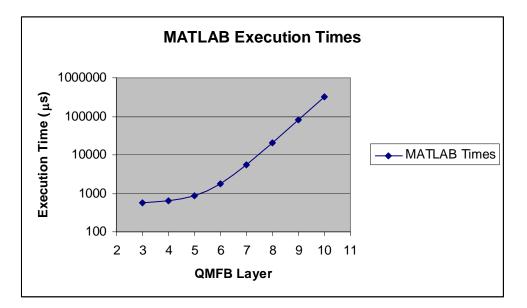

|      |                                           | 1. MATLAB                       |    |

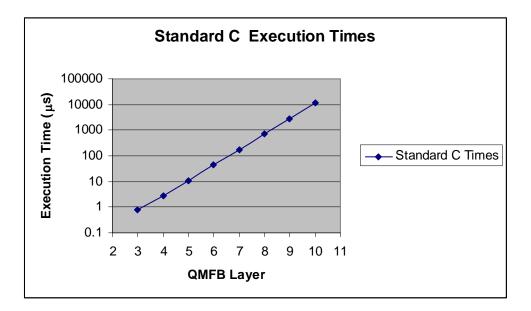

|      |                                           | 2. Standard C                   |    |

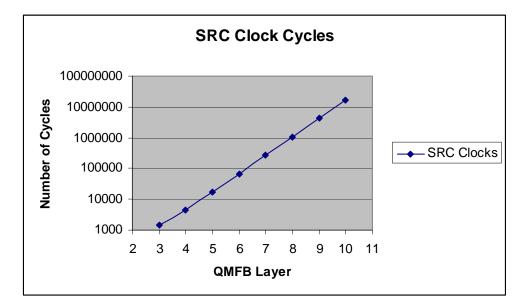

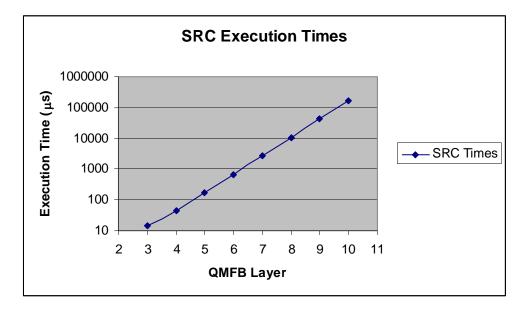

|      |                                           | 3. SRC-6                        |    |

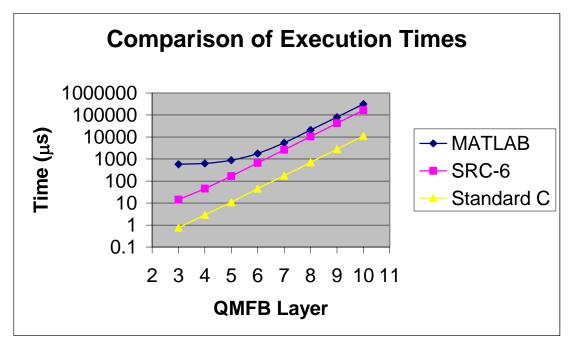

|      | C.                                        | COMPARISON                      |    |

|      | D.                                        | SUMMARY                         |    |

| VII. | CON                                       | NCLUSIONS                       | 57 |

|      | A.                                        | SUMMARY                         |    |

|      | <b>B</b> .                                | PROBLEMS ENCOUNTERED            |    |

|      | C.                                        | RECOMMENDATIONS FOR FUTURE WORK |    |

| APPE | ENDIX                                     | A. MATLAB CODE                  | 61 |

|      | A.                                        | MATLAB CODE                     |    |

|      | <b>B</b> .                                | OUTPUT                          |    |

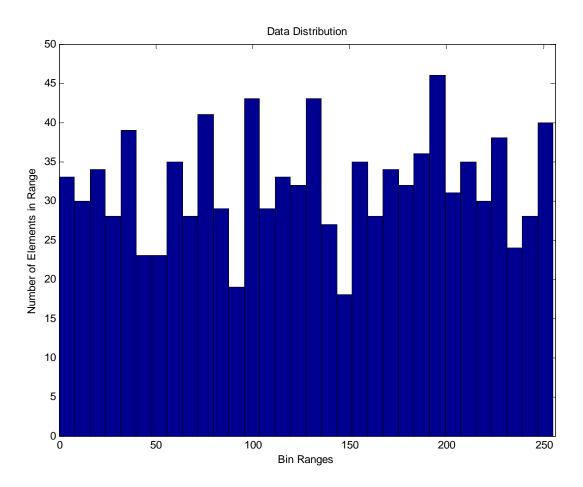

|      | C.                                        | HISTOGRAM                       |    |

| APPF | ENDIX                                     | K B. STANDARD C CODE            | 69 |

|      | A.                                        | STANDARD C CODE                 |    |

|      | B.                                        | OUTPUT                          |    |

|      |                                           | K C. SRC-6 SPECIFIC C CODE      |    |

| Arrr | $\Delta \mathbf{D} \mathbf{D} \mathbf{D}$ | A C. BAC-UBECIFIC C CODE        |    |

| А.        | SRC-6 SPECIFIC C CODE |    |

|-----------|-----------------------|----|

|           | 1. main.c             |    |

|           | 2. preproc.mc         |    |

|           | 3. Make File          |    |

| В.        | OUTPUT                | 79 |

| LIST OF R | REFERENCES            | 83 |

| INITIAL D | DISTRIBUTION LIST     |    |

# LIST OF FIGURES

| Figure 1.  | Interface Architecture of the MAP (From Ref. 4.)      | 6  |

|------------|-------------------------------------------------------|----|

| Figure 2.  | On-Board Memory Interface (From Ref. 4.)              | 9  |

| Figure 3.  | User Logic Interface to MAP (From Ref. 4.)            | 10 |

| Figure 4.  | User Logic Internal Interface (From Ref. 4.)          | 11 |

| Figure 5.  | SRC-6 Compilation Process (From Ref. 5.)              | 15 |

| Figure 6.  | Project Flow Chart (After Ref. 6.)                    |    |

| Figure 7.  | The Quadrature Mirror Filter Bank Tree (From Ref. 6.) |    |

| Figure 8.  | Preprocessing Flow Chart (After Ref. 8.)              | 27 |

| Figure 9.  | MATLAB Execution Times                                | 46 |

| Figure 10. | Standard C Execution Times                            | 49 |

| Figure 11. | SRC-6 Clock Cycles Executed                           | 51 |

| Figure 12. | SRC-6 Execution Times                                 |    |

| Figure 13. | Preprocessing Procedure Execution Times               | 54 |

| Figure 14. | MATLAB Histogram                                      |    |

# LIST OF TABLES

| Table 1. | MAP Registers (From Ref. 4.)     | 7  |

|----------|----------------------------------|----|

| Table 2. | QMFB Classification Results.     |    |

| Table 3. | MATLAB Execution Timing Data     |    |

| Table 4. | Standard C Execution Timing Data |    |

| Table 5. | SRC-6 Execution in Clock Cycles  |    |

| Table 6. | SRC-6 Execution Time Data        |    |

| Table 7. | Comparison of Average Times      | 53 |

# ACKNOWLEDGMENTS

I would like to thank David Caliga of SRC Computers, Inc. for his invaluable contributions to my research process. His hands on training course and book of SRC documentation made programming on the SRC-6 much simpler than it would have been otherwise.

Many thanks to Professor Jon Butler of NPS for his Advanced Computer Architecture course which gave me a first glance at the SRC-6 hardware and software interfaces.

I am grateful to Professor Phillip Pace of NPS who provided much of the research pertaining to LPI signal processing and answered many of my questions regarding that part of the project. His understudy, ENS Eric Zilberman, was also instrumental to my work as his research ran somewhat parallel to mine except that it dealt mainly in MATLAB.

Professor Douglas Fouts of NPS was my thesis advisor who organized and directed my research. He was also responsible for pointing me to sources of further help when I came to an impasse; I would like to thank him for his contributions.

Finally, this research was supported in part by the National Security Agency and the Office of Naval Research Code 313, Arlington, Virginia.

# **EXECUTIVE SUMMARY**

This thesis describes the implementation of an ELINT algorithm for the detection and classification of Low Probability of Intercept (LPI) signals. The algorithm was coded in the C programming language and executed on a Field Programmable Gate Array based reconfigurable computer; the SRC-6 manufactured by SRC Computers, Inc.

This thesis is part of a larger project in which all three stages of the detection to classification sequence for Low Probability of Intercept Signals are being ported to the SRC-6 and having their combined performance compared to general processing solutions that are in place presently. One student will be completing the porting of the detection algorithm into the C language for the SRC-6. The output from this code will then be fed into the section being completed in this thesis for preprocessing. The output from the code presented here will then be sent to the final stage of the detection to classification sequence which is classification of the modulations present in the signal by a trained Neural Classifying Network. A third student will be focusing his or her efforts on the creation and training of this Neural Network. The work from all three of these stages will be focused on the Quadrature Mirror Filtering Bank detection techniques, which is one of the common time-frequency techniques for detecting Low Probability of Intecept signals.

Specifically, this thesis focuses on the preprocessing stage of an LPI signal processing algorithm. This stage receives a detected signal that has been run through a Quadrature Mirror Filter Bank and outputs the preprocessed signal for classification by a neural network. Once these other two stages have been ported to the SRC-6 by the other students, all three stages may then be run on the SRC-6 hardware in parallel. These three pieces are optimized so that when they are run in parallel, the overall program should be much faster and provide a significant processing gain over general purpose processing solutions that are currently available. A major value of this study comes from comparing the performance of the reconfigurable computer to that of supercomputers and embedded systems that are currently used to solve the signal processing needs of the United States Navy.

# I. INTRODUCTION

#### A. BACKGROUND

In the field of battle, it is important to gain every possible advantage over an opponent. LPI radar and communication systems are one tool that helps to give this edge. LPI stands for Low Probability of intercept and these systems have characteristics that make them very difficult to detect with modern intercept receivers. Clearly, the edge could be taken back if one were able to come up with a reliable method to consistently detect and classify these signals in real time or near real time.

One approach seeks to determine if a reconfigurable computer can accomplish the required real-time processing of LPI radar and communications signals. ELINT (Electronic Intelligence) algorithms for automatically detecting and classifying LPI emitters have already been developed and tested. The specific ELINT algorithms applicable to Low Probability of Intercept emitters utilize the pseudo Wigner-Ville distribution algorithm, the Quadrature Mirror Filter Bank algorithm, and the Cyclostationary signal processing algorithm.

A reconfigurable computer is a computer with the capability to reprogram the hardware logic circuits and optimize them for the algorithms specific to the user [1]. These systems are usually based heavily on FPGAs (Field Programmable Gate Array) and PLDs (Programmable Logic Devices) embedded in their design. The advantage of reconfigurable computing is, as its name implies, that devices may be programmed and reprogrammed at any time to suit the needs of the user. This cuts down on the cost and development time of manufacturing an entirely new device simply to make minor changes to the hardware. Reconfigurable computers are also able to realize increased speed in their functions over general purpose supercomputers because the hardware is specialized and they are able to devote all of their processing power on the task they have been programmed to perform.

The SRC-6, by SRC Computers, Inc., is an example of such a reconfigurable computer. It contains two Pentium 4 processors and a Multi-Adaptive Processing (MAP) board with four Xilinx Virtex-II series XC2V6000 FPGAs. Through the provided Linux

interface, the SRC-6 can be programmed directly in a hardware description language that correlates specifically to the logic design inside the chip. More recently, SRC Computers has added the ability to port programs written in the C language over to the SRC-6. This greatly broadens the scope of what can be accomplished on the system.

Once running, the Virtex-II FPGAs operate at 100 MHz. This is clearly much slower than the speeds at which modern supercomputers operate, but the SRC-6 attempts to make up for its lack of speed in other areas such as its programmable hardware and its inherent parallelism.

#### **B. OBJECTIVE**

There are two major objectives of this thesis work. It is necessary to determine whether ELINT algorithms for the detection and classification of Low Probability of Intercept signals can be coded for execution on a reconfigurable computer. If it is indeed possible, the second goal will become to ascertain what level of performance can be achieved when compared to commodity computing solutions.

This research will help to answer questions regarding the practicality of reconfigurable computing, such as whether reconfigurable computers can process vast amounts of data in real time. Radar detection and classification can be a very time-sensitive matter in which information will be needed almost as soon as it is intercepted. This means that the real-time processing capabilities of the SRC-6 will be crucial in this study.

Once a suitable solution has been created and tested, its performance must be compared to the solutions that are already in place. Benchmarking will be necessary to compare the performance of the solution programmed onto the reconfigurable SRC-6 versus that of existing supercomputers and embedded signal processing systems. This benchmarking will compare these systems not only by quality of performance, but also by cost and speed. It is well known that supercomputers are very fast and that embedded systems are very specialized. It is anticipated that the SRC-6 reconfigurable computer will be able to obtain a desirable combination of these advantages at a much lower cost. If the SRC-6 is able to outperform the competition as expected, it could become an invaluable tool for the Navy to use in detecting and classifying LPI signals. This thesis concentrates on the creation and examination of the preprocessing stage of the ELINT algorithms being coded onto the SRC-6. These algorithms are being coded in three distinct stages which are necessary to classify an LPI signal once it has been detected. The first of the stages is the detection itself which runs the intercepted signal through a filter created for LPI signals. This filtered signal is then passed on to a preprocessor which is covered in depth in this thesis. The preprocessor finally passes a resized image on to a neural network which performs the actual classification of the signal.

## C. RELATED WORK

This thesis is part of a larger project which seeks to autonomously detect and classify LPI signals. The sequence of detecting and classifying these signals described above has been broken up into its major stages. The first and third stages which involve detection and classification, respectively, have each been assigned to another researcher for porting to the SRC-6. Thus, this thesis does not cover these areas in depth, rather it completely explains and creates code for the second stage, preprocessing, and details the porting of this code to the reconfigurable computer.

Some research in this field has previously been done by Professor Phillip Pace of the Naval Postgraduate School on using these algorithms on a general purpose computer. His work successfully simulated the detection to classification sequence using the software simulation package MATLAB. The MATLAB code he has developed is the basis for the MATLAB code which will be developed for the specific application of this thesis. This MATLAB code will be used as a model and a benchmark for similar code which will be created here for execution on the SRC-6.

# D. THESIS ORGANIZATION

The remainder of this thesis is organized as follows:

- Chapter II provides an overview of the SRC-6 system. This begins with the system hardware, then moves on to a discussion of the software interface that has been provided.

- Chapter III is a discourse of the overall project, detailing each one of its major stages. These include the detection and filtering stage, the preprocessing stage, and the neural network classification stage.

- Chapter IV narrows in on the preprocessing stage and goes much deeper. This chapter describes the specific procedures of signal preprocessing which include cropping, thresholding, binarization, and matrix resizing.

- Chapter V describes the porting of the ELINT algorithms used from the original MATLAB code to the standard C code, and finally to the SRC-6 C code to be run on the reconfigurable computer.

- Chapter VI is a performance analysis of the final code running on the reconfigurable computer and a comparison of that implementation to other methods of detecting and classifying LPI radar signals.

- This thesis concludes with Chapter VII which gives a brief recap of the findings and makes some recommendations for future work in this area.

# II. SRC-6 OVERVIEW

#### A. INTRODUCTION

The SRC-6 is a powerful reconfigurable computer made by SRC Computers, Inc. This chapter describes the reconfigurable computer and how it may help speed up signal processing applications. It begins with a discussion of the architecture of the SRC and the hardware interface that a user is provided. It then moves on to describe the software interface a user sees for programming the reconfigurable computer.

## **B. HARDWARE**

As previously stated, the SRC-6 contains two Pentium 4 processors and a Multi-Adaptive Processing (MAP) board with four Xilinx Virtex-II series XC2V6000 FPGAs.

#### 1. Microprocessor

The Intel microprocessor is separate from the MAP board and this is where the general purpose computing takes place, just as in an ordinary computer. It also has a memory bus and access to the system Common Memory which can be accessed by both the microprocessor and the MAP. The SRC provides a SNAP<sup>™</sup> card to interface between the microprocessor and the MAP via Direct Memory Access procedures [2].

#### 2. MAP Board

#### a. MAP Organization

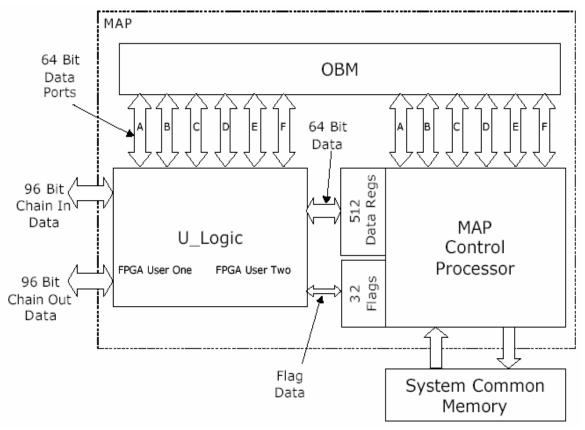

The MAP processor consists of some general control logic, memory, and two Xilinx Virtex II series XC2V6000 FPGAs. There are two MAP processors on the MAP board. Figure 1 below gives a block diagram of the MAP. It contains input and output to System Common Memory (SCM) to receive commands. It also has the MAP Control Processor which contains the system flags and the data registers. The MAP provides hardware for User Logic to be configured by the end user. In addition, there is an On-Board Memory bank that interfaces with the User Logic and the Control Logic via 62-bit data ports. The MAP board has General Purpose Input Output (GPIO) ports which allow direct connections for other MAPs or data input. It also contains Direct Memory Access (DMA) engines which support: distributed SRAM, Block SRAM, On-Board SRAM, and microprocessor memory [3].

## b. Control Logic

MAP operation is coordinated through use of Control Logic in the MAP Control Processor. This processor receives instruction sequences from a Command List, or ComList, which is provided by the System Common Memory via a DMA engine. This Control Logic executes instructions sequentially and controls such tasks as: User Logic functions, operand input, and result output [4].

The Control Processor is where the MAPs 32 flags and 512 data registers are found. Table 1 provides an appropriate description of these resources.

| Registers      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Registers | Data Registers (DRs) are mainly used to hold addresses, (both SCM and OBM addresses),<br>but can hold any needed data. By using Data Registers, scalar (single item) data can be<br>sent to or received from User Logic. Only simple arithmetic and logical operations are<br>supported on these registers. Register contents can be tested for zero/non-zero and thus<br>support command branches and loops. A given ComList command must use DRs from<br>within the same group.                                   |

|                | There are sixteen groups of thirty-two 64-bit registers, known as Groups 0 through 15 of DR0 through DR31.                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | DR0 is always zero. DR1 is always an integer 1. This applies to all groups. Neither register can be written, and errors will not be reported if a write to DR0 or DR1 is attempted.                                                                                                                                                                                                                                                                                                                                 |

| Flag Registers | Flag Registers (FRs) are used for direction of movement, requests, and complete functions.<br>Commands can test and wait on the state of Flag Registers before execution (e.g. hold<br>execution of this ComList command until Flag 3 goes set). Commands can change the<br>state of Flag Registers, forcing them to set and clear. In addition there are logical<br>instructions that allow combining Flag states (AND, OR, XOR). Other commands allow<br>testing and branching on the contents of Flag Registers. |

|                | There are thirty-two single-bit Flag Registers, FR0 through FR31                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                | FR0 is always clear, 0, and FR1 is always set, 1. Neither register can be written, and errors will not be reported if a write to FR0 or FR1 is attempted.                                                                                                                                                                                                                                                                                                                                                           |

|                | FR31 is reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Temp Register  | A register in the Control Processor used for temporary storage during the TMP2DR and DR2TMP commands.                                                                                                                                                                                                                                                                                                                                                                                                               |

# Table 1.MAP Registers (From Ref. 4.)

The explicitly controlled logic circuitry also features what is known as Direct Execution Logic (DEL). Direct Execution Logic is comprised of at least one User Logic device. These circuits allow for explicit computational units, memory pre-fetch units, and data access units [3]. These features cause the SRC-6 to have more efficient use of logic gates, power, and bandwidth, thus increasing processing power by several orders of magnitude, as compared to existing solutions.

# c. Memory

The SRC-6 MAP has access to its own memory known as On-Board Memory (OBM). There are six banks with each having four megabytes of memory, for a total of 24 megabytes. These banks are essentially arrays where each data element is exactly 64-bits long; each array can hold up to 523,776 elements, for a total of 3,142,656

64-bit data words across On-Board Memory. Technically, each bank could hold as many as 524,288 data elements but 512 of these data words are reserved for scalar values and working space.

The Direct Memory Access (DMA) engines are what allow this On-Board Memory system to be so effective. Data is transferred between the OBM banks and the general purpose microprocessor via DMA transfers. When transferring data to or from On-Board Memory banks one must specify: the direction of the transfer, where the OBM banks begin, how often to stripe, or input, the data, the Central Processing Unit (CPU) address, the CPU stride, the total length of the transfer in byte, and finally the server number which must wait for the DMA transfer to complete [5]. The instruction format is as follows:

DMA\_CPU (<Transfer Direction>, <OBM address>, <OBM striping>, <Computer Memory Address>, <Computer Memory Stride>, <Length>, <Server>); wait\_DMA (<Server>);

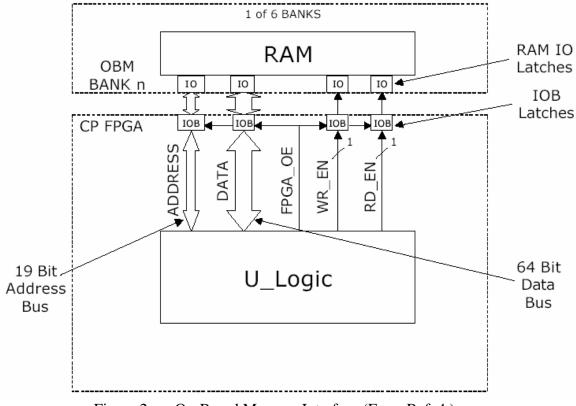

The following, Figure 2, shows a clear illustration of how each On-Board Memory bank interfaces with the User Logic. Data is sent back and forth in the standard 64-bit word format that OBM banks accept. Since there are 512k words in the memory banks, User Logic uses a 19-bit address bus to decode which element is being accessed. Finally, to control the bidirectional data, there is an FPGA output enable bit, a write enable bit, and a read enable bit.

Figure 2. On-Board Memory Interface (From Ref. 4.)

Having these six banks truly enhances the parallelism of the system, which is one of its greatest strengths, because each one can be accessed simultaneously.

# d. FPGA

The User Logic recently discussed is comprised of two Xilinx Virtex II Field Programmable Gate Arrays (FPGAs). These FPGAs are what make the SRC-6 a reconfigurable computer; the end users program them to their own specifications and thus define what is contained in User Logic. The User Logic FPGAs can interact with the control circuitry and can also read and write to On-Board Memory through various ports.

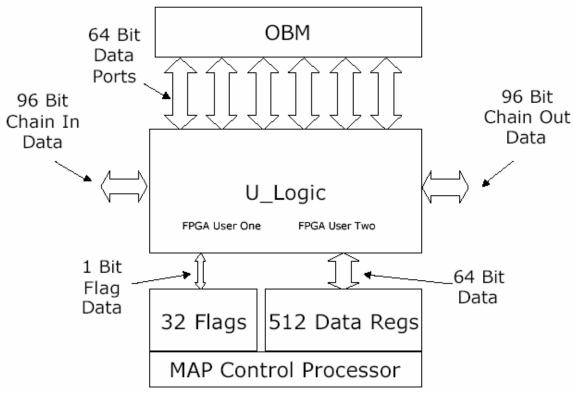

This diagram delineates the interfacing of the FPGAs to the rest of the MAP. It shows the six 64-bit bidirectional ports to On-Board Memory, as well as the ports to the MAP Control Processor through the flag bit and the data register bits. It also illustrates the input and output chain ports that could connect the local User Logic to external User Logic on another MAP, thus forming a chain of MAPs.

Figure 3. User Logic Interface to MAP (From Ref. 4.)

Since MAPs can be chained together by User Logic, they can communicate with one another, send partial results to other MAPs, and receive partial results from other MAPs. In this way, another dimension of parallelism is added to the SRC-6, which can reap great benefits in performance.

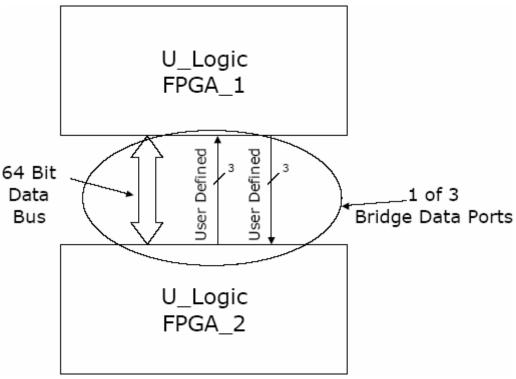

Not only can the FPGAs communicate with the rest of the MAP and other MAPs, they can also communicate between each other. The two FPGAs in User Logic are able to send data to one another using a 64-bit data bus that is separate from the memory board and does not use up any memory bandwidth. This bus, when combined with three bits of user defined input and three bits of user defined output, constructs a Bridge Data Port. There are three Bridge Data Ports [4].

Figure 4 which follows shows how the FPGAs communicate.

Figure 4. User Logic Internal Interface (From Ref. 4.)

# C. SOFTWARE

### 1. Software Environment

In order for the end users to utilize the functionality of the reconfigurable computer, they must program the SRC-6 using a specialized software development environment on a Linux computer.

#### a. Linux Operating System

Currently, the SRC-6 is compatible with the Red Hat version of the Linux operating system (OS). Linux is a Unix-based operating system which is not as familiar to most people or as user-friendly as Microsoft Windows, however it has many tools available for experienced users that really ease the processes of writing code, testing it, and debugging it.

Another advantage to using Linux is the shell interface. Unlike in Windows, one can easily set up a remote shell to a computer to which access is granted and execute any command as if one were at the host computer. This eliminates the need for a programmer to be physically located at the SRC-6 in order to program it. This ability is especially convenient at facilities where there is only one SRC-6 because multiple users can log onto it remotely and test their code rather than having to wait at the one machine for each person to complete their work.

#### b. Languages

As with any computer program, the creator must write and compile the code that accomplishes the desired function. For most reconfigurable computers, the language in which this code is written is VHDL, or VHSIC Hardware Description Language, which uses practical mnemonics to describe the specific hardware functions. While useful, VHDL still has a steep learning curve. It is still a relatively low-level language with which many programmers are unfamiliar.

SRC Computers, Inc. has attempted to eliminate the need for writing VHDL code, thus relieving the burden on the code developer. When programming the SRC-6, the coder has a choice between programming in FORTRAN or C. Both of these are very high level languages that do not possess the same control over the hardware that VHDL does, but each one is more intuitive to experienced programmers. Though FORTRAN is more straightforward than VHDL, the language itself is antiquated and obsolete. However, it is still an option to a programmer who is comfortable with it [5].

The overwhelming choice for modern programmers is C. While it does not include the object oriented abilities of its successor C++, it is equipped to handle most tasks applicable to reconfigurable computing and it is used exclusively in this thesis.

#### c. File Types

There are two file types made available to the programmer who codes in C, they are .c files and .mc files. These extensions tell the SRC-6 where to run the code. The .c files are set to be executed on the microprocessor, whereas the .mc files are set for execution on the MAP. Both files generally include *libmap.h*, a. header file that defines the prototypes and constants specific to working with the SRC-6. This allows the use of SRC-6 specific data types such as *uint64\_t* and functions such as DMA transfers.

To optimize programs on the SRC-6, a user must decide ahead of time what should be run on the microprocessor and what should be run on the MAP. The FPGAs can be configured to run certain repeated calculations much faster and more efficiently than the general purpose microprocessor. Once the programmer has planned the optimal method, the code that is desired to run on the MAP is written into the .mc file while the code that must be executed on the general purpose microprocessor is written into the .c file. Usually, the .mc file is used to run optimized functions and the .c file will be used to pass in the necessary parameters to be manipulated and then receive the desired data.

As previously noted, the C programs do not give the coder much specific control over hardware functions. If a user does need more hardware control, macros can be written directly in VHDL. There are two types of useful user-defined macros, external macros and user defined macros. External macros interact with the outside SRC-6 system and are controlled by *start* and *done* signals received from the system. Purely functional macros receive inputs and compute outputs every clock cycle. They are not stateful and can only process current data that they are given. However, they are able to pipeline data and execute them in parallel.

Macros that are created have three parts. The first is the VHDL code that describes the functioning of the hardware; this can be explicitly written by the programmer or extracted from a graphic schematic editing tool. The second part is a black box file, this file depicts the input and output interfaces of the macro. Finally a macro needs an info file. Info files work by linking the hardware signals to their respective variable and functions that they will be called with from the C programs [5].

#### d. Editing Programs

Editing C programs in Linux is a bit different than working with them using Microsoft Windows. The standard editors are not as user friendly and do not walk the programmer through the entire process of editing, formatting, compiling, and testing. *Vi* is a basic text editor found in all distributions of Unix and Linux. It is difficult to learn how to use, but if a programmer understands it, it can be used to program on any Unixbased machine. Another standard tool that is generally found is *gedit*. This is a graphical text editor that may be slightly more familiar to the average user, but still not very helpful to someone specifically trying to write programs. A rather helpful editor that is found on some Linux platforms is *emacs*. This is another graphical tool that is a powerful program editor. It recognizes languages like C and automatically formats and color-codes text to make it simpler for a coder to read.

#### 2. Compilation

Just as in any other programming language, written code must be compiled in order to be tested and debugged. In general, when programming in C on a Linux platform the GNU C compiler, *gcc*, is used. This program compiles the source code into object code then links and assembles it and turns it into an executable program. This is the general process for turning a high-level program into a running executable. However, it is not acceptable for SRC-6 programming. The C code must be translated into VHDL so that the FPGAs can understand how to operate the hardware.

This calls for a different compilation method which involves a Make file. The Make file is the last required file in a project directory. It goes alongside the .c, the .mc, and the macro files and is always titled *Make file*. There are three ways in which a user may Make a project. The first is a *make debug* mode. Debug compilation is fast because the code is just interpreted; if the syntax in the files is correct, debug mode will quickly simulate the results of the executed code. If the programmer wants to see a simulation that more closely emulates what will happen on the MAP, a *make simulate* mode is available. A simulated program takes longer to Make, but not as long as a full compilation. The final debug mode available to the coder is the *make hardware* mode. This actually Makes the code in the SRC-6 hardware ready for execution. This mode, however, takes much longer than the others to complete and is not practical for testing and debugging code. It is best used after completion of the debugging stage for performance analysis.

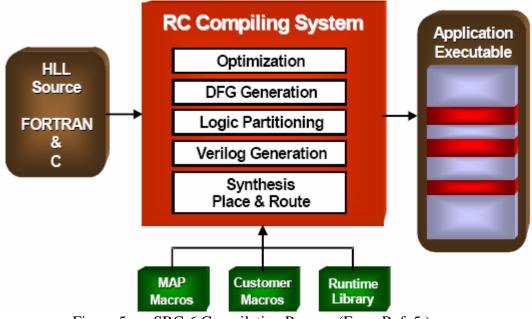

Figure 5 below is an accurate visual aid in understanding the stages of the compilation process that take place on the SRC-6.

Figure 5. SRC-6 Compilation Process (From Ref. 5.)

The previous *make* options compile the project in a certain way and leave many files in the project directory specific to their respective modes of execution. In order to recompile the program, a user must restore the directory to the basic source files. This is accomplished with the *make clobber* command. Another option is the *make clean* command, this will perform a similar function to *make clobber* with the exception that it will also leave the executable files themselves in the project directory [5].

## D. SUMMARY

This chapter provided a brief overview of the hardware and software interfaces provided in the SRC-6. It began with a description of the major hardware components, to include the microprocessor, the Multi-Adaptive Processing Board, and their interfaces. It then went on to discuss the software environment presented when working with the SRC-6, as well as how the compilation process works.

This information is necessary to the research because in order to program the reconfigurable computer, one must have a solid understanding of its interfaces and how to use them to accomplish the necessary tasks. The upcoming chapters move into a discussion of the process of detecting and classifying Low Probability of Intercept radar.

THIS PAGE INTENTIONALLY LEFT BLANK

# **III. PROJECT STAGES**

#### A. INTRODUCTION

Low Probability of Intercept signals are difficult to detect because of their inherent properties. For example, LPI radar has very low power, a wide bandwidth, and tends to vary the transmission frequencies. Additionally, LPI signals have the advantage of being veiled by modern environmental effects to include high noise interference and multiple signals destructively interfering with one another [6]. Clearly, an edge could be taken if one were able to come up with a reliable method to consistently detect and classify these signals in real time.

Non-cooperative intercept receivers achieve a significant increase in processing gain when using time-frequency and bifrequency techniques to detect LPI radar modulations. It is possible to use parallel pattern classification with these detection techniques to autonomously determine the modulation present in a signal. This intelligent autonomous handling of the intercepted signal will greatly mitigate if not eliminate the need for human intervention which can ultimately lead to real-time handling of the data [6].

There are three stages involved with intercepting an LPI signal and determining what it is. These are detection, preprocessing, and classification. If these three stages can be programmed into a pipeline and run in parallel on an SRC-6, near real-time processing of the LPI signals can be achieved.

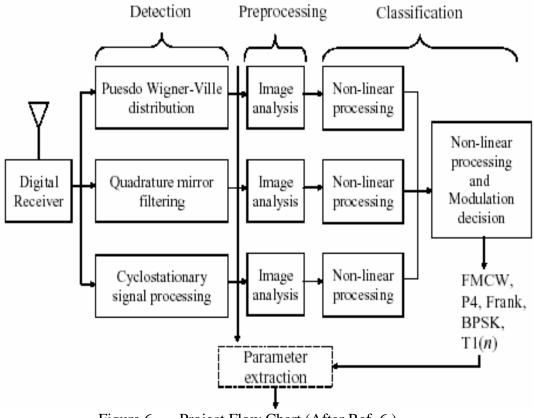

The flow of these three stages can be seen in Figure 6 to follow. This image is a good general description of the project and will be a constant visual reference for this thesis.

Figure 6. Project Flow Chart (After Ref. 6.)

# **B. DETECTION**

The detection can be performed by any one of three algorithms. The first is a pseudo Wigner-Ville distribution. The second is by a Quadrature Mirror Filter Bank (QMFB). The third method of detection is through Cyclostationary signal processing. The pseudo Wigner-Ville distribution and the Quadrature Mirror Filter Bank are both time-frequency techniques. Cyclostationary signal processing is a bifrequency detection technique. For simplicity, the entire process may be viewed as it stems from just one detection technique. A reasonable choice is to focus on the Quadrature Mirror Filter Bank.

# **1.** Detection Techniques

Time-frequency and bifrequency techniques are advanced signal processing methods that are used to detect Low Probability of Intercept signal because the wide bands of their frequency and phase modulations require significant processing gain on the part of the receiver. These two techniques produce images that can be later classified by a trained human or an autonomous device.

## a. Time-Frequency

Time-frequency distributions are generally used in examining nonstationary signals. These distributions represent the frequency spectrum of signals as a function of time, which make it relatively simple to determine what kind of modulations are present in a given signal. An ordinary time-domain signal lacks details about the frequencies of a signal making it impossible to determine the frequency modulations. Taking a Fourier transform of a time signal provides its frequency spectrum, however this spectrum does not specify anything about the times at which the signal energies are present.

Time-frequency distribution is a more sophisticated technique which takes advantage of the fact that time information is encoded into the phase of a Fourier transform. Taking this time information from the frequency spectrum is rather difficult as it involves complex calculations like phase unwrapping. Time-frequency information is usually a direct representation of the frequency content of a signal while keeping the time parameter intact [6]. These time-frequency techniques apply themselves well to detection techniques such as the Wigner-Ville Distribution and the Quadrature Mirror Filter Bank Tree.

## b. Bifrequency

Bifrequency spectral analysis is a method of taking a periodic part of a signal and examining its spectral frequency versus its cycle frequency. A bifrequency map describes a Linear Time Varying (LTV) system. For a non-stationary vector random process its autocorrelation function is a function of two indices. These processes have a bispectrum matrix which is a two-dimensional Fourier transform. This matrix fully describes the second order statistics of the process [7].

# 2. ELINT Algorithms

ELINT algorithms are Electronic Intelligence algorithms. The specific ELINT algorithms applicable to Low Probability of Intercept signal processing utilize the pseudo Wigner-Ville distribution algorithm, the Quadrature Mirror Filter Bank algorithm, and the Cyclostationary signal processing algorithm.

## a. Wigner-Ville Distribution

The first type of time-frequency algorithm used in detecting LPI signals is the Pseudo Wigner-Ville distribution (PWVD). This is one of the most useful and popular methods of time-frequency analysis in signal processing. The output of this distribution is always real and produces cross-terms between each pair of signal components which can complicate the recognition of signal modulations. These crossterms can, however, help the classification process with the added information they provide [6].

# b. Quadrature Mirror Filter Bank Tree

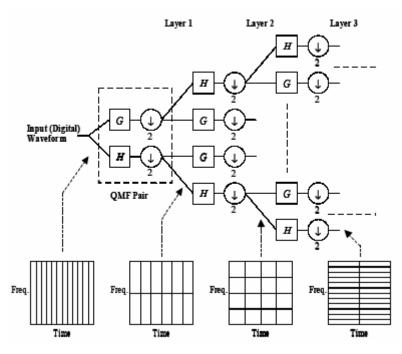

Another ELINT algorithm which makes use of time-frequency analysis is the Quadrature Mirror Filter Bank (QMFB) Tree. For the purpose of simplicity, this project follows the detection, preprocessing, and classification procedures using only one of the detection techniques in the above flow chart; the chosen technique here was the Quadrature Mirror Filter Bank Tree.

A QMFB tree consists of a number of layers of fully connected pairs of orthogonal wavelet filters (or basis functions) that linearly decompose the received waveform into tiles on the time-frequency plane. A modified sinc filter is used and every filter output is connected to a filter pair in the next layer, as shown in Figure 7 below. The tiles are used to refer to the rectangular regions of the time-frequency plane containing the basis function's energy. Each filter pair divides the digital input waveform into its high-frequency and low-frequency components, with a transition centered at  $\pi$ . Within the series of time-frequency layers, each subsequent layer provides a trade-off in time and frequency resolution. By examining the energy within the tiles, parameters such as bandwidth, center frequency, phase modulation, signal duration and location in the time-frequency plane can be determined [6].

Figure 7. The Quadrature Mirror Filter Bank Tree (From Ref. 6.)

The received signal is first padded with zeros to contain  $N_p = 2^L$  samples where L is the number of layers within the tree. A normalized input of one sample per second is assumed, with a signal bandwidth of  $[0, \pi]$ . Since each filter's output signal has half the bandwidth, only half the samples are required to meet the Nyquist criteria; therefore, these sequences are down sampled by two and the same number of output samples is returned. Each of the two resulting sequences is then fed into QMFB pairs, forming the next layer, where the process is repeated, and so on down the tree. The l=L/2layer provides a good compromise in time and frequency resolution. The QMFB output strongly resembles the signal's periodic ambiguity function [6].

# c. Cyclostationary Signal Processing

The detection technique which takes advantage of the bifrequency spectral analysis method is Cyclostationary processing. This model assumes that the input signal is periodically stationary and thus can measure the signal's periodic properties like modulation, sampling, and keying. These properties can be found through the results of the cyclic autocorrelation function and the spectral correlation density function. At certain frequency separations, known as the cycle frequency, a spectrally correlated signal is correlated with frequency-shifted versions of that signal. Finally, the spectral correlation density (SCD) can be approximated by a method know as direct frequency smoothing whereby the spectral components of the signal are calculated and then the frequency components directly undergo a spectral correlation operation [6].

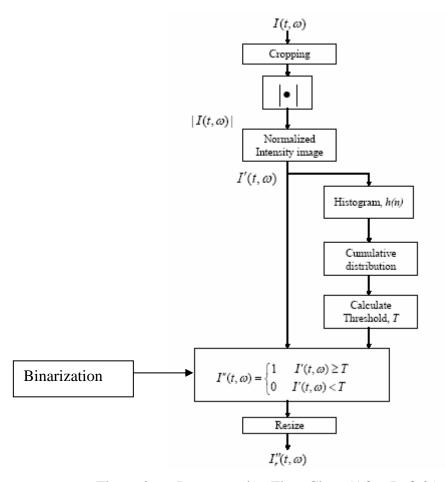

### C. PREPROCESSING

The next stage is preprocessing the image passed in from the detection algorithm to create a feature vector to pass on to be classified by the neural network. The main goals of preprocessing are to extract the features of modulation within the image, to reduce the dimensionality, and to keep the feature vector output as unique and small as possible [6]. Generally, the preprocessing stage begins with cropping, but this is not necessary when the Quadrature Mirror Filter Bank is used. With QMFB, preprocessing is accomplished by thresholding, binarization, and finally reshaping the input matrix into a unique feature vector.

The preprocessing stage is discussed in depth in the following chapter.

# D. NEURAL NETWORK CLASSIFICATION

The final stage is classification. Simply put, classification involves non-linear processing of the feature vector to put the data into a form in which the best decision can be made about what type of modulation was used to create the signal. This is accomplished by processing the feature vector received from the preprocessing stage through a three-layer perceptron neural network. These neural networks are well-suited to the classification stage because of their non-linear aptitude for learning and recognizing complex patterns.

## 1. Autonomous Classification Methods

Currently, expertly trained human operators are able to identify the signal parameters and determine the modulations received from the outputs of the timefrequency and bifrequency algorithms. In general, relying on a human to perform a task such as this adds considerable delay to the process. Classification would be significantly sped up if the classification stage were automated and performed by a fast computer. This way, signals could be classified in real time and the results would be useful in timesensitive applications.

Currently, there are three major techniques used in the autonomous classification of signals. These techniques are energy detection, decision theory, and pattern recognition. This study seeks out a new classification method based on the use of prior knowledge to continually train a hierarchical neural network to group similar signals into classes. A human programs a set of rules into the neural network that allow it to quickly group signals into classes. This greatly expedites the learning process and the accuracy of the classification results [6].

#### 2. Recognized Modulations

#### a. FMCW Modulations

This neural network is trained to recognize several different modulations. One of the important modulations that can be recognized is Frequency Modulation Continuous Wave (FMCW), which is often used in the measuring of the range and range rate of a target. There are two linear frequency modulation parts of the waveform which have positive and negative slopes. FMCW is effective as a modulation for Low Probability of intercept signals because it spreads the transmitted energy over a large bandwidth which allows good range resolution. Also, its rectangular power spectrum makes noncooperative signal interception complicated. FMCW is additionally a deterministic waveform which makes the return signal form predictable and resistant to undesired interference [6].

# b. BPSK Modulations

Another type of modulation that is commonly used is the Barker-code Binary Phase Shift Keying (BPSK). This code consists of discrete time complex sequences of finite length with a constant magnitude. It results in a periodic ambiguity function with low side lobes relative to the main lobe. The code itself is not Low Probability of Intercept; rather it is simply a sequence used to perform the phase modulation. However, it is a solid benchmark to compare the classification techniques against [6].

### c. Polyphase Modulations

Polyphase is a type of modulation with more than two phases that includes the Frank code and the P1 through P4 phase codes. The Frank code is similar to linear frequency modulation and Barker codes, but it has been successfully integrated into Low Probability of Intercept radars. It is derived from a step approximation to a linear frequency modulation waveform with M frequency steps and M samples per frequency. Much like Frank codes, the P1, P2, P3, and P4 codes are also derived from linear

frequency modulated waveforms. They are also made up of discrete phases of the linear chirp waveform, but they achieve lower side lobe levels. For all Polyphase codes, the time spent at any phase state is constant within the code period [6].

#### d. Polytime Modulations

The final modulation group is Polytime. This consists of the T1, T2, T3, and T4 codes which also aid in the estimation of stepped frequency modulations. Unlike Polyphase codes, these Polytime codes vary the time spent at each phase state throughout the code period. Polytime approximations improve in quality when the total number of phase states is higher. Unfortunately, this tends to complicate waveform generation by reducing the time spent at any particular phase state. The phase state durations change with time and the shortest duration sets the bandwidth [6].

### **3.** Modulation Results

Dr. Phillip Pace of the Naval Postgraduate School tested these modulations against each other using set inputs. Table 2 shows an (non-optimized) example of using Quadrature Mirror Filter Bank detection-classification signal processing. The maximum neural network output is used for each classification vector, presented as a Confusion Matrix (CM). The first and second blocks show the results of testing the network with the training signals. The third block shows the results of testing the network with the training signals but with various signal-to-noise ratios. The fourth block shows the results when testing the network with the training signals but with the training signals with variations in the modulation parameters. The columns of this Confusion Matrix indicate the input modulation type, the rows show what was assigned by the neural network, and the diagonals give the percent chance that the proper modulation was chosen.

| Training Signal CM            | BPSK              | FMCW               | FRANK             | P4             | PT1             |

|-------------------------------|-------------------|--------------------|-------------------|----------------|-----------------|

| BPSK                          | 100%              | 0%                 | 0%                | 0%             | 0%              |

| FMCW                          | 0%                | 100%               | 0%                | 0%             | 0%              |

| FRANK                         | 0%                | 0%                 | 100%              | 0%             | 0%              |

| P4                            | 0%                | 0%                 | 0%                | 100%           | 0%              |

| PT1                           | 0%                | 0%                 | 0%                | 0%             | 100%            |

| Training Noise CM             | BPSK              | FMCW               | FRANK             | P4             | PT1             |

| BPSK                          | 100%              | 0%                 | 0%                | 0%             | 0%              |

| FMCW                          | 0%                | 100%               | 0%                | 0%             | 0%              |

| FRANK                         | 0%                | 0%                 | 100%              | 0%             | 0%              |

| P4                            | 0%                | 0%                 | 0%                | 100%           | 0%              |

| PT1                           | 0%                | 0%                 | 0%                | 0%             | 100%            |

| Test Modulation CM            | BPSK              | FMCW               | FRANK             | P4             | PT1             |

| BPSK                          | 80%               | 95%                | 45%               | 43%            | 0%              |

| FMCW                          | 20%               | 5%                 | 23%               | 18%            | 0%              |

| FRANK                         | 0%                | 0%                 | 10%               | 23%            | 30%             |

| P4                            | 0%                | 0%                 | 20%               | 18%            | 5%              |

| PT1                           | 0%                | 0%                 | 3%                | 0%             | 65%             |

|                               | 070               | 070                | 0,0               | 0,0            | 0070            |

| Test Noise CM                 | BPSK              | FMCW               | FRANK             | P4             | PT1             |

|                               |                   |                    |                   |                |                 |

| Test Noise CM                 | BPSK              | FMCW               | FRANK             | P4             | PT1             |

| Test Noise CM<br>BPSK         | BPSK<br>92%       | FMCW<br>16%        | FRANK<br>1%<br>3% | P4 2%          | PT1<br>0%       |

| Test Noise CM<br>BPSK<br>FMCW | BPSK<br>92%<br>8% | FMCW<br>16%<br>72% | FRANK<br>1%<br>3% | P4<br>2%<br>4% | PT1<br>0%<br>0% |

Table 2.QMFB Classification Results.

# E. SUMMARY