# **Calhoun: The NPS Institutional Archive**

# **DSpace Repository**

Theses and Dissertations

1. Thesis and Dissertation Collection, all items

1995-09

# A CMOS current-mode full-adder cell for multi-valued logic VLSI

# Barton, Robert James

Monterey, California. Naval Postgraduate School

http://hdl.handle.net/10945/7557

Downloaded from NPS Archive: Calhoun

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

## NAVAL POSTGRADUATE SCHOOL Monterey, California

### THESIS

#### A CMOS CURRENT-MODE FULL-ADDER CELL for MULTI-VALUED LOGIC VLSI

by

Robert J. Barton III

September, 1995

Thesis Advisor: Co-Advisor: Douglas J. Fouts Amr Zaky

Approved for public release; distribution is unlimited.

Thesis B242344 DUDLEY KNOX LIBRARY NAVAL POSTGRADUATE SCHOOL MONTEREY CA 93943-5101

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |                                                         | Form Approved<br>OMB No. 0704-0188                             |    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------|----|--|

| Pater expering budget for this context of information is estimated to alrenge. This year response, including to white weeking instructions, subcriting and as accurate<br>gataving and managing the data events and ampairing and another primations. Send commands in priparty the subcritic of this<br>subcritic of information, including suggestions for instance in the submatrix Send and another is priparty the subset of this<br>budget of information. Including suggestions for instance in the submatrix Send another Discusses for information Operations and Haynow. This demons<br>Desire signals subset 104, Autopen, UK-2022 442, and the for of Managinant and Sangar, Papaven Richards Inglical Difference in the subset of<br>the subset of the subset of Autopen, UK-2020.                                                                                                                                                                                                                                                                                                                                                                                       |                                                             |                                                         |                                                                |    |  |

| 1. AGENCY USE ONLY (Leave Blank)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2. REPORT DATE<br>September 1995                            | 3. REPORT TYPE AND DATE<br>Master's Thesis              | S COVERED                                                      | -  |  |

| A CMOS CURRENT-M<br>VALUED LOGIC VLSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LL FOR MULTI-                                               | 5. FUNDING NUMBERS                                      |                                                                |    |  |

| L. AUTHORES<br>Barton III, Robert James                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                             |                                                         |                                                                |    |  |

| 7. PERFORMING ORGANIZATION NAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | E(S) AND ADDRESS(ES)                                        |                                                         | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER                    |    |  |

| Naval Postgraduate Scho<br>Monterey, CA 93943-500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |                                                         |                                                                |    |  |

| 9. SPONSORING/ MONITORING AGEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             | 10. SPONSORING/ MONITORING<br>AGENCY REPORT NUMBER      |                                                                |    |  |

| T. EXPERIMENTATION FOR THE ADDRESS OF THE UNITED STATES GOVERNMENT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |                                                         |                                                                |    |  |

| Tax DEFTREMINON / AWALENDUTY STATEMENT<br>Approved for public release; distribution is unlimited.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |                                                         |                                                                |    |  |

| TA MSTMET Means 200 end)<br>The MSTMET Means 200 end)<br>This basis describes the design and implementation of a carry save adder cell for multi-valued<br>logic VLSI. A four-valued system was chosen and the logic was analyzed and minimized using the<br>HAMLET CAD tool [1]. SPICE was used to design and simulate the required behavior of the current-<br>mode CMOS circuits. A VLSI test and evaluation integrated circuit was simplemented with MAGIC and<br>fabricated through the MOSIS service. The completed IC was tested and evaluated using a specially<br>designed binary-to-multi-valued logic converter and decoder. Engineering modifications to the original<br>current-mode inverter cells used by HAMLET were made leading to significant power savings in a<br>complete design. The fabricated device performed as predicided by SPICE simulation. Exhaustive<br>functional testing produced correct steady-state output signals for all cases of input loadings. Finally, we<br>show HAMLET minimization heuristics are not efficient in the design of adder cells by comparison with<br>an alternative modulo 4 carry save adder cell in current-mode CMOS. |                                                             |                                                         |                                                                |    |  |

| ta signater reinen<br>VLSI, Multi-Valued Logic, Current-Mode CMOS, High-Radix Circuitry<br>R. Multi-Valued Logic, Current-Mode CMOS, High-Radix Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |                                                         |                                                                |    |  |

| 17. SECURITY CLASSIFICATION<br>OF REPORT<br>Unclassified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18. SECURITY CLASSIFICATION<br>OF THIS PAGE<br>Unclassified | 19. SECURITY CLASSIFICAT<br>OF ABSTRACT<br>Unclassified | Unlimited                                                      |    |  |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             | i                                                       | Standard Form 298 (Rev. 2-89<br>Prescribed by ANSI Std. 239-18 | 9) |  |

ii

Approved for public release; distribution unlimited.

#### A CMOS CURRENT-MODE FULL-ADDER CELL FOR MULTI-VALUED LOGIC VLSI

Robert James Barton III Lieutenant, United States Navy B.S., United States Naval Academy, 1985

Submitted in partial fulfillment of the requirements for the degrees of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

and

#### MASTER OF SCIENCE IN COMPUTER SCIENCE

from the

NAVAL POSTGRADUATE SCHOOL

1 Koois B242341 C. 2

#### ABSTRACT

The rapidly expanding fields of digital control and data signal processing require high performance compact arithmetic circuitry. In particular, the multiplication of large data words currently requires a network of carry-save adders to perform the addition of sets of partial products. This method suffers with scalability, particularly in the required die area and power required for carry-save adder trees. One possible solution is to take advantage of a compact design incorporating a high-radix signed number system.

This thesis describes the design and implementation of a carry save adder cell for multi-valued logic VLSI. A four-valued system was chosen and the logic was analyzed and minimized using the HAMLET CAD tool [1]. SPICE was used to design and simulate the required behavior of the current-mode CMOS circuits. A VLSI test and evaluation integrated circuit was implemented with MAGIC and fabricated through the MOSIS service. The completed IC was tested and evaluated using a specially designed hinary-tomulti-valued logic converter and decoder. Engineering modifcations to the original current-mode inverter cells used by HAMLET were made leading to significant power savings in a complete design. The fabricated device performed as predicted by SPICE simulation. Exhaustive functional testing produced correct steady-state output signals for all cases of input loadings. Finally, we show HAMLET minimization heuristics are not efficient in the design of adder cells by comparison with an alternative modulo 4 carry save adder cell in current-mode CMOS.

vi

#### TABLE OF CONTENTS

| Ι.  | INT |       | JCTION                                               |     |

|-----|-----|-------|------------------------------------------------------|-----|

|     | Α.  | HIST  | TORICAL PERSPECTIVE                                  | 1   |

|     | Β.  | CUR   | RRENT WORK                                           |     |

|     | C.  | MUI   | LTIPLE VALUED LOGIC ARITHMETIC                       | 4   |

| Π.  | DE  |       | OF MODULO 4 ADDER CELL                               | 7   |

|     | Α.  |       | CRIPTION OF THRESHOLD DETECTORS AND CURRENT          |     |

|     |     | GEN   | VERATORS                                             |     |

|     | В.  | HAN   | MLET - A CAD TOOL FOR MVL DESIGN                     | 11  |

|     | C.  | MIN   | IMIZATION OF LITERALS USING HAMLET HEURISTICS        | 15  |

| Ш.  | IM  |       | ENTATION                                             |     |

|     | Α.  |       | RRENT-MODE CMOS LOGIC                                |     |

|     | В.  | LIM   | ITATIONS OF THE PRESENT CAD TOOL - HAMLET            | 18  |

|     |     | 1.    | HAMLET's PLA Generator module                        | 18  |

|     |     | 2.    | Power Consumption                                    | 18  |

|     |     | 3.    | Scalability                                          | 19  |

|     | C.  |       | GINEERING MODIFICATIONS TO STEP-UP, STEP-DOWN, AN    |     |

|     |     | COL   | LUMN GENERATOR CELLS                                 | 19  |

|     |     | 1.    | Transistor Sizing                                    |     |

|     |     | 2.    | Improved Logic Values and Switching Thresholds       | 20  |

|     |     | 3.    | Simulation of New Cells                              | 21  |

|     |     | 4.    | Simulation of a Combined Minterm Using the New Cells | 22  |

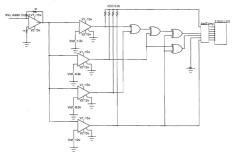

|     | D.  | CIR   | CUIT LAYOUT                                          | 23  |

|     |     | 1.    | Basic Floor Plan                                     | 23  |

|     |     | 2.    | Input Current Mirror Design and Layout               |     |

|     |     | 3.    | VDD and Ground Rail Considerations                   |     |

|     |     | 4.    | Simulation of Completed Chip Design                  | 25  |

| IV. | TE  | TING  | AND EVALUATION OF MULTI-VALUED LOGIC (MOD4) CA       | RRY |

|     | SA  | VE AD | DDER                                                 | 27  |

|     | Α.  | DES   | SIGN OF MODULO FOUR TESTBENCH                        | 27  |

|     |     | 1.    | Binary-to-Ideal Current Source Conversion            |     |

|     |     | 2.    | Current Decoding at Outputs                          |     |

|     | Β.  | SUN   | MMARY OF TEST RESULTS                                |     |

|     |     | 1.    | Static Power Tests                                   |     |

|     |     | 2.    | Functional Testing                                   |     |

|     |     | 3.    | Transient Analysis                                   |     |

|     |     | 4.    | Results Discussion                                   |     |

| V.  | CO  | NCLU  | SIONS                                                | 35  |

|     | Α.  | HAN   | MLET RECOMMENDATIONS                                 |     |

|     |     | 1.    | Port to an X-Windows Application                     |     |

|     |     | 2.    | Design of Current-Mode Logic Cells                   |     |

|     | D   | A NT  | AT TERMATIVE DESIGN FOR A RADIY & ADDER CELL IN      |     |

B. AN ALTERNATIVE DESIGN FOR A RADIX-4 ADDER CELL IN

|     | CURRENT-MODE CMOS                                                  | 36 |

|-----|--------------------------------------------------------------------|----|

|     | <ol> <li>A Different Approach</li> </ol>                           |    |

|     | <ol><li>Simulation of Alternative Design</li></ol>                 |    |

|     | <ol><li>Conclusions of Alternative Design Method</li></ol>         | 40 |

| C.  | RECOMMENDATIONS FOR FURTHER STUDY                                  |    |

|     | <ol> <li>Charged-Coupled Device (CCD) Logics</li> </ol>            |    |

|     | <ol><li>Resonant-Tunneling Diodes (RTD) Logics</li></ol>           |    |

|     | <ol><li>Hierarchical MVL Design for Symmetric Functions.</li></ol> | 41 |

|     | 4. Modulo 16 (hexadecimal) Current Mode CMOS Full Adder Cell       | 41 |

| REF | FERENCES                                                           | 43 |

| API | PENDIX                                                             | 45 |

| Α.  | HAMLET REPORT - ORIGINAL SOP EXPRESSION                            | 45 |

| Β.  | HAMLET REPORT - DEUCK & MILER MINIMIZATION                         | 48 |

| C.  | HAMLET REPORT - SIMULATED ANNEALING MINIMIZATION                   | 50 |

| D.  | SPICE FILE - STEP UP GENERATOR                                     |    |

| E.  | SPICE FILE - STEP DOWN GENERATOR                                   | 54 |

| F.  | SPICE FILE - COLUMN OUTPUT GENERATOR                               | 56 |

| G.  | SPICE FILE - TERM 3*X(2,2)Y(3,3)C(2,2)                             | 58 |

| H.  | SPICE FILE - CURRENT MIRROR                                        | 62 |

| I.  | SPICE INPUT FILE - MODULO 4 ADDER DESIGN                           | 65 |

| J.  | MAGIC LAYOUTS                                                      | 68 |

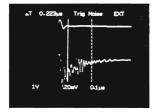

| Κ.  | SCOPE PHOTOGRAPHS - TRANSIENT ANALYSIS                             | 77 |

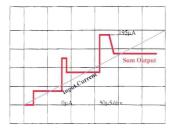

| L.  | TRANSIENT ANALYSIS SCOPE PLOT - MODULO 4 ADDER CELL                | 81 |

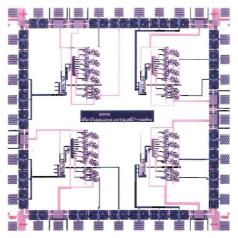

| M.  | FABRICATION PHOTOGRAPH                                             | 82 |

| INT | TIAL DISTRIBUTION LIST                                             |    |

#### LIST OF FIGURES

| 2.1 CMOS Inverter With Current Input                                           | 7  |

|--------------------------------------------------------------------------------|----|

| 2.2 Transfer Characteristics for Current Input Single Stage and Two-Stage CMOS |    |

| Inverters                                                                      | 9  |

| 2.3 Step Down Function Generator                                               | 9  |

| 2.4 Step Up Function Generator                                                 | 10 |

| 2.5 Transfer Curves for Function Generators                                    | 10 |

| 2.6 Example of a 2 Variable 4-Valued Function f(X)                             | 11 |

| 2.7 Mapping for Carry Save Adder Sum Function in Radix 4                       | 12 |

| 2.8 Mapping for Carry Save Adder Carry Out Function in Radix 4                 | 14 |

| 3.1 Current Logic Levels                                                       | 17 |

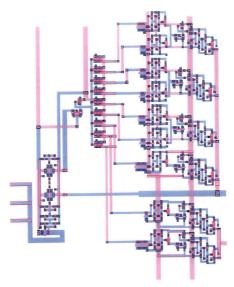

| 3.2 Final Layout of Design                                                     | 23 |

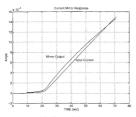

| 3.3 Current Mirror Response                                                    |    |

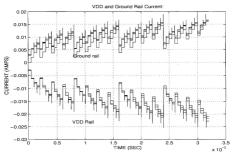

| 3.4 Current Measurements at VDD and Ground Rails                               | 25 |

| 3.5 Complete Functional Test                                                   | 26 |

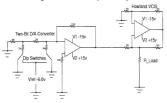

| 4.1 Testbench Input Circuitry                                                  |    |

| 4.2 Testbench Output Circuitry                                                 |    |

| 4.3 Measured and SPICE Simulation of No Load Static Power Consumption          |    |

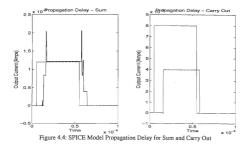

| 4.4 SPICE Model Propagation Delay for Sum and Carry Out                        |    |

| 5.1 Current Input Complementary Pass Gate                                      | 37 |

| 5.2 Block Diagram of New Modulo 4 Adder                                        |    |

| 5.3 Chip Layout of Alternative Design                                          |    |

| 5.4 Transient Analysis of Alternate Design                                     |    |

| A.1 Step Up Generator Cell                                                     |    |

| A.2 Step Down Generator Cell                                                   |    |

| A.3 Column Output Generator Cell                                               |    |

| A.4 Term 3*X(2,2)Y(3,3)C(2,2)                                                  |    |

| A.5 Current Mirror                                                             |    |

| A.6 HAMLET Design Modulo 4 Adder                                               |    |

| A.7 Current-Input Complementary Transmission Gate                              |    |

| A.8 Alternate Design Modulo 4 Adder                                            |    |

| A.9 Fabrication Layout Alternate Design Adder                                  |    |

| A.10 T <sub>f</sub> Sum 3->0                                                   |    |

| A.11 Tr Sum 0->3                                                               |    |

| A.12 T <sub>ndf</sub> Sum 3->0                                                 | 78 |

| A.13 T <sub>pdr</sub> Sum 0->3                                                 |    |

| A.14 Tf Carry Out 1->0                                                         |    |

| A.15 T, Carry Out 0->1                                                         |    |

| A.16 T <sub>pdf</sub> Carry Out 1->0                                           | 80 |

| A.17 Tpdr Carry Out 0->1                                                       | 80 |

| A.18 Sum 0->3 Power Transients                                                 |    |

| A.19 Die Photo Modulo 4 Adder Cell                                             | 82 |

x

-

#### LIST OF TABLES

| 2.1 SOP Expression for Sum Function                           | 13 |

|---------------------------------------------------------------|----|

| 2.2 SOP for Carry Function                                    | 15 |

| 2.3 Reduced SOP for Sum Function                              | 16 |

| 2.4 Reduced SOP for Carry Function                            | 16 |

| 3.1 New Logic and Threshold Current Values                    | 20 |

| 3.2 New Step Up and Step Down Generator Output Current Design | 21 |

| 3.3 Timing and Power Simulation of Cells                      | 21 |

| 3.4 Term 3 X(2,2) Y(3,3) C(2,2)                               | 22 |

| 4.1 Component Static Power                                    | 29 |

| 4.2 Full Power Measurements                                   | 31 |

| 4.3 Functional Test for Device 1                              | 32 |

| 4.4 Propagation Delay                                         | 33 |

xii

#### Acknowledgement

For Pam and Baby Kay.

#### I. INTRODUCTION

#### A. HISTORICAL PERSPECTIVE

Circuits which implement binary logic can be characterized by the effect of the circuit itself on the signal or signals being processed. A restoring circuit is capable of interpreting logic signals and then generating an output which is very narrowly constrained to the given signal space. In logic function implementations in higher radix(r) systems, the signal space does not significantly increase, whereas the number of required logic levels represented within the signal space increases in r. Narrower signal logic bands within the circuit present greater difficulty in maintaining functional integrity across cascaded non-restoring partitions within the circuit.[2]

In the latter half of the 1970s, a great deal of interest in ternary logic devices was prevalent. The design approach was, and in many instances remains, implementation of ternary (or higher) radix logic using binary components. For example, in a ternary system, the physical medium must have three equiprobable states and the distances between the states must be equal, or very nearly so. The use of a **cyclic** physical medium would allow optimal design of such a system. Alas, quantifiable cyclic phenomenon is extremely rare in the field of electronic devices. The approach then is to use the cyclic properties of binary circuits in such a way as to represent higher radices. In general, these circuits can be **voltage mode** or **current mode**. During this period various circuits were proposed using TLL(Transistor-Transistor Logic), ECL(Emitter-Coupled Logic), and CMOS [3]

By the end of the decade Current Mode Logic (CML) was regarded as a simple, compact solution for higher radix arithmetic circuits. Several test example devices of full adder circuits were designed and implemented in current-mode CMOS, mainly in modulo 4. Greater speed performance was achievable using high-speed ECL, but the primary goal was to reduce circuit size and thus reduce cost and power requirements for arithmetic devices operating on large data words.[4]

1

In order to achieve greater speeds, GaAs MESFET logic was becoming an important area of research for multi-valued circuits. Circuits which are general, ic., expandable to higher radices, and able to perform at low power with good noise margin performance are highly desirable. An approach presented by Tront [5] in 1979 included using MESFETS in which the individual transistors on the device had varying pinchoff voltages, at least one at each logic level desired. The difficulty with this approach is that Vp is a property which is only controlled at fabrication, either through channel thickness or doping concentrations. Even now, fabrication facilities have difficulty keeping threshold voltage within 50% of design tolerances.

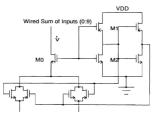

During the late 1970s and into the 1980s, a great deal of work was done on multiple valued logic theory and modeling, as well as minimization techniques, but very few physical test devices were implemented. It is the explosion of progress in fabrication technology that allows much tighter control of device intrinsic properties. In the early 1980s Charge-Coupled Device logic became of interest. CCD implementation is in the category of charge-mode circuits. These circuits have many similarities with current-mode logic design, most significantly, the basic gate required for implementation is a common storage well. The storage well acts as a kind of "logical accumulator", much in the same way current mode CMOS makes extensive use of the "wired sum" to represent various signal levels.

By the end of the 1980s, current-mode CMOS was gaining in popularity for multivalued function implementations. First, integrated circuit process technology is the same for binary CMOS as well as current-mode CMOS. This allows for the integration of multivalued current-mode modules and binary logic circuits on the same VLSI device. Utilizing bi-directional current-mode CMOS formed the basis for the first presented CAD tool for implementing multi-valued functions in VLSI. This CAD tool was developed largely at Naval Post Graduate School, and is called HAMLET. HAMLET is a heuristics analyzer and CAD tool for multi-valued programmable logic arrays. In its current form, current mode CMOS is used exclusively for function implementation. The advantages are simplicity of design and very inexpensive fabrication costs. In the future, it is envisioned that HAMLET will be capable of implementations in CCD logic, and possibly an implementation based upon resonant tunneling diode devices (RTDs).

#### B. CURRENT WORK

In recent years, continued improvements in VLSI fabrication processes have led to a renewed interest in current-mode CMOS high-radix arithmetic circuits. Of particular importance is the development of high speed compact multiplier circuits for the rapidly expanding fields of digital signal processing and digital control systems. In most modern high-speed arithmetic units, multiplication of long data words is performed by simultaneously generating sets of partial products and then summing them together with a network of carry save adders (CSAs) in an operation that is referred to as "row reduction." Although the network of CSAs lends itself very well to pipelining in high-speed processors, binary multipliers using the Wallace Tree [6] approach suffer from scalability problems. Scalability difficulties can be overcome by utilizing a high-radix signed number system to significantly reduce the number of transistors and the die area required for large data-word arithmetic.

Presently, current-mode CMOS logic is not a suitable solution for the generation of partial products in a large multiplier circuit. One alternative is to use binary CMOS circuits to implement a modification of Booth's algorithm[7][8]. However, the design of high-radix adders lends itself well to current-mode CMOS, primarily because of the wired sum[9] function. One of the key elements of the adder circuit is the threshold detector[10]. This particular circuit has, in the past, proved to be difficult to scale down to minimum VLSI implementation device sizes. With the vast and continuing improvements in CMOS fabrication processes, this design problem can be minimized. Of recent interest is the development of alternative low-power high-speed threshold detector circuits such as those found in CML current-mode full adders[11]. In this thesis we demonstrate the design and implementation of a radix-4, carry-save adder cell for multi-valued VLSI. The adder receives current inputs X, Y, and Carry<sub>IN</sub>, generating the Sum and Carry<sub>OUT</sub> outputs. The Carry<sub>IN</sub> input of the carry save adder accepts all possible radix-4 inputs (0:3) so that it may be used as a three-to-two row reduction unit in the CSA adder network previously described.

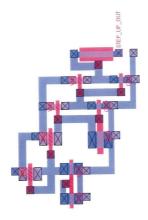

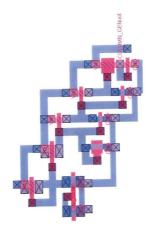

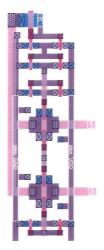

The first test IC was designed and implemented using the HAMLET cad tool for multivalued logic expressions. A second test IC of the same radix and function was designed and implemented without the assistance of the CAD tool,, using a different technique which takes advantage of the symmetrical property of the addition logic. The alternative design actually uses two radices, modulo-4 for input and output, and modulo-12 logic within the device.

#### C. MULTIPLE VALUED LOGIC ARITHMETIC

As previously mentioned, high-radix multiplication does not lend itself to currentmode CMOS, and is therefore not discussed in this thesis. Before an adder can be designed in a high-radix system (greater than binary), we need a convenient way to express the logic combinations of the inputs. The expression which describes the sum function in any radix is:

$$SUM\{f(C_i, X_iY_i)\} = C_i(XOR)X_i(XOR)Y_i \qquad (1.1)$$

This expression generates a set of product terms of the form:

$$SUM_{\mu} = 1 * {}^{3}C^{31}X^{31}Y^{1} \qquad (1.2)$$

This notation translates as for an input at C of 3, an input at X of 1,2, or 3, and an input at Y of 1, generate an output of 1. Thus, the sum function is the summation of this set of product terms:

$$SUM \left\{ f \left( C_i X_i Y_i \right) \right\} = \sum_{k=1}^{n} SUM_k \qquad (1.3)$$

In current mode CMOS, the distinction between levels of logic at the inputs is accomplished by a threshold detector. The output value for each term in the sum is realized by a current generator. To accomplish the required summation of the product terms, the outputs of the current generators for each product term are physically "wired together", thus the notion of a "wired sum" in current mode CMOS multiple-valued VLSI. In the following chapter we discuss the use of the CAD tool HAMLET and develop the equations and device modules for the threshold detectors and current generators.

#### II. DESIGN OF MODULO 4 ADDER CELL

Described herein is the design of a radix-4 carry save adder cell utilizing the CAD tool HAMLET. The ideal threshold detectors and current generators are also derived. We show the result of HAMLET minimization heuristics on a set of product terms that fully describes the required sum and carry-out functions.

#### A. DESCRIPTION OF THRESHOLD DETECTORS AND CURRENT GENERATORS

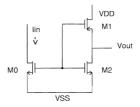

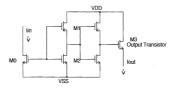

At the core of the current-mode circuits required to implement an MVL expression is a CMOS inverter with a *current* input.

Figure 2.1: CMOS Inverter With Current Input

In Figure 2.1, The nFET device M0 operates in saturation because  $V_{DS} = V_{GS}$  and  $V_{DS} > V_T$ . Ignoring the Early voltage and bulk effects which are minimal, the saturation value of the drain current is given by:

$$I_{D} = K(V_{GS} - V_{t})^{2} \qquad (2.1)$$

where the process-dependent constant K can be determined by:

$$K = 1/2(u_n C_{ox}(W/L))$$

(2.2)

Since the drain current  $I_d$  is the input current, then the operating point at which the nMOS device M0 becomes saturated is found by:

$$I_{SW} = C(V_{SW} - V_t)^2(W/L)$$

(2.3)

$I_{SW}$  and  $V_{SW}$  refer to the "switching" current and switching voltage respectively. When M0 is saturated, the input voltage to the CMOS inverter stage is high, both the pMOS (M1) and the nMOS(M2) devices are in the saturation region such that.

$$I_{DSp} = -I_{DSn}$$

(2.4)

$$I_{DSp} = K_p (V_{SW} - V_{DS} - V_{tp})^2$$

(2.5)

$$I_{DSn} = K_n (V_{SW} - V_{tp})^2$$

(2.6)

Since  $K_n = K_p$  on the same chip, solving equations 2.5 - 2.7 for switching voltage vields:

$$V_{SW} = (V_{DS} + V_{tp} + V_{tp})/2$$

(2.7)

As seen by equation 2.7 the switching voltage is a function of the threshold voltages of the transistors M1 and M2, which is constant through the chip. Thus, the switching voltage of these inverters are constant on the same chip. With a constant switching voltage  $V_{SW}$ , the switching current  $I_{SW}$  of equation 1.4 is strictly a function of transistor geometry (W/L). Therefore the inverter will generate a  $V_{OUT}$  of 0 when the designed  $I_{SW}$  is experienced at the drain of M0. In practice, we will use two inverter stages for a "sharper" transition at Vout.[12][10]

Figure 2.2: Transfer Characteristics for Current Input Single Stage and Two-Stage CMOS Inverters

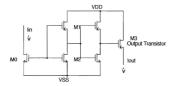

The basic cells used to implement the current mode logic consist of the current-input CMOS inverter with the output connected to a single MOS or pMOS transistor (figure 2.11). Since the inverter output will produce  $V_{OLT}$  >> threshold voltage of M3, this circuit acts as a constant current source when the threshold current  $I_{SW}$  is detected. The step-down generator produces a constant  $I_{out}$  when the input current is **less than** the switching current, else 0. The step-up generator has an output current  $I_{out} = 0$  unless the input current is **greater than**  $I_{SW}$ .

Figure 2.3: Step Down Function Generator

Figure 2.4: Step Up Function Generator

Figure 2.5: Transfer Curves for Function Generators

The column output generator is actually a step down function generator in which the geometry of the nMOS transistor M3 is proportioned to produce the desired output current for its term. The output currents from various step up and step down generators are connected to the input of the column generator, which in turn generates its output value only when the input current is 0.

#### B. HAMLET - A CAD TOOL FOR MVL DESIGN

To realize a logic function in multi-valued log (MVL), a design method is required to develop the abstraction into a format on which CAD tools can perform heuristics. Unlike binary logic design, MVL of radix greater than 2 quickly becomes difficult to conceptualize. For example, while a two-input NAND gate is readily described in binary logic, there is no "symbol" to functionally describe a two-input NAND gate in a logic system of 6 variables.

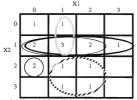

The MVL CAD tool HAMLET uses a sum-of-products (SOP) expression as formatted input[]. Since HAMLET will minimize the SOP expression, any valid SOP expression which completely describes the functionality of the design is sufficient. The SOP is derived from a mapping technique which resembles the familiar Karauagh Map method.

Let  $X = \{x_1, x_2, ..., x_n\}$  be a set of n variables in a logic system of radix r, where  $x_i$  takes on values from  $R = \{0, 1, 2, ..., r-1\}$ . The function f(X) can be fully described in the following example:

Figure 2.6: Example of a 2 Variable 4-Valued Function f(X)

The groups in Figure 2.5 represent implicants of the function *f*(*X*). The SOP representation for this particular choice of implicants in the format for HAMLET would be the following:

$$f(x_1x_2) = 1^0 x_1^{00} x_2^{0} + 1^1 x_1^{10} x_2^{1} + 1^0 x_1^{21} x_2^{1} + 1^0 x_1^{31} x_2^{1} + 1^1 x_1^{22} x_2^{3} + 2^0 x_1^{02} x_2^{2} (2.8)$$

The single-bit adder has 3 inputs, namely, a carry in  $C_i$ , 1st addend  $X_i$ , 2nd addend  $Y_i$ , and 2 outputs, the sum  $S_i$ , and the carry out  $C_{or}$ . Recalling for the full adder:

$$SUM{f(C_iX_iY_i)} = C_i(XOR)X_i(XOR)Y_i$$

(2.9)

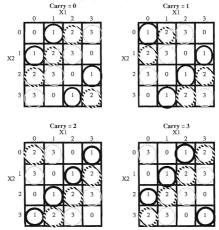

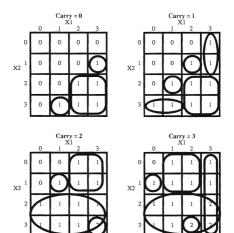

By utilizing the mapping technique described earlier, the SUM function for the carry save adder in radix 4 can be completely described by:

Figure 2.7: Mapping for Carry Save Adder Sum Function in Radix 4

In order for the expression to be accepted into the HAMLET tool, the mappings described above must first be translated into the following SOP expression:

#### TABLE 2.1: SOP Expression for Sum Function

| 1 0 1/1 1) 0 2/0 0) * 2/0 0)      | 2 * 1(0 0) * 0(0 0) * 0(0 0)           |

|-----------------------------------|----------------------------------------|

| 1 * x1(1,1) * x2(0,0) * x3(0,0)   | +2 * x1(0,0) * x2(0,0) * x3(2,2)       |

| + 2 * x1(2,2) * x2(0,0) * x3(0,0) | +3 * x1(1,1) * x2(0,0) * x3(2,2)       |

| + 3 * x1(3,3) * x2(0,0) * x3(0,0) | + 1 * x1(3,3) * x2(0,0) * x3(2,2)      |

| +1 * x1(0.0) * x2(1.1) * x3(0.0)  | +3 * x1(0,0) * x2(1,1) * x3(2,2)       |

| + 2 * x1(1,1) * x2(1,1) * x3(0,0) | +1*x1(2,2)*x2(1,1)*x3(2,2)             |

| +3 * x1(2,2) * x2(1,1) * x3(0,0)  | +2 * x1(3,3) * x2(1,1) * x3(2,2)       |

|                                   |                                        |

| +2 * x1(0,0) * x2(2,2) * x3(0,0)  | + 1 * x1(1,1) * x2(2,2) * x3(2,2)      |

| + 3 * x1(1,1) * x2(2,2) * x3(0,0) | +2 * x1(2,2) * x2(2,2) * x3(2,2)       |

| + 1 * x1(3,3) * x2(2,2) * x3(0,0) | + 3 * x1(3,3) * x2(2,2) * x3(2,2)      |

| + 3 * x1(0.0) * x2(3.3) * x3(0.0) | +1 * x1(0,0) * x2(3,3) * x3(2,2)       |

| + 1 * x1(2,2) * x2(3,3) * x3(0,0) | +2 * x1(1,1) * x2(3,3) * x3(2,2)       |

| + 2 * x1(3,3) * x2(3,3) * x3(0,0) | + 3 * x1(2,2) * x2(3,3) * x3(2,2)      |

| +1 * x1(0,0) * x2(0,0) * x3(1,1)  | +3 * x1(0,0) * x2(0,0) * x3(3,3)       |

| +2 * x1(1,1) * x2(0,0) * x3(1,1)  | +1*x1(2,2)*x2(0,0)*x3(3,3)             |

| +3 * x1(2,2) * x2(0,0) * x3(1,1)  | +2 * x1(3,3) * x2(0,0) * x3(3,3)       |

| + 2 * x1(0,0) * x2(1,1) * x3(1,1) | +1 * x1(1,1) * x2(1,1) * x3(3,3)       |

| + 3 * x1(1,1) * x2(1,1) * x3(1,1) | + 2 * x1(2,2) * x2(1,1) * x3(3,3)      |

| +1*x1(3,3)*x2(1,1)*x3(1,1)        | + 3 * x1(3,3) * x2(1,1) * x3(3,3)      |

| +3 * x1(0,0) * x2(2,2) * x3(1,1)  | +1 * x1(0,0) * x2(2,2) * x3(3,3)       |

|                                   |                                        |

| + 1 * x1(2,2) * x2(2,2) * x3(1,1) | + 2 * x1(1,1) * x2(2,2) * x3(3,3)      |

| + 2 * x1(3,3) * x2(2,2) * x3(1,1) | + 3 * x1(2,2) * x2(2,2) * x3(3,3)      |

| + 1 * x1(1,1) * x2(3,3) * x3(1,1) | + 2 * x1(0,0) * x2(3,3) * x3(3,3)      |

| + 2 * x1(2,2) * x2(3,3) * x3(1,1) | +3 * x1(1,1) * x2(3,3) * x3(3,3)       |

| +3 * x1(3,3) * x2(3,3) * x3(1,1)  | +1*x1(3,3)*x2(3,3)*x3(3,3);            |

| + 5 · x1(5,5) · x2(5,5) * X5(1,1) | $\pm 1 = x1(3,3) = x2(3,3) = x3(3,3);$ |

In a similar fashion, the following mapping fully describes the carry out (Co) function:

Figure 2.8: Mapping for Carry Save Adder Carry Out Function in Radix 4

The translated SOP expression resulting from this mapping is:

#### TABLE 2.2: SOP for Carry Function

| 1 * x1(3,3) * x2(1,1) * x3(0,0)   | + 1 * x1(1,1) * x2(1,1) * x3(2,2)  |

|-----------------------------------|------------------------------------|

| + 1 * x1(1,1) * x2(3,3) * x3(0,0) | + 1 * x1(0,3) * x2(2,3) * x3(2,2)  |

| + 1 * x1(2,3) * x2(2,3) * x3(0,0) | + 1 * x1(3,3) * x2(3,3) * x3(2,2)  |

| + 1 * x1(3,3) * x2(0,1) * x3(1,1) | + 1 * x1(1,2) * x2(0,1) * x3(3,3)  |

| + 1 * x1(2,2) * x2(1,1) * x3(1,1) | + 1 * x1(0,0) * x2(1,1) * x3(3,3)  |

| + 1 * x1(1,1) * x2(2,2) * x3(1,1) | + 1 * x1(3,3) * x2(0,3) * x3(3,3)  |

| + 1 * x1(0,1) * x2(3,3) * x3(1,1) | + 1 * x1(0,3) * x2(2,3) * x3(3,3)  |

| + 1 * x1(2,3) * x2(2,3) * x3(1,1) | + 1 * x1(2,2) * x2(3,3) * x3(3,3); |

| + 1 * x1(2,3) * x2(0,1) * x3(2,2) |                                    |

#### C. MINIMIZATION OF LITERALS USING HAMLET HEURISTICS

Once the file containing the required SOP terms was input into the HAMLET CAD tool, a report was generated which returned the original expression with matrices representing the mappings given above for the sum and carry functions. Two heuristic minimization techniques were chosen to minimize the terms required for this design. The first was the Deuck&Miller and Proper&Armstrong heuristics[1]. This technique resulted in a reduction from 48 to 32 terms required for the sum function, and from 17 to 15 terms required to realize the carry function. Simulated Annealing minimization was also used, and HAMLET reported the same performance. In each case, the tool verifies each minimization by producing the mappings associated with each result. Copies of all HAMLET generated reports and a copy of the input data file are included in the appendix. Table 2.3 and Table 2.4 give the reduced SOP expressions returned by HAMLET which were utilized to implement the modulo-four adder. (Appendices A-C) The reduced SOP expression generated by HAMLET for the sum function:

| 1 * x1(3,3) * x2(0,1) * x3(3,3)   | +1 * x1(3,3) * x2(2,3) * x3(0,0)   |

|-----------------------------------|------------------------------------|

| + 1 * x1(3,3) * x2(0,2) * x3(2,2) | + 3 * x1(2,2) * x2(1,1) * x3(0,0)  |

| + 2 * x1(0,1) * x2(0,0) * x3(2,2) | + 1 * x1(0,1) * x2(3,3) * x3(2,3)  |

| + 1 * x1(2,3) * x2(3,3) * x3(0,0) | + 2 * x1(0,0) * x2(3,3) * x3(0,0)  |

| + 1 * x1(1,1) * x2(0,0) * x3(0,2) | + 1 * x1(3,3) * x2(3,3) * x3(3,3)  |

| + 2 * x1(0,0) * x2(2,2) * x3(1,1) | + 1 * x1(3,3) * x2(1,3) * x3(1,1)  |

| + 1 * x1(2,3) * x2(1,2) * x3(2,2) | + 3 * x1(1,1) * x2(2,2) * x3(0,0)  |

| + 1 * x1(1,3) * x2(3,3) * x3(1,1) | + 1 * x1(1,1) * x2(2,3) * x3(2,3)  |

| + 1 * x1(2,3) * x2(0,1) * x3(3,3) | + 2 * x1(2,2) * x2(0,0) * x3(0,0)  |

| + 3 * x1(0,0) * x2(1,1) * x3(2,2) | + 2 * x1(1,1) * x2(1,1) * x3(0,1)  |

| + 3 * x1(2,2) * x2(2,2) * x3(3,3) | + 3 * x1(0,0) * x2(0,0) * x3(3,3)  |

| + 1 * x1(0,1) * x2(2,3) * x3(3,3) | + 3 * x1(2,2) * x2(3,3) * x3(2,2)  |

| + 3 * x1(3,3) * x2(0,0) * x3(0,0) | + 1 * x1(1,3) * x2(1,1) * x3(3,3)  |

| + 3 * x1(2,2) * x2(0,0) * x3(1,1) | +1 * x1(0,1) * x2(0,1) * x3(1,1)   |

| + 1 * x1(0,0) * x2(2,3) * x3(0,0) | + 1 * x1(0,0) * x2(1,2) * x3(0,1)  |

| + 1 * x1(2,3) * x2(2,3) * x3(1,1) | + 1 * x1(2,3) * x2(2,2) * x3(2,2); |

|                                   |                                    |

#### TABLE 2.3: Reduced SOP for Sum Function

The reduced SOP expression for the carry function is:

| TABLE 2.4: | Reduced | SOP | for | Carry | Function |

|------------|---------|-----|-----|-------|----------|

| 1 * x1(2,2) * x2(0,1) * x3(2,3)   | + 1 * x1(2,2) * x2(1,1) * x3(1,1)  |

|-----------------------------------|------------------------------------|

| + 1 * x1(1,1) * x2(2,2) * x3(1,1) | + 1 * x1(0,2) * x2(3,3) * x3(1,2)  |

| + 1 * x1(0,2) * x2(2,2) * x3(2,2) | + 1 * x1(3,3) * x2(3,3) * x3(2,2)  |

| + 1 * x1(3,3) * x2(1,3) * x3(0,0) | + 1 * x1(1,2) * x2(3,3) * x3(0,0)  |

| + 1 * x1(0,0) * x2(1,3) * x3(3,3) | + 1 * x1(1,1) * x2(1,1) * x3(2,2)  |

| + 1 * x1(3,3) * x2(0,3) * x3(1,3) | + 1 * x1(1,3) * x2(2,3) * x3(3,3)  |

| + 1 * x1(2,2) * x2(2,2) * x3(0,1) | + 1 * x1(2,2) * x2(3,3) * x3(3,3); |

| + 1 * x1(1,1) * x2(0,1) * x3(3,3) |                                    |

#### **III. IMPLEMENTATION**

#### A. CURRENT-MODE CMOS LOGIC

To implement the MVL expression, Current-Mode CMOS was utilized. In essence, different values of current correspond to the four different logic levels. A serious drawback to this implementation is that it requires current to be constantly flowing in the circuit. The logic levels and switching points were designed as shown in figure 3.1. Currents are shown above are in µA.

Figure 3.1: Current Logic Levels

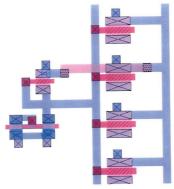

To achieve these characteristics, three components are required. The step-up and stepdown generators supply the appropriate currents to the column output generator[10]. Together, these components form one minterm of the logic equation.

The column output generator outputs a current of predetermined value if there is no current flow at its input. This input is the wired-OR of the step-up and step-down generators. The predetermined value will be one of the designed logic levels. This value is set by the gate dimensions of the output transistor. Note that the column output generator is insensitive to the value of the input current when it is present, i.e. it does not produce an output if the input is not zero. There is one column output generator per minterm.

It is the job of the step-up and step-down generators to produce zero current when an output current is desired for that term. The step-down generator cuts off the output when the input rises above the desired threshold values. These threshold values correspond to the switching points for the desired logic level and are set by the gate dimensions of the input transistor. Typically, there is a step-up and step-down generator for each input.

Figure 2.3 illustrates the use of two inverter stages between the sensing transistor of the threshold detector and the output transistor for each component. Unfortunately, both stages are required in order to produce accurate and sharp transitions at the appropriate logic current levels of input. The consequence of this design is the added propagation delay incurred across two inverters, as well as an increase in the number of transistors and the power of the device as a whole.

#### B. LIMITATIONS OF THE PRESENT CAD TOOL - HAMLET

During the implementation phase of the radix-4 adder, certain limiting features of HAMLET were discovered and re-engineered using the current MOSIS 2.0 micron design rules.

#### 1. HAMLET's PLA Generator Module

A program created by Ko[10] in support of the HAMLET project generates a PLA in current mode CMOS when given an MVL SOP expression. The resulting PLA conforms to MOSIS design rules. When originally designed, this module could be run on ISIS graphics workstations or a VAX. Currently, there is no operating version of this tool available for use on any modern graphical workstation available at NPS. However, the individual cells can still be assembled by hand, and a custom layout vice a generated PLA was created for this device.

#### 2. Power Consumption

In the present tool, the step-up function generator modules are designed to produce output currents in the range of 150uA to 180uA. Likewise, the step-down function generators produce output currents of approximately 240uA. However, these outputs only function as input to column generators, which have a switching threshold of approximately 20uA. Thus, internally, the switching currents produced by a device implemented using these cells tend to consume more power than necessary.

#### 3. Scalability

In order for a large number of terms to function correctly, a high degree of accuracy is required in the individual cells. Column generators must produce output currents that are very nearly the ideal logic values, or small errors will tend to compound quickly as terms are connected for the wired sum function. Also, the switching current levels of the threshold detectors in the step-up and step down generators should ideally "split" the ideal logic values for maximum effectiveness against introduced errors. As can be readily seen by figures 4.2-4.4 of [10], the original pla generator tool suffered from both inaccuracies in the output generator as well as at the inputs to the threshold detectors. For example, if the outputs from two column generators are wired together, and each is designed to produce a logic 1, the wired sum would be approximately 110uA, a logic 2. However, the step-up function generator reports detection of a logic 3 input beginning at 110uA. Thus, if this wired sum was to be used as an input to another term which included the step-up 3 function, an error would occur. Similar examples can be contrived for the step down function cells.

#### C. ENGINEERING MODIFICATIONS TO STEP-UP, STEP-DOWN, AND COLUMN GENERATOR CELLS

In order to improve the implementation of the MVL expression design, several engineering changes were made to the basic cells used by HAMLET and implemented in a custom layout of the final device.

#### 1. Transistor Sizing

Using new MOSIS design rules, minimum wire width is reduced from  $4\mu m$  to  $2\mu m$ with a  $\lambda$  of 1.0 $\mu m$ . This allows more precise control of threshold detector values and column output generator current levels.

### 2. Improved Logic Values and Switching Thresholds

In order to reduce power requirements for this design and improve noise margin performance, the logic value thresholds and the ideal current values produced by the stepup and step-down generators were redesigned as follows:

|                 | Ori                    | ginal HAMLE      | ET Design Values:    |                      |  |

|-----------------|------------------------|------------------|----------------------|----------------------|--|

| Logic<br>Values | Step Down<br>Generator | Ideal<br>Current | Current<br>Generator | Step Up<br>Generator |  |

| 0               | 0μA                    | 0µА              | *                    | 10µA                 |  |

| 1               | 20µA                   | 50µA             | 58µA                 | 60µА                 |  |

| 2               | 80µA                   | 100µA            | 100µA                | 110µA                |  |

| 3               | 130µA                  | 150µA            | 136µА                | not defined          |  |

|                 |                        |                  |                      |                      |  |

|                 |                        | New Desig        | gn Values:           |                      |  |

| 0               | 0μΑ                    | 0μΑ              | *                    | 20µA                 |  |

| 1               | 20µA                   | 40µA             | 40µA                 | 60µA                 |  |

| 2               | 60µА                   | 80µA             | 80µA                 | 100µA                |  |

| 3               | 100µA                  | 120µA            | 120µA                | 150µA                |  |

TABLE 3.1: New Logic and Threshold Current Values

A substantial power savings was also realized by reducing the current output from the step up and step down cells. The column output generators require much less current for switching purposes than in the original HAMLET design. Table 3.2 summarizes the redesign of the step up/down generator output current levels.

| Output Currents From Step Up/Down Generators: |                      |                        |  |  |  |

|-----------------------------------------------|----------------------|------------------------|--|--|--|

|                                               | Step Up<br>Generator | Step Down<br>Generator |  |  |  |

| Original Cells                                | 180µA                | 240µA                  |  |  |  |

| New Cell Design                               | 60µA                 | 70µA                   |  |  |  |

# TABLE 3.2: New Step Up and Step Down Generator Output Current Design

### 3. Simulation of New Cells

The individual circuits were implemented using MAGIC and then extracted to SPICE for simulation and analysis. Because of the nature of multi-valued logic, the normal definition of noise margin does not apply. For this circuit, the noise margin can be defined as the difference between the output logic level and the input switching thresholds of the next gate. The optimum noise margin can be achieved only by centering the output logic value between its associated switching thresholds. These nominal current values have been achieved within 2nA.

The timing delays and power consumption of the various components are detailed below.

|                          | Step Up<br>Generator | Step Down<br>Generator | Column<br>Output<br>Generator |

|--------------------------|----------------------|------------------------|-------------------------------|

| T <sub>r</sub> (ns)      | 4.19                 | 1.43                   | 1.23                          |

| T <sub>r</sub> (ns)      | 2.04                 | 3.12                   | 1.51                          |

| T <sub>PLH</sub> (ns)    | 11.48                | 4.29                   | 2.16                          |

| T <sub>PHL</sub> (ns)    | 2.74                 | 9.61                   | 5.69                          |

| P <sub>STATIC</sub> (mW) | 1.78(H)/<br>0.0L     | 1.07                   | 0.42(H)/<br>0.81(L)           |

TABLE 3.3: Timing and Power Simulation of Cells

|                            | Step Up<br>Generator | Step Down<br>Generator | Column<br>Output<br>Generator |

|----------------------------|----------------------|------------------------|-------------------------------|

| P <sub>LH(peak)</sub> (mW) | 1.78                 | 1.34                   | 0.87                          |

| P <sub>HL(peak)</sub> (mW) | 1.78                 | 2.25                   | 1.60                          |

TABLE 3.3: Timing and Power Simulation of Cells

The power dissipation for this circuit appears to be fairly high. This is expected because the proper operation of this type of multi-valued logic circuit requires continuous current flow at different levels to achieve the desired results. Unlike conventional CMOS logic, the static power dissipation is much greater than the transistor leakage current.

#### 4. Simulation of a Combined Minterm Using the New Cells

The components were combined to yield a fairly typical minterm for analysis. The minterm chosen was:

This term was implemented in MAGIC and extracted to SPICE for simulation and analysis. The results are compiled in the following table:

| T <sub>r</sub> (ns)        | 4.19         |

|----------------------------|--------------|

| T <sub>r</sub> (ns)        | 2.04         |

| T <sub>PLH</sub> (ns)      | 11.48        |

| T <sub>PHL</sub> (ns)      | 2.74         |

| P <sub>STATIC</sub> (mW)   | 1.78(H)/0.0L |

| P <sub>LH(peak)</sub> (mW) | 1.78         |

| P <sub>HL(peak)</sub> (mW) | 1.78         |

TABLE 3.4: Term 3 X(2,2) Y(3,3) C(2,2)

As expected, the rise and fall times are fairly close and reflect the contribution of the column output generator. The propagation delays are a result of the series connection of the step generators and the column output generator. In this configuration, there are a total of 4 CMOS inverter stages that a signal must propagate through prior to the generator output transitor. The power results are expected and reflect the affect of choosing a current-mode CMOS implementation. The static power dissipation is fairly significant, while the dynamic power is of much lower value. Unfortunately, these will add to the static figure during loxic transitions and result in a substantial power transitien. (Appendices D-G)

### D. CIRCUIT LAYOUT

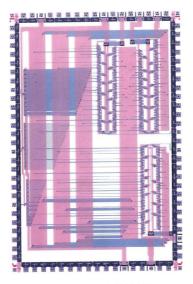

The circuit was laid out using MAGIC for a MOSIS 2.0 micron process, using n-well process data from Orbit fabrication facility.

### 1. Basic floor plan

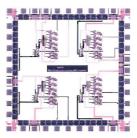

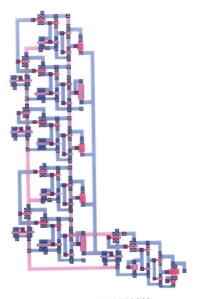

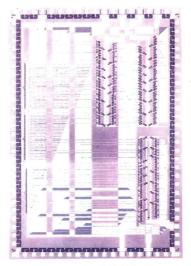

The basic floor plan of the chip consists of 2 "towers" wired together at the output to realize the truncated sum function, a single tower for the carry out function, and a set of current mirrors to replicate the inputs that are required for each term. The cell has 3 input and 2 output pads, as well as separate power and ground inputs for the sum function towers (2), carry function, and current mirror cell, respectively. The sum output is composed of 47 minterms, while the carry is composed of 17 minterms. The final layout for this device is shown in figure 3.2.

Figure 3.2: Final Layout of Design

#### 2. Input Current Mirror Design and Layout

Each of these terms, in general, requires all three input current signals. A current mirror was designed to provide for these input requirements. We centered the current replicator design at 80uA because of the nonlinear nature of the current mirror circuit with a varying current reference. This results in less than a 10uA deviation from the desired current at the other logic levels.

Figure 3.3: Current Mirror Response

### 3. VDD and Ground Rail Considerations

Power consumption was also a major design consideration, as discussed earlier. Care must be exercised to ensure that the circuit will not fail due to electromigration problems associated with excess current within the interconnect network. In addition, to separate power and ground rails for each tower and the current mirror unit, metal 2 was used which has a nominal rating of 1 mA/µm of width. As can be observed in the power plot of Figure 3.4, at no point does the current exceed 30mA on any rail. These measurements were recorded during the functional test (Figure 3.5) These values are relatively high, but do not pose a threat to the circuit.

Figure 3.4: Current Measurements at VDD and Ground Rails

Finally, there are transients in the output due to the nature of the circuit. The various minterms turn "on" and "off" at different times depending on the current levels at their inputs. This results in transients while the circuit is stabilizing between input changes. Provided the transients do not exceed power ratings (as previously shown) and the output is sampled once it has stabilized, these hazards will not affect the circuit operation. The time delay for transients to subside can be included in the delay of the adder.

## 4. Simulation of Completed Chip Design

A series of square current waveforms were applied at each input in order to simulate all combinations possible. The SPICE model produced output showing the correct counting sequence at the output nodes for all input combinations.

Power and transient models obtained from SPICE are included in the results chapter for comparison with measured and observed values.

### IV. TESTING AND EVALUATION OF MULTI-VALUED LOGIC (MOD4) CARRY SAVE ADDER

This section summarizes the performance characteristics and functionality of the multiple-valued logic (modulo four) carry save adder designed and implemented in current mode CMOS. A total of 15 devices were returned from fabrication, 12 of which were mounted in appropriate packages. Four devices from the lot were completely tested (dev1 - dev4). In order to readily test these devices, a custom testbench was designed and constructed.

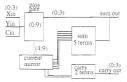

### A. DESIGN OF MODULO FOUR TESTBENCH

### 1. Binary-to-Ideal Current Source Conversion

It is desirable to have a method for converting binary digits to current levels as required by the inputs to the full adder. Conversely, a convenient method for measuring the sum and carry out is also necessary. Each of the three inputs, X, Y, and Carry in are driven by the following circuit:

Figure 4.1: Testbench Input Circuitry

The D/A converter stage is controlled by two dip switches which select between Vref and open-circuit. The use of dip switches is dependent on the ability of the op-amp to produce a virtual ground at the inverting terminal, and the input resistance of the op-amp being significantly greater than R (50kCD). The output of the D/A converter is connected to the Vin node of a Howland voltage-controlled current source.[23] The Howland circuit was chosen because the output current is nearly ideal over a wide range of loading. This is required because the current-sensing transistors in the threshold detectors will have a variable resistance as they switch in and out of saturation.

#### 2. Current Decoding at Outputs

The output circuitry has three stages, a current-controlled voltage source (ICVS), a series of voltage comparators, and a digital logic LED display circuit. The output circuit is specifically designed to detect the proper switching thresholds designed into the modulo four adder. The output circuitry is shown in figure 4.2.

Figure 4.2: Testbench Output Circuitry

It should be noted that this testbench is useful for functional testing and transient analysis. For transient testing, the dip switch input is changed to a clocked voltage waveform from a function generator.

### B. SUMMARY OF TEST RESULTS

### 1. Static Power Tests

Static power test results for no-load and full-load conditions were found to be slightly higher than those obtained from SPICE simulation of the layout. As previously mentioned, VDD and Ground inputs were provided for each of the major components of the device. This allowed static power testing of each component individually. The following table shows the power consumption of the major components of the third device in the test lot:

| MVL_adder Device 3                |        |        |  |  |  |

|-----------------------------------|--------|--------|--|--|--|

| Design No Measure<br>Load No Load |        |        |  |  |  |

| Sum (right tower)                 | 2.93mA | 3.12mA |  |  |  |

| Sum (left tower)                  | 2.88mA | 3.02mA |  |  |  |

| Carry out tower                   | 2.95mA | 3.23mA |  |  |  |

| Current mirror                    | 0      | 0.0mA  |  |  |  |

| Pad ring                          | 0      | 0.0mA  |  |  |  |

| TABLE 4.1: | Comp | onent | Static | Power |

|------------|------|-------|--------|-------|

|------------|------|-------|--------|-------|

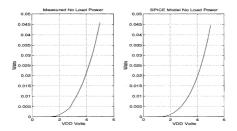

The four test devices were measured under no load conditions (all inputs set to 0uA). As VDD was ramped from 0 to 5.0v, the power supply cuurent was recorded. The static power consumption was calculated by finding an average current for the four devices and then multiplying by a constant VDD of 5.0v.

$$I_{ave} = (Idev_1 + Idev_2 + Idev_3 + Idev_4)/4 \qquad (4.1)$$

$$P_{ave} = I_{ave} * VDD$$

(4.2)

The resulting average static power under no load conditions is plotted as a function of VDD in Figure 4.5.

The design power consumption model was obtained using SPICE for no-load conditions and VDD was once again ramped from 0 to 5.0v, and the current through the power supply was obtained. The average static power under no-load conditions was calculated as previously described:

Figure 4.3: Measured and SPICE Simulation of No Load Static Power Consumption

For full load testing, all inputs were held high (120µA each) and VDD was set to 5.0v. Once again, the power supply current was recorded for each test device. The measured values are shown compared with the full power simulation obtained from the SPICE model in Table 4.2

|          |                     | ler Fab ID:<br>EFF1 |                | Spice Model<br>(VDD set 5.0v) |  |

|----------|---------------------|---------------------|----------------|-------------------------------|--|

|          | Measured<br>Current | Calculated<br>Power | VDD<br>Current | VDD<br>Power                  |  |

| Device 1 | 70.5mA              | 352.5mW             |                |                               |  |

| Device 2 | 69.3mA              | 346.5mW             | 66mA           | 330mW                         |  |

| Device 3 | 70.2mA              | 351.0mW             |                |                               |  |

| Device 4 | 69.3mA              | 346.5mW             | 7              |                               |  |

TABLE 4.2: Full Power Measurements

The highest current level at the outputs occurs when the sum output transitions from a logic 2 to a logic 3, and vice versa. The measured value was determined by using a ramped current input from 0 to 150µA and observing the transitions at the sum terminal. A transient current spike of 195µA was recorded. This effect was seen for transitions in both directions. This transient result correlates with the SPICE model which showed similar transients of 195µA for these transitions(Appendix L). This result translates into a peak power rating for the device of 353.63mW, assuming all three inputs experience a simultaneous transition from logic 2 to logic 3.

### 2. Functional Testing

Steady-state functional values for output currents were within 1.5% of design, and most were found to be significantly less than 1.0%. Exhaustive functional logic testing was conducted (64 input combinations), and no deviation from predicted output values was observed in steady-state. The following table is a sample set from the input test on dev1. Shown are the design output values from the SPICE model vs. actual measured currents observed no the testbench.

|                 | Sum (          | Dutput | Carry | Output   |

|-----------------|----------------|--------|-------|----------|

| [Xin, Yin, Cin] | design<br>(mA) |        |       | measured |

| [1,1,0]         | 80             | 82.2   | 0     | 0        |

| [2,1,0]         | 120            | 119.3  | 0     | 0        |

| [1,3,0]         | 0              | 0      | 40    | 41.3     |

| [2,0,1]         | 120            | 119.7  | 0     | 0        |

| [2,1,2]         | 40             | 41.2   | 40    | 40.3     |

| [3,0,1]         | 0              | 0      | 40    | 40.9     |

| [3,2,1]         | 80             | 80.9   | 40    | 40.0     |

| [0,3,2]         | 40             | 40.3   | 40    | 40.3     |

| [3,3,2]         | 0              | 0      | 80    | 79.2     |

| [0,2,2]         | 0              | 0      | 40    | 40.2     |

TABLE 4.3: Functional Test for Device 1

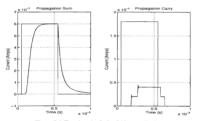

#### 3. Transient Analysis