# Vectored Interrupt Programming

Copyright (c) 2023 - 2014 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using LibreOffice.

### Based on

ARM System-on-Chip Architecture, 2<sup>nd</sup> ed, Steve Furber

Introduction to ARM Cortex-M Microcontrollers – Embedded Systems, Jonathan W. Valvano

Digital Design and Computer Architecture, D. M. Harris and S. L. Harris

ARM assembler in Raspberry Pi Roger Ferrer Ibáñez

https://thinkingeek.com/arm-assembler-raspberry-pi/

### Standard Interrupt Controller

The **standard** interrupt controller <u>sends</u> an interrupt signal to the <u>processor</u> core when an <u>external</u> <u>device</u> requests servicing.

It can be programmed to <u>ignore</u> or <u>mask</u> an <u>individual</u> device or <u>set</u> of devices.

The interrupt handler <u>determines</u>

<u>which device</u> requires servicing

by <u>reading</u> a <u>device</u> bitmap register

in the interrupt controller.

standard interrupt controller

programmable <u>mask</u>

interrupt source by <u>reading</u> a device register

http://s3-us-west-2.amazonaws.com/valpont/uploads/20160326012043/Exception\_handling.pdf

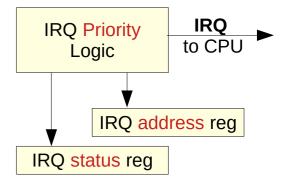

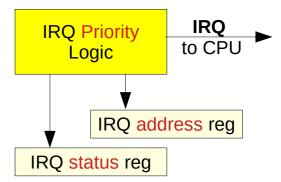

### Vectored Interrupt Controller

The VIC is more powerful than the standard interrupt controller

- prioritizes interrupts

- simplifies the determination of interrupt source (of which device caused the interrupt)

- a priority is associated with a handler address for each interrupt request

- the VIC <u>asserts</u> an interrupt signal to the core

VIC = IVT + Priority

**Vectored Interrupt Controller (VIC)** Interrupt Vector Table (IVT)

priority - handler address

preemptive interrupt handling only when the priority of a new interrupt is higher than that of the currently executing interrupt handle

http://s3-us-west-2.amazonaws.com/valpont/uploads/20160326012043/Exception handling.pdf

### Multiple ISR handlers

Usually in the old generation controllers, there is <u>only one</u> ISR that handles <u>multiple</u> interrupt sources.

the ISR <u>checks</u> the particular register to find the interrupt source

- who is <u>interrupting</u> the processor.

large interrupt latency

to <u>reduce</u> interrupt latency,

ARM has come up with an idea of

a vector interrupt controller (**VIC**)

where each interrupt can have <u>separate</u> ISR's

each ISR <u>address</u> will be stored in the **Interrupt Vector Table**.

**Default ISR**

ISR determines the interrupt source

One ISR – multiple interrupt sources

Large latency

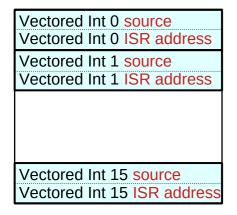

#### Separate ISR's, IVT

IRQ source 1 ---- ISR 1 address IRQ source 2 ---- ISR 2 address IRQ source 3 ---- ISR 3 address

If IRQ source i, then jump to ISRi

https://embetronicx.com/tutorials/microcontrollers/stm32/vectored-interrupt-controller-nested-vectored-interrupt-controller-vic-nvic/

6

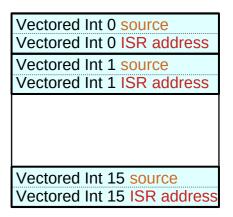

### IRQ sources and ISR addresses

The VIC provides a software interface to the interrupt system.

In a standard interrupt controller,

software must determine

the source that is requesting service

where its ISR is loaded.

<u>SW</u> (ISR) determines the interrupt source

Jump address must be loaded

In a vectored interrupt controller,

hardware supplies

the starting address,

or vector address, of the ISR

corresponding to the interrupt source

that has the highest priority

**HW** determines the interrupt source

A table lookup of <u>IVT</u> provides the jump address (the specific ISR)

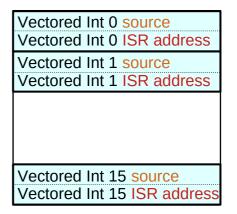

### Interrupt Vector Table

Interrupt vector table (IVT)

VIC = IVT + Priority

contains the address of the IRQ handlers of every interrupt.

Old VIC = IVT only, no priority

directs the PC where to go, when an interrupt occurs.

refers <u>early generation</u> of VIC, because they just point the address when an interrupt occurs.

priority was not fully applied

https://www.quora.com/What-is-the-difference-between-ARMs-nested-vectored-interrupt-controller-and-an-interrupt-vector-table-which-seems-to-be-used-by-the-other-process.

# VIC interrupt handling types (1)

#### the VIC interrupt handling types

- make the core jump <u>directly</u> to the handler address for the device (Vectored IRQ)

- either call the standard interrupt exception handler, which can <u>load</u> the handler address for the device from the VIC (Non-Vectored IRQ)

*VIC* = *IVT* + *Priority*

Vectored IRQ

unique ISR

jump to the address

Non-vectored IRQ default ISR load the address

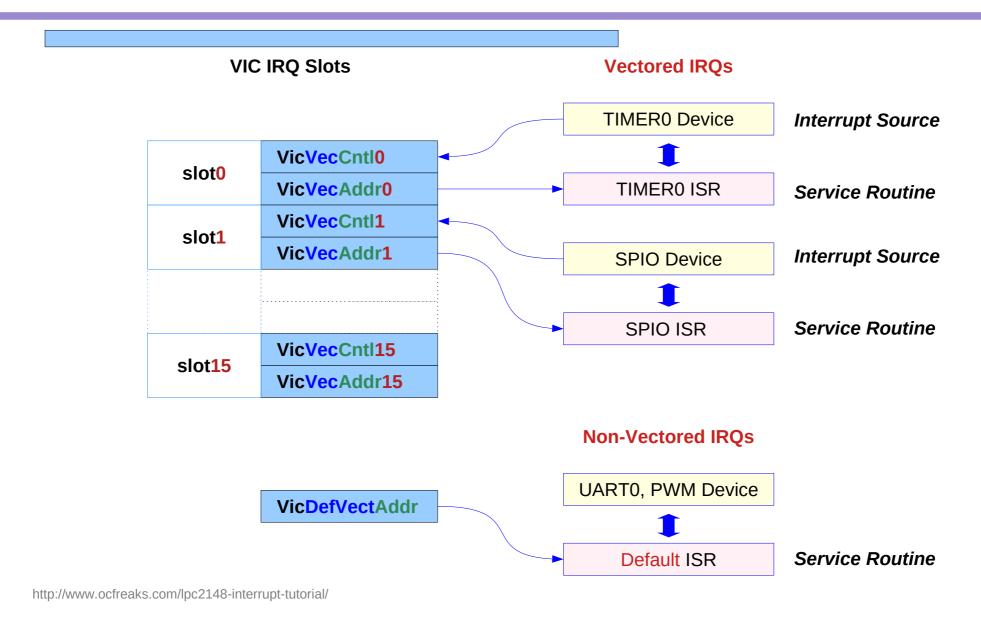

#### in lpc214x

VICVectAddr : holds the address of the associated ISR i.e the one which is <u>currently active</u>.

VICDefVectAddr : stores the <u>address</u> of the "<u>default</u>/common" ISR for a **Non-Vectored IRQ** occurs

$http://s3-us-west-2.amazonaws.com/valpont/uploads/20160326012043/Exception\_handling.pdf$

# VIC interrupt handling types (2)

VIRQ (Vectored IRQ) has dedicated IRQ <u>service routine</u> for *each* Vectored interrupt <u>source</u>

NVIRQ (Non-Vectored IRQ) has the same IRQ <u>service routine</u> for *all* Non-Vectored Interrupts. VIC = IVT + Priority

Vectored IRQ dedicated ISR for each IRQ source

Non-vectored IRQ default ISR for all IRQ sources

in lpc214x

VICVectAddr

i.e the one which is <u>currently active</u>.

VICDefVectAddr

i.e the one which is <u>currently active</u>.

i.e the one which is <u>currently active</u>.

i.e the one which is <u>currently active</u>.

http://www.ocfreaks.com/lpc2148-interrupt-tutorial/

# VIC interrupt handling types (3)

Vectored means that

the CPU is <u>aware</u> of the address of the ISR

when the interrupt occurs

Non-Vectored means that

CPU doesn't know the address of the ISR nor the source of the IRQ when the interrupt occurs it needs to be supplied with the ISR address.

For the Vectored Interrupt Controller, the system internally maintains a table IVT (Interrupt Vector Table)

> which contains the information about Interrupts sources and their corresponding ISR address.

http://www.ocfreaks.com/lpc2148-interrupt-tutorial/

*VIC* = *IVT* + *Priority*

Vectored IRQ

ISR address is known

jump to the address

Non-vectored IRQ

IRQ address <u>not</u> known

<u>load</u> the address

IRQ source 1 ISR 1 address IRQ source 2 ISR 2 address IRQ source 3 ISR 3 address

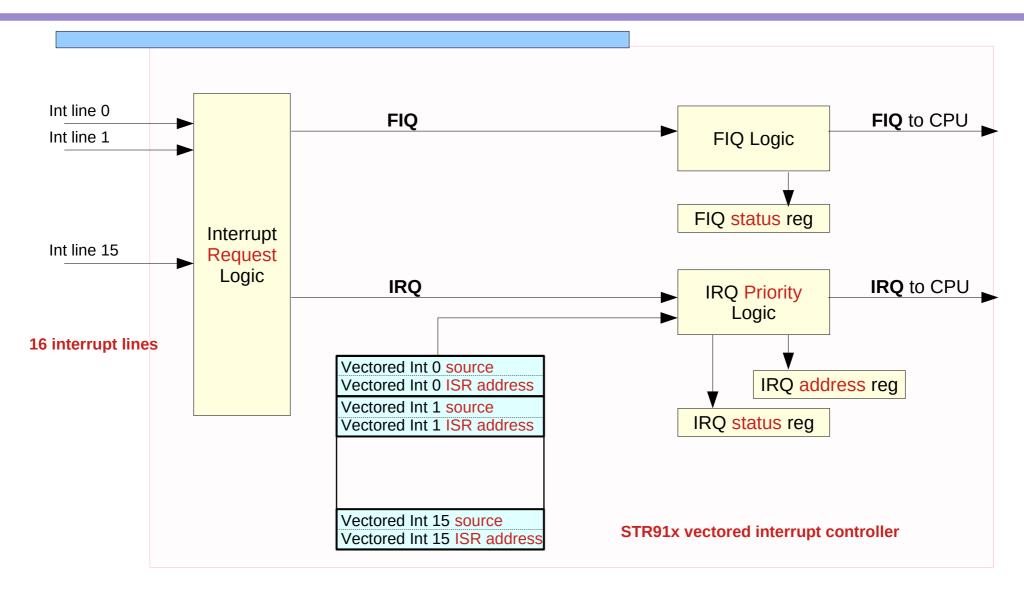

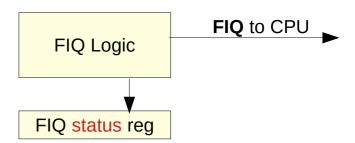

### **ARM FIQ**

In an ARM system, two levels of interrupts are available:

#### **Fast Interrupt reQuest (FIQ)**

- For <u>fast</u>, <u>low latency</u> interrupt handling.

#### **Interrupt ReQuest (IRQ)**

- For more general interrupts.

- a <u>single</u> FIQ source system for a low-latency interrupt

Single FIQ source system

- the ISR is executed <u>directly</u>

<u>without</u> <u>determining</u> the <u>source</u> of the interrupt

- this reduces the interrupt latency

- the banked registers of FIQ mode can be used more efficiently, without incurring a context save overhead

Register bank

### 3 categories of IRQ's

The ARM Vectored Interrupt Controller (VIC) takes 32 interrupt request inputs and programmably assigns them into 3 categories,

- FIQ

- vectored IRQ

- non-vectored IRQ.

### **Nested Vectored Interrupt Controller**

A <u>Nested</u> Vectored Interrupt Controller (NVIC) is used to manage the interrupts from <u>multiple</u> interrupt sources.

NVIC is closely integrated with the processor core to achieve low-latency interrupt processing and efficient processing of late arriving interrupts.

# NVIC vs. VIC (1)

every interrupt with certain priority levels

each interrupt is <u>serviced</u> / <u>processed</u> with its own <u>priority</u> level.

Servicing / processing the interrupt means the processing of the part of codes inside the IRQ handler of the respective interrupt.

#### Interrupt handling of

- Nested Vectored Interrupt Controller (NVIC)

- Vectored Interrupt Controller (VIC)

- Interrupt Vector Table (IVT)

https://www.quora.com/What-is-the-difference-between-ARMs-nested-vectored-interrupt-controller-and-an-interrupt-vector-table-which-seems-to-be-used-by-the-other-process.

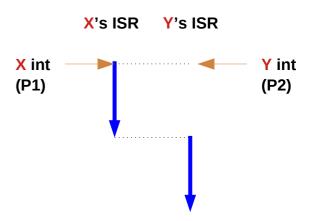

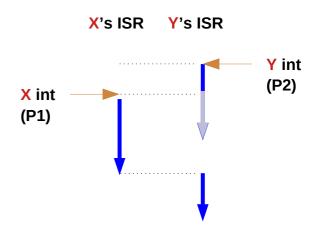

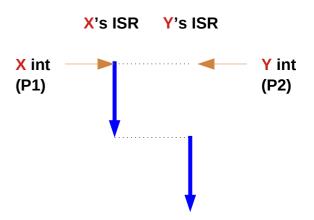

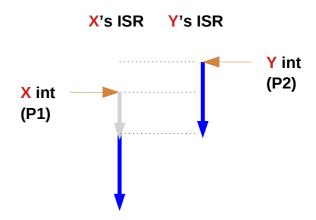

# NVIC vs. VIC (2)

#### Example assumption:

```

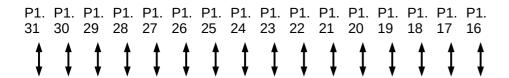

Priority 1 (P1) - highest

Priority 2 (P2) - second highest

```

There are two different interrupts X and Y with priority levels P1 and P2 respectively.

- interrupts X and Y occur at the same time.

- interrupt Y (P2) has occured first and while servicing interrupt Y (P2) interrupt X (P1) occurs

# Nested VIC handling (1)

• If interrupts X and Y occur at the same time.

first X (P1) is <u>processed</u>, Y (P2) is <u>put on hold</u>.

After processing X, Y is processed.

# Nested VIC handling (2)

If interrupt Y (P2) has occured first and interrupt X (P1) occurs while servicing interrupt Y (P2)

Then, the controller <u>puts</u>

the <u>interrupt Y's IRQ</u> handler <u>on hold</u>

and <u>processes</u>

the <u>interrupt X's IRQ</u> handler <u>completely</u>

and then <u>resumes</u>

the <u>interrupt Y's IRQ</u> handler

So, it <u>processes</u> interrupt by <u>nesting</u> them within each other.

# VIC handling (1)

• If interrupts X and Y occur at the same time.

first X (P1) is <u>processed</u>, Y (P2) is <u>put on hold</u>.

After processing X, Y is processed.

# VIC handling (2)

If interrupt Y (P2) has occured first and interrupt X (P1) occurs while servicing interrupt Y (P2)

Then, the controller <u>processes</u> the <u>interrupt Y's IRQ</u> handler <u>completely</u>

and then the <u>processes</u> the interrupt X's IRQ handler

https://www.guora.com/What-is-the-difference-between-ARMs-nested-vectored-interrupt-controller-and-an-interrupt-vector-table-which-seems-to-be-used-by-the-other-processing and the controller and the cont

# NVIC features in cortex M (1)

- external interrupts (1 ~ 240)

- bits of priority (3 ~ 8)

- a dynamic re-prioritization of interrupts.

- priority grouping enables the <u>selection</u> of preempting interrupt levels

non-preempting interrupt levels.

- support for tail-chaining and late arrival of interrupts.

This enables <u>back-to-back</u> interrupt processing <u>without</u> the overhead of state <u>saving</u> and <u>restoration</u> between interrupts.

# NVIC features in cortex M (2)

processor state <u>automatically</u>

```

saved on interrupt entry,restored on interrupt exit,with no instruction overhead.

```

- Optional Wake-up Interrupt Controller (WIC),

providing ultra-low-power sleep mode support.

- Vector table can be located in either RAM or flash.

All interrupts including the core exceptions are <u>managed</u> by the NVIC.

The NVIC maintains knowledge of the <u>stacked</u>, or <u>nested</u>, interrupts to enable tail-chaining of interrupts.

# Nest VIC (1)

- In a microcontroller, such as those at the heart of industrial motion controllers, interrupts serve as a way to immediately divert the CPU from its current task to another, more important task.

- An interrupt can be triggered internally from the microcontroller (MCU) or externally, by a peripheral.

- the interrupt alerts the CPU to an occurrence such as a time-based event

- · a specified amount of time has elapsed or

- a specific time is reached, for example,

- a change of state, or

- the start or end of a process.

### Nest VIC (2-1)

- Another method of monitoring a timed event or change of state is referred to as "polling."

- With polling, the status of a timer or state change is periodically checked.

- The downsides of polling are the risk of excessive latency (delay) between the actual change and its detection, the possibility of missing a change altogether, and the increased processing time and power it requires.

•

•

•

# Nest VIC (2-2)

- When an interrupt occurs, an interrupt signal is generated, which causes the CPU to stop its current operation, save its current state, and begin the processing program

- referred to as an interrupt service routine (ISR) or interrupt handler

- associated with the interrupt.

•

- When the interrupt processing is complete,

- the CPU restores its previous state and resumes where it left off.

# Nest VIC (3)

- Nested vector interrupt control (NVIC) is a method of prioritizing interrupts, improving the MCU's performance and reducing interrupt latency.

- NVIC also provides implementation schemes for handling interrupts that occur when other interrupts are being executed or when the CPU is in the process of restoring its previous state and resuming its suspended process.

•

- The term "nested" refers to the fact that in NVIC, a number of interrupts can be defined (up to several hundred in some processors), and each interrupt is assigned a priority, with "0" being the highest priority.

- In addition, the most critical interrupt can be made non-maskable, meaning it cannot be disabled (masked).

# Nest VIC (4)

- One function of NVIC is to ensure that higher priority interrupts are completed before lower-priority interrupts, even if the lower-priority interrupt is triggered first.

- For example, if a lower-priority interrupt is being registered\* or executed and a higher-priority interrupt occurs, the CPU will stop the lower-priority interrupt and process the higher-priority one first.

•

\* A register is a special, dedicated memory circuit within the CPU that can be written and read much more quickly than regular memory.

•

The register is used to store information such as calculation results,

CPU execution states, or other critical program information.

# Nest VIC (5)

Similarly, a handling scheme referred to as "tail-chaining" specifies that if an interrupt is pending while the ISR for another, higher-priority another interrupt completes, the processor will immediately begin the ISR for the next interrupt, without restoring its previous state.

•

• The term "vector" in nested vector interrupt control refers to the way in which the CPU finds the program, or ISR, to be executed when an interrupt occurs.

•

•

# Nest VIC (6)

- Nested vector interrupt control uses a vector table that contains the addresses of the ISRs for each interrupt.

- When an interrupt is triggered, the processor gets the address from the vector table.

•

- The prioritization and handling schemes of nested vector interrupt control reduce the latency and overhead that interrupts typically introduce and

- ensure low power consumption, even with high interrupt loading on the controller.

•

$https://www.st.com/resource/en/application\_note/an 2593-str91x-interrupt-management-stmicroelectronics.pdf$

$https://www.st.com/resource/en/application\_note/an 2593-str91x-interrupt-management-stmicroelectronics.pdf$

| Interrupt           | Configured Priority |

|---------------------|---------------------|

| VIC0 FIQ / VIC1 FIQ | NA                  |

| VIC0 IRQ            | 0                   |

| VIC0 IRQ            | 1                   |

|                     |                     |

| VIC0 IRQ            | 15                  |

| VIC1 IRQ            | 0                   |

| VIC1 IRQ            | 1                   |

|                     |                     |

| VIC1 IRQ            | 15                  |

Highest priority

Lowest priority

http://www.ocfreaks.com/lpc2148-interrupt-tutorial/

- for FIQ there are <u>no</u> priority levels.

- when an enabled FIQ interrupt occurs, the VIC <u>signals</u> it *directly* to the ARM core by asserting the FIQ interrupt line.

- then the ARM core switches to FIQ mode, and goes to address 0x1C

where the FIQ interrupt handler resides

| no   | priority | levels   |           |         |

|------|----------|----------|-----------|---------|

| dire | ectly as | sert FIQ | ) interru | pt line |

FIQ mode

FIQ interrupt handler at 0x1C

| Interrupt           | Configured Priority |

|---------------------|---------------------|

| VIC0 FIQ / VIC1 FIQ | NA                  |

| VIC0 IRQ            | 0                   |

| VIC0 IRQ            | 1                   |

|                     |                     |

| VIC0 IRQ            | 15                  |

| VIC1 IRQ            | 0                   |

| VIC1 IRQ            | 1                   |

|                     |                     |

| VIC1 IRQ            | 15                  |

|                     |                     |

**Highest priority**

Lowest priority

- normally in order to minimize FIQ interrupt latency only one interrupt should be configured as FIQ.

- But it is possible to configure <u>several interrupts</u> as FIQ, and in this case the application software must <u>read</u> the FIQ status registers of both VIC0 and VIC1 in order to <u>determine</u> the FIQ interrupt <u>source</u>

- when the interrupt flag is <u>cleared</u>

in the peripheral(s) that generated the interrupt,

the VIC then will <u>stop</u> <u>asserting</u> the FIQ interrupt to CPU

and the flag will be <u>cleared</u> in the VIC FIQ status register

one interrupt source

multiple interrupt sources read the FIQ status reg determine the FIQ source

interrupt flag in the peripherals interrupt flag in the VIC status reg

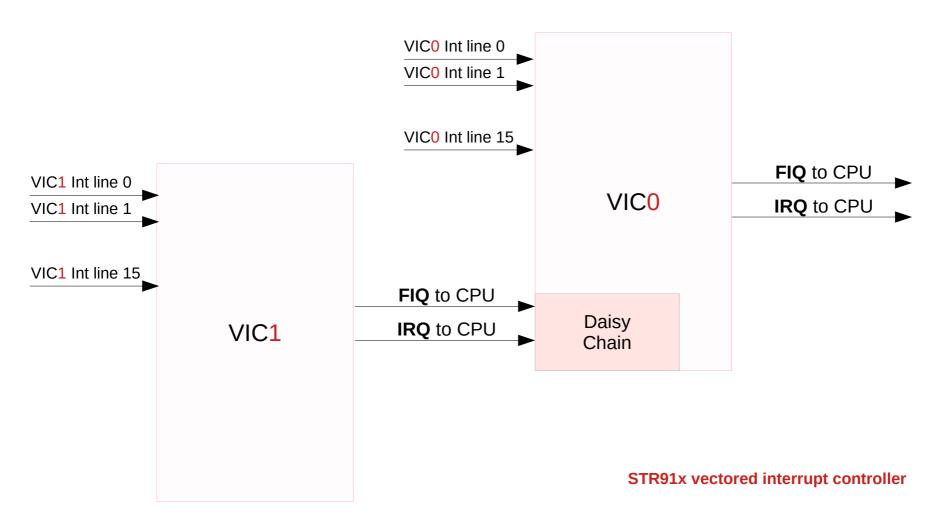

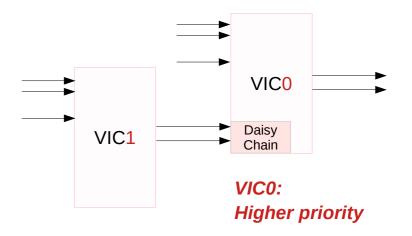

- 1. Vectored IRQ handling

- 2. Simple (Non vectored) IRQ handling

Vectored handling ensures the best interrupt latency

the <u>hardware</u> priority management of the VIC - small latency

the <u>software</u> priority management of the VIC - simple handling

Although a <u>software</u> priority management increases the interrupt latency, it can be useful in special cases where a VIC1 interrupt has to be configured with a higher priority level than a VIC0 interrupt,

this is <u>not possible</u> when using the hardware priority management due to the hardwired priority between VICO and VIC1

| Interrupt           | Configured Priority |  |

|---------------------|---------------------|--|

| VIC0 FIQ / VIC1 FIQ | NA                  |  |

| VIC0 IRQ            | 0                   |  |

| VIC0 IRQ            | 1                   |  |

|                     |                     |  |

| VIC0 IRQ            | 15                  |  |

| VIC1 IRQ            | 0                   |  |

| VIC1 IRQ            | 1                   |  |

|                     |                     |  |

| VIC1 IRQ            | 15                  |  |

When an IRQ interrupt from VIC0 or from VIC1 occurs,

- If the interrupt has a <u>lower priority</u>

than the <u>current interrupt</u> being processed,

then it remains <u>pending</u> in the VIC

<u>until</u> it becomes the <u>higher priority</u> interrupt.

- If the interrupt has the <u>highest priority</u> level then the VICO Vector Address register VICO\_VAR will be <u>loaded</u> with the ISR address and an IRQ interrupt will be <u>signalled</u> to CPU.

Note: The VICO\_VAR will be <u>loaded</u> with the ISR address of the interrupt <u>independently</u> from the the interrupt source either from VIC0 or from VIC1.

- 1. In the IRQ interrupt handler, the software should read the VICO\_VAR (vector address register) to determine the ISR address and jump to it.

- 2. If the interrupt originates <u>from VICO</u>, then reading the VICO\_VAR in step 1 will <u>update</u> the <u>priority logic</u> of VICO: so interrupts with the <u>same</u> or <u>lower priority levels</u> will be <u>masked</u> by the VIC.

But if an interrupt originates <u>from VIC1</u> then you must also read the <u>VIC1\_VAR</u> in order to <u>update</u> the <u>priority logic</u> in VIC1.

including the clearing of the interrupt flags, you must write any value in the VICO\_VAR if the interrupt originates from VICO, or in the VIC1\_VAR if the interrupt is from VIC1, in order to indicate to the VIC that interrupt processing has finished, so it can update the priority logic: then a same or lower level interrupt will be able to interrupt the CPU

# Non-vectored handling of IRQ in STR91x (1)

STR91x

Non-vector handling method of IRQ interrupts does <u>not</u> use the VIC hardware priority management,

so this means you <u>do not have</u> to <u>read</u> or <u>write</u> the VIC0\_VAR or VIC1\_VAR registers to <u>update</u> the hardware priority logic.

This method can be used when there is a need to give <u>higher priority</u> to a VIC1 interrupt over a VIC0 interrupt.

The flow for simple (non vectored) IRQ handling is the following:

- 1. An IRQ interrupt occurs.

- 2. <u>Branch</u> to the interrupt handler.

- 3. Read the VICs IRQ Status registers to determine the source that generated the interrupt, and prioritize the interrupts if there are multiple active interrupt sources.

- 4. <u>Branch</u> to the *corresponding* ISR.

- 5. Execute the ISR.

- 6. <u>Clear</u> the interrupt. If a software interrupt generated the request, you must <u>write</u> to the VICx\_SWINTCR register.

- 7. Check the IRQ Status registers of both VICs to ensure that no other interrupt is active. If there is an <u>active request</u>, go to Step 4.

- 8. Return from the interrupt.

## **Vectored Interrupt Controller**

the sequence for the vectored interrupt flow:

- VICVectAddr Register

read to branch to the ISR (interrupt service routine),

which is <u>currently active</u>.

write to <u>clear</u> the respective interrupt

- VICSoftIntClear Register to clear the software interrupt request triggered by VICSoftInt

### the sequence for the vectored interrupt flow:

- When an interrupt occurs, The ARM processor <u>branches</u> to either the **IRQ** or **FIQ interrupt vector**.

- If the interrupt is an IRQ, read the VICVectAddr Register and branch to the ISR (interrupt service routine).

- Stack the workspace so that you can re-enable IRQ interrupts.

- Enable the IRQ interrupts so that a higher priority can be serviced.

- Execute the Interrupt Service Routine (ISR).

- Clear the requesting interrupt in the peripheral, or write to the VICSoftIntClear Register if the request was generated by a software interrupt.

- Disable the interrupts and restore the workspace.

- Write to the VICVectAddr Register.

This clears the respective interrupt in the internal interrupt priority hardware.

- Return from the interrupt. This re-enables the interrupts.

### **Interrupt Source**

| VicVecCntl0  | IRQ source 0  |

|--------------|---------------|

| VicVecCntl1  | IRQ source 1  |

| VicVecCntl2  | IRQ source 2  |

| VicVecCntl3  | IRQ source 3  |

| VicVecCntl4  | IRQ source 4  |

| VicVecCntl5  | IRQ source 5  |

| VicVecCntl6  | IRQ source 6  |

| VicVecCntl7  | IRQ source 7  |

| VicVecCntl8  | IRQ source 8  |

| VicVecCntl9  | IRQ source 9  |

| VicVecCntl10 | IRQ source 10 |

| VicVecCntl11 | IRQ source 11 |

| VicVecCntl12 | IRQ source 12 |

| VicVecCntl13 | IRQ source 13 |

| VicVecCntl14 | IRQ source 14 |

| VicVecCntl15 | IRQ source 15 |

#### **Service Routine**

| VicVecAddr0  | ISR 0 address  |

|--------------|----------------|

| VicVecAddr1  | ISR 1 address  |

| VicVecAddr2  | ISR 2 address  |

| VicVecAddr3  | ISR 3 address  |

| VicVecAddr4  | ISR 4 address  |

| VicVecAddr5  | ISR 5 address  |

| VicVecAddr6  | ISR 6 address  |

| VicVecAddr7  | ISR 7 address  |

| VicVecAddr8  | ISR 8 address  |

| VicVecAddr9  | ISR 9 address  |

| VicVecAddr10 | ISR 10 address |

| VicVecAddr11 | ISR 11 address |

| VicVecAddr12 | ISR 12 address |

| VicVecAddr13 | ISR 13 address |

| VicVecAddr14 | ISR 14 address |

| VicVecAddr15 | ISR 15 address |

Highest priority

**Lowest priority**

the 'magnitude': the interrupt source ID the 'source' of the currently pending IRQ

the 'direction': the corresponding ISR vectored IRQ 'points to' its own unique ISR

Non-Vectored IRQs does <u>not</u> point to a <u>unique</u> ISR instead, default / common ISR

In LPC214x, **VICDefVectAddr** register is used The user must assign the address of the **default ISR**

VicVecCntl0~15

VicVecAddr0~15

VIC (in ARM CPUs & MCUs), as per its design, can take 32 interrupt request inputs but only 16 requests can be assigned to Vectored IRQ interrupts in its LCP2148 ARM7 Implementation.

We are given a set of <u>16</u> vectored IRQ **slots** to which we can assign any of the 22 **requests** that are available in LPC2148.

The slot numbering goes from 0 to 15 with slot no. 0 having highest priority and slot no. 15 having lowest priority.

VicVecCntl0~15 VicVecAddr0~15

| Bit 0 | : WDT   |

|-------|---------|

| Bit 1 | : N/A   |

| Bit 2 | : ARMC0 |

| Bit 3 | : ARMC1 |

| Bit 4 | : TIMR0 |

| Bit 5 | : TIMR1 |

| Bit 6 | : UART0 |

| Bit 7 | : UART1 |

| Bit 8 | : PWM   |

| Bit 9 | : I2C0  |

| Bit10 | : I2C0  |

|       |         |

| Bit11: SPI1/SSP |

|-----------------|

| Bit12 : PLL     |

| Bit13: RTC      |

| Bit14 : EINT0   |

| Bit15 : EINT1   |

| Bit16 : EINT2   |

| Bit17 : EINT3   |

| Bit18 : AD0     |

| Bit19 : I2C1    |

| Bit20 : BOD     |

| Bit21 : AD1     |

| Bit22 : USB     |

|                 |

## **Interrupt Source Encoding**

22 requests

## Vectored meaning (4)

For example if you working with 2 interrupt sources UARTO and TIMERO.

Now if you want to give TIMER0 a higher priority than UART0 then assign TIMER0 interrupt a lower number slot than UART0.

eg. TIMER0 to slot 0 and UART0 to slot 1 or TIMER0 to slot 4 and UART to slot 9 and so on.

The number of the slot doesn't matter as long TIMER0 slot is lower than UART0 slot.

## Vectored meaning (5)

VIC has plenty of registers.

Most of the registers that are used to <u>configure</u> interrupts or <u>read</u> status

each bit corresponds to a particular interrupt source and this correspondence is same for <u>all</u> of these <u>registers</u>.

### For example

bit 0 in these registers corresponds to Watch dog timer interrupt,

bit 4 corresponds to TIMER0 interrupt,

bit 6 corresponds to UARTO interrupt .. and so on.

- VICIntSelect (R/W): used to select an interrupt as IRQ or as FIQ

VICIntEnable (R/W): used to enable interrupts

VICIntEnCIr (R/W): used to disable interrupts

- 4) **VICIRQStatus** (R) : used for reading the current status of the enabled IRQ interrupts.

5) **VICFIQStatus** (R) : used for reading the current status of the enabled FIQ interrupts

6) **VICSoftInt** : used to generate interrupts using software i.e the program itself

- 7) **VICSoftIntClear** : used to clear the interrupt request that was triggered(forced) using VICSoftInt.

- 8) VICVectCntl0 ~15 : used to assign a particular interrupt source to a particular slot.

- 9) **VICVectAddr0 ~15**: store the address of the function that must be called when an interrupt occurs 10) **VICVectAddr**: holds the address of the associated ISR i.e the one which is currently active.

- 11) VICDefVectAddr : stores the address of the "default/common" ISR for a Non-Vectored IRQ occurs

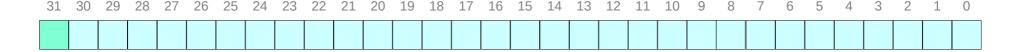

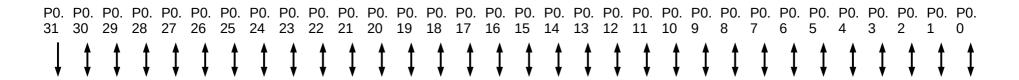

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

E Int source

VICVectCntl0 ~ 15 : used to <u>assign</u> a particular interrupt source to a <u>particular slot</u>.

VICVectCntl0 - the highest priority VICVectCntl15 - the lowest priority

Bit4 ~ Bit0 contain the number of the interrupt request which is assigned to this slot.

Bit5 is used to enable the vectored IRQ slot by writing

| IWA            | . <u>L</u> |

|----------------|------------|

| ARMC0<br>ARMC1 | : 2        |

| ÄRMC1          | : 3        |

| TIMR0          | : 4        |

| TIMR1          | : 5        |

| UART0          | : 6        |

| UART1          | : 7        |

| PWM            | : 8        |

| I2C0           | : 9        |

| I2C0           | : 10       |

|                |            |

| SPI1/SSP | : 11 |

|----------|------|

| PLL      | : 12 |

| RTC      | : 13 |

| EINT0    | : 14 |

| EINT1    | : 15 |

| EINT2    | : 16 |

| EINT3    | : 17 |

| AD0      | : 18 |

| I2C1     | : 19 |

| BOD      | : 20 |

| AD1      | : 21 |

| USB      | : 22 |

## Defining the ISR for Timers

### defining the ISR

explicitly tell the compiler that the function is not a normal function but an ISR

a special keyword called "\_\_irq": a function qualifier.

use this keyword with the function definition

an example of defining an ISR in Keil:

```

__irq void myISR (void) {

....

}

// or equivalently

void myISR (void) __irq

{

....

}

```

## Setup the interrupt for Timers

```

for ARM based microcontrollers like lpc2148.

in order to assign TIMER0 IRQ and ISR to slot X.

Assign TIMER0 Interrupt to Slot number 0

// Enable TIMER0 IRQ

// 5th bit must 1 to enable the slot

// Vectored-IRQ for TIMER0 has been configured

VICIntEnable |= (1<<4);

VICVectCntl0 = (1<<5) | 4;

VICVectAddr0 = (unsigned) myISR;

```

```

Bit 0 : WDT

Bit 1 : N/A

Bit 2 : ARMC0

Bit 3 : ARMC1

Bit 4 : TIMR0

Bit 5 : TIMR1

Bit 6 : UART0

Bit 7 : UART1

Bit 8 : PWM

Bit 9 : I2C0

Bit10 : I2C0

```

- 2) VICIntEnable (R/W): used to enable interrupts

- 8) VICVectCntl0 ~15 : used to assign a particular interrupt source to a particular slot.

- 9) VICVectAddr0 ~15 : store the address of the function that must be called when an interrupt occurs

TOIR, UOIIR Ipc214x

### **IR** (Interrupt Register)

The IR can be written to clear interrupts.

The IR can be read to identify

which of eight possible interrupt sources are pending

### **TOIR** (TIMERO Interrupt Register)

4 bits for the *timer* match interrupts

4 bits for the *timer* capture interrupts

The high bit in the IR signifies that an interrupt is generated

Writing a logic one

to the corresponding IR bit

will reset the interrupt.

Writing a zero has no effect.

**UOIIR (UARTO Interrupt Identification Register)**The UOIIR provides a status code that denotes the priority and source of a pending interrupt.

The interrupts are frozen during an UOIIR access.

If an interrupt occurs during an U0IIR access, the interrupt is recorded for the next U0IIR access

https://www.keil.com/dd/docs/datashts/philips/user\_manual\_lpc214x.pdf

## **TOIR** (TO Timer Interrupt Register )

The **IR** can be <u>read</u> to identify which of 8 possible interrupt sources are pending.

The **IR** can be <u>written</u> to <u>clear</u> interrupts.

| TIMER/ COUNTER0 | T0IR |

|-----------------|------|

| TIMER/ COUNTER1 | T1IR |

The Interrupt Register consists of four bits for the match interrupts and four bits for the capture interrupts.

If an interrupt is <u>generated</u> then the corresponding <u>bit</u> in the <u>IR</u> will be <u>high</u>. Otherwise, the bit will be low.

Writing a logic <u>one</u> to the corresponding IR bit will <u>reset</u> the <u>interrupt</u>.

Writing a <u>zero</u> has no effect

https://www.keil.com/dd/docs/datashts/philips/user\_manual\_lpc214x.pdf

| Bit 0 : MR0 Interru | pt flag for match channel 0         |

|---------------------|-------------------------------------|

| Bit 1 : MR1 Interru | pt flag for match channel 1         |

| Bit 2 : MR2 Interru | pt flag for match channel 2         |

| Bit 3 : MR3 Interru | pt flag for match channel 3         |

| Bit 4 : CR0 Interru | pt flag for capture channel 0 event |

| Bit 5 : CR1 Interru | pt flag for capture channel 1 event |

| Bit 6 : CR2 Interru | pt flag for capture channel 2 event |

| Bit 7 : CR3 Interru | pt flag for capture channel 3 event |

A high bit signifies the interrupt is generated

# **U0IIR** (UARTO Interrupt Identification Register )

lpc214x

Note than UART0's Interrupt Register (**U0IIR**) is a lot different than TIMER0's (**T0IR**).

The first Bit UARTO[0] in U0IIR indicates whether any interrupt is pending or not and its Active LOW!

The next 3 bits UART0[3:1] give the <u>Identification</u> for any of the 4 Interrupts if enabled.

```

Bit0 Interrupt Pending

```

the U0IIR[0] is active low

the pending interrupt can be determined by evaluating U0IIR[3:1]

### Bit3:1 Interrupt Identification

U0IIR[3:1] identifies an interrupt corresponding to the UARTO Rx FIFO All other combinations of U0IIR[3:1] not list are reserved (000, 100, 101, 111)

```

011 1 RLS (Receive Line Status)

010 2a RDA (Receive Data Available)

110 2b CTI (Character Time-Out Indicator

001 2 TLDE (Transmitter Helding Pagister

```

```

001 3 THRE (Transmitter Holding Register Empty)

```

```

__irq void myDefault_ISR(void)

[

U0RegVal = U0IIR; // read the current value

...

if(!(U0RegVal & 0x1)) // active low

{

}

...

VICVectAddr = 0x0; // The ISR has finished!

```

https://www.keil.com/dd/docs/datashts/philips/user\_manual\_lpc214x.pdf

#### **IOPIN** GPIO Port Pin value register.

the current state of the GPIO configured port pins can always be <u>read</u> from this register, regardless of pin direction

#### **IODIR** GPIO Port Direction control register.

This register individually <u>controls</u> the <u>direction</u> of each port pin.

#### **IOSET** GPIO Port Output Set register.

This register <u>controls</u> the state of <u>output pins</u> in conjunction with the <u>IOCLR</u> register.

<u>Writing ones</u> produces <u>highs</u> at the corresponding port pins. <u>Writing zeroes</u> has <u>no effect</u>.

#### **IOCLR** GPIO Port Output Clear register.

This register controls the state of output pins.

Writing ones produces <u>lows</u> at the corresponding port pins and <u>clears</u> the corresponding bits in the <u>IOSET</u> register. Writing zeroes has no effect.

the legacy GPIO referred as "the slow" GPIO the enhanced GPIO referred as "the fast" GPIO.

### IODIR1 for Port 1 1 for output / 0 for input

FIODIR Fast GPIO Port Direction control register. This register individually controls the direction of each port pin.

FIOMASK Fast Mask register for port.

Writes, sets, clears, and reads to port

alter or return only the bits enabled

by zeros in this register.

(done via writes to FIOPIN, FIOSET, and FIOCLR,

and reads of FIOPIN)

FIOPIN Fast Port Pin value register using FIOMASK. The current state of digital port pins can be read from this register, regardless of pin direction or alternate function selection (as long as pins is not configured as an input to ADC). The value read is masked by ANDing with FIOMASK. Writing to this register places corresponding values in all bits enabled by ones in FIOMASK.

**FIOSET** Fast Port Output Set register using **FIOMASK**.

This register controls the state of output pins.

Writing 1s produces highs at the corresponding port pins.

Writing 0s has no effect.

Reading this register returns the current contents of the port output register.

Only bits enabled by ones in FIOMASK can be altered

FIOCLR Fast Port Output Clear register using FIOMASK.

This register controls the state of output pins.

Writing 1s produces lows at the corresponding port pins.

Writing 0s has no effect.

Only bits enabled by ones in **FIOMASK** can be altered.

## GPIO Register (4) examples

```

IOODIR = 0xFFFFFFFF; // Configure all pins on Port 0 as Output

IOOPIN = 0x0;

IOOPIN = \sim IOOPIN;

// Toggle all pins in Port 0

IOOPIN ^= (1<<0);

// xor 2^0

Toggle GPIOO PINO .. PO.0

IOOPIN ^= (1<<1);

// xor 2^1

Toggle GPIO0 PIN1 .. P0.1

IOOPIN ^= (1<<2);

// xor 2^2

Toggle GPIO0 PIN2 .. P0.2

// Toggle 3rd Pin (PIN2) in GPIO0 .. P0.2

IOOPIN ^= (1<<2);

// Toggle 4th Pin (PIN3) in GPIO0 .. P0.3

IOOPIN ^= (1<<3);

```

## VICVectAddr

This must not be confused with the set of 16 VICVecAddr0 ~15 registers.

When an interrupt is Triggered this register holds the address of the associated ISR i.e the one which is currently active.

Writing a value i.e dummy write to this register indicates to the VIC that current Interrupt has finished execution.

In this tutorial the only place we'll use this register .. is at the end of the ISR to signal end of ISR execution.

```

__irq void myDefault_ISR(void)

{

U0RegVal = U0IIR; // read the current value

...

if(!(U0RegVal & 0x1)) // active low

{

}

...

VICVectAddr = 0x0; // The ISR has finished!

```

consider two simple cases for coding an ISR

Use **TIMER0** for generating IRQs

### **Case #1)**

only one 'internal' source of interrupt in **TIMER0** i.e an MR0 match event which raises an IRQ.

### **Case #2)**

multiple 'internal' source of interrupt in **TIMER0** i.e. say a match event for MR0 , MR1 & MR2 which raise an IRQ.

http://www.ocfreaks.com/lpc2148-interrupt-tutorial/

## **TOIR** for TIMER0 T0's Interrupt Register

```

regVal = TOIR;

* * * MRO * * *

TOIR = regval;

```

```

regVal = TOIR;

if( TOIR & MROI_FLAG ) {

*** MRO match ***

} else if ( TOIR & MR1I_FLAG ) {

*** MR1 match ***

} else if ( TOIR & MR2I_FLAG ) {

*** MR2 match ***

}

TOIR = regval;

```

## Only one interrupt source

Since <u>only one</u> source is triggering an <u>interrupt</u> we don't need to <u>identify</u> it

- though its a good practice to explicitly identify it.

```

irq void mylSR(void)

long int regVal;

// read the current value in

// TIMER0's Interrupt Register

regVal = TOIR;

//... MR0 match event has occured

// .. do something here

// write back to clear the interrupt flag

TOIR = regval;

VICVectAddr = 0x0; // The ISR has finished!

```

Even in case #2 things are simple unless we need to identify the 'actual' source of interrupt.

```

#define MR0I FLAG (1<<0)

#define MR1I FLAG (1<<1)

#define MR2I FLAG (1<<2)

irq void mylSR(void)

long int regVal;

// read the current value

// in TIMER0's Interrupt Register

regVal = TOIR;

// write back to clear the interrupt flag

TOIR = regVal;

// Acknowledge that ISR has finished execution

VICVectAddr = 0x0:

http://www.ocfreaks.com/lpc2148-interrupt-tutorial/

```

```

if( TOIR & MROI_FLAG ) {

//do something for MRO match

} else if ( TOIR & MR1I_FLAG ) {

//do something for MR1 match

} else if ( TOIR & MR2I_FLAG ) {

//do something for MR2 match

}

```

## Only one interrupt source

Case #2 actually provides a general method of using Timers as PWM generators!

You can use any one of the match registers as PWM Cycle generator and then use other 3 match registers to generate 3 PWM signals!

Since LPC214x already has PWM generator blocks on chip I don't see any use of Timers being used as PWM generators.

But for MCUs which don't have PWM generator blocks this is very useful.

Both of them deal with IRQs from <u>different blocks</u>: TIMERO and UARTO.

## **Case #3)**

<u>Multiple Vectored IRQs</u> from <u>different</u> devices. Hence <u>Priority</u> comes into picture here.

myTimer0\_ISR()

myUart0\_ISR

### **Case #4)**

Multiple Non-Vectored IRQs from different devices.

myDefault\_ISR

**TOIR** for TIMER0 T0's Interrupt Register

**U0IIR** for UART0 U0's Interrupt ID Register

#### Case #3

TIMERO and UARTO generating interrupts with TIMERO having higher priority.

2 different Vectored ISRs

- one for TIMER0 and one for UART0.

myTimer0\_ISR()

myUart0 ISR

assume only 1 internal source inside both TIMER0 and UART0

```

__irq void myUart0_ISR(void)

{

long int regVal;

regVal = U0IIR;  // read the current value

//Something inside UART0 has raised an IRQ

VICVectAddr = 0x0;

}

```

#### Case #4

TIMERO and UARTO generating interrupts

But here both of them are Non-Vectored and hence will be serviced by a common Non-Vectored ISR.

Hence, here we will need to check the <u>actual</u> source i.e device which triggered the interrupt and proceed accordingly.

This is quite similar to Case #2.

T0's Interrupt Register

U0's(Uart 0) Interrupt Identification Register

```

irq void myDefault_ISR(void)

long int TORegVal, U0RegVal;

T0RegVal = T0IR;

// read the current value

U0RegVal = U0IIR: // read the current value

if( TORegVal )

//do something for TIMER0 Interrupt

TOIR = TORegVal:

// write back to clear

// the interrupt flag

// active low

if(!(U0RegVal & 0x1))

// do something for UARTO Interrupt

// No need to write back to UOIIR

// since reading it clears it

VICVectAddr = 0x0: // The ISR has finished!

```

## Fast Interrupt Request

Well, you can think FIQ as a promoted version of a Vectored IRQ.

To promote or covert a Vectored IRQ to FIQ just make the bit for corresponding IRQ in VICIntSelect register to 1 and it will be become an FIQ.

Also Note that its recommended that you only have one FIQ in your system.

FIQs have low latency than VIRQs and usually used in System Critical Interrupt Handling.

```

/* This file is part of the uVision/ARM development tools

Copyright KEIL ELEKTRONIK GmbH 2002-2005

*/

*/

/* LPC214X.H: Header file for Philips LPC2141/42/44/46/48 */

/***********************************

/* Vectored Interrupt Controller (VIC) */

#define VICIRQStatus

(*((volatile unsigned long *) 0xFFFFF000))

#define VICFIQStatus

(*((volatile unsigned long *) 0xFFFFF004))

#define VICRawIntr

(*((volatile unsigned long *) 0xFFFFF008))

#define VICIntSelect

(*((volatile unsigned long *) 0xFFFFF00C))

#define VICIntEnable

(*((volatile unsigned long *) 0xFFFFF010))

(*((volatile unsigned long *) 0xFFFFF014))

#define VICIntEnClr

#define VICSoftInt

(*((volatile unsigned long *) 0xFFFFF018))

#define VICSoftIntClr

(*((volatile unsigned long *) 0xFFFFF01C))

(*((volatile unsigned long *) 0xFFFFF020))

#define VICProtection

(*((volatile unsigned long *) 0xFFFFF030))

#define VICVectAddr

#define VICDefVectAddr

(*((volatile unsigned long *) 0xFFFFF034))

```

https://www.keil.com/dd/docs/arm/philips/lpc214x.h

```

#define VICVectAddr0 (*((volatile unsigned long *) 0xFFFFF100))

#define VICVectAddr1 (*((volatile unsigned long *) 0xFFFFF104))

... ... (*((volatile unsigned long *) 0xFFFFF13C))

#define VICVectAddr15 (*((volatile unsigned long *) 0xFFFFF13C))

#define VICVectCntl1 (*((volatile unsigned long *) 0xFFFFF204))

... ... ...

#define VICVectCntl15 (*((volatile unsigned long *) 0xFFFFF23C))

```

```

/* Timer 0 */

// Interrupt Register (IR)

#define TOIR

(*((volatile unsigned long *) 0xE0004000))

// Timer Control Register (TCR)

#define TOTCR

(*((volatile unsigned long *) 0xE0004004))

// Timer Counter (TC)

#define TOTC

(*((volatile unsigned long *) 0xE0004008))

// Prescale Register (PR)

#define TOPR

(*((volatile unsigned long *) 0xE000400C))

// Prescale Counter Register (PC)

#define TOPC

(*((volatile unsigned long *) 0xE0004010))

// Match Control Register (MCR)

(*((volatile unsigned long *) 0xE0004014))

#define TOMCR

// Match Register 0 (MR0)

#define TOMRO

(*((volatile unsigned long *) 0xE0004018))

// Match Register 1 (MR1)

#define TOMR1

(*((volatile unsigned long *) 0xE000401C))

// Match Register 2 (MR2)

#define TOMR2

(*((volatile unsigned long *) 0xE0004020))

// Match Register 3 (MR3)

(*((volatile unsigned long *) 0xE0004024))

#define TOMR3

// Capture Control Register (CCR)

(*((volatile unsigned long *) 0xE0004028))

#define TOCCR

// Capture Register 1 (CR1)

(*((volatile unsigned long *) 0xE000402C))

#define TOCRO

(*((volatile unsigned long *) 0xE0004030))

// Capture Register 2 (CR2)

#define TOCR1

// Capture Register 3 (CR3)

(*((volatile unsigned long *) 0xE0004034))

#define TOCR2

// Capture Register 4 (CR4)

#define TOCR3

(*((volatile unsigned long *) 0xE0004038))

// External Match Register (EMR)

#define TOEMR

(*((volatile unsigned long *) 0xE000403C))

// Counter Control Register (CTCR)

#define TOCTCR

(*((volatile unsigned long *) 0xE0004070))

```

```

/* Universal Asynchronous Receiver Transmitter 0 (UART0) */

// Receiver Buffer Register (RBR)

#define U0RBR

(*((volatile unsigned char *) 0xE000C000))

// Transmit Holding Register (THR)

#define U0THR

(*((volatile unsigned char *) 0xE000C000))

// Interrupt Enable Register (IER)

(*((volatile unsigned long *) 0xE000C004))

#define U0IER

// Interrupt Identification Register (IIR)

#define U0IIR

(*((volatile unsigned long *) 0xE000C008))

// FIFO Control Register (FCR)

#define U0FCR

(*((volatile unsigned char *) 0xE000C008))

// Line Control Register (LCR)

#define U0LCR

(*((volatile unsigned char *) 0xE000C00C))

// Modem Control Register (U1MCR)

#define U0MCR

(*((volatile unsigned char *) 0xE000C010))

// Line Status Register (LSR)

#define U0LSR

(*((volatile unsigned char *) 0xE000C014))

// Modem Status Register (U1MSR)

#define U0MSR

(*((volatile unsigned char *) 0xE000C018))

// Scratch Pad Register (SCR)

#define U0SCR

(*((volatile unsigned char *) 0xE000C01C))

// Divisor Latch LSB Register (DLL)

(*((volatile unsigned char *) 0xE000C000))

#define U0DLL

// Divisor Latch MSB Register (DLM)

(*((volatile unsigned char *) 0xE000C004))

#define U0DLM

// Auto-baud Control Register (ACR)

(*((volatile unsigned long *) 0xE000C020))

#define U0ACR

// Fraction Divisor Register (FDR)

(*((volatile unsigned long *) 0xE000C028))

#define U0FDR

// Transmit Enable Register (TER)

#define U0TER

(*((volatile unsigned char *) 0xE000C030))

```

| /* General Purpose Inp | ut/Output (GPIO) */                        |          |

|------------------------|--------------------------------------------|----------|

| #define IOPIN0         | (*((volatile unsigned long *) 0xE0028000)) |          |

| #define IOSET0         | (*((volatile unsigned long *) 0xE0028004)) |          |

| #define IODIR0         | (*((volatile unsigned long *) 0xE0028008)) |          |

| #define IOCLR0         | (*((volatile unsigned long *) 0xE002800C)) |          |

| #define IOPIN1         | (*((volatile unsigned long *) 0xE0028010)) |          |

| #define IOSET1         | (*((volatile unsigned long *) 0xE0028014)) |          |

| #define IODIR1         | (*((volatile unsigned long *) 0xE0028018)) |          |

| #define IOCLR1         | (*((volatile unsigned long *) 0xE002801C)) |          |

| #define IOOPIN         | (*((volatile unsigned long *) 0xE0028000)) | // alias |

| #define IO0SET         | (*((volatile unsigned long *) 0xE0028004)) | // alias |

| #define IOODIR         | (*((volatile unsigned long *) 0xE0028008)) | // alias |

| #define IO0CLR         | (*((volatile unsigned long *) 0xE002800C)) | // alias |

| #define IO1PIN         | (*((volatile unsigned long *) 0xE0028010)) | // alias |

| #define IO1SET         | (*((volatile unsigned long *) 0xE0028014)) | // alias |

| #define IO1DIR         | (*((volatile unsigned long *) 0xE0028018)) | // alias |

| #define IO1CLR         | (*((volatile unsigned long *) 0xE002801C)) | // alias |

| #define FIOODIR        | (*((volatile unsigned long *) 0x3FFFC000)) |          |

| #define FIO0MASK       | (*((volatile unsigned long *) 0x3FFFC010)) |          |

| #define FIOOPIN        | (*((volatile unsigned long *) 0x3FFFC014)) |          |

| #define FIO0SET        | (*((volatile unsigned long *) 0x3FFFC018)) |          |

| #define FIOOCLR        | (*((volatile unsigned long *) 0x3FFFC01C)) |          |

| #define FIO1DIR        | (*((volatile unsigned long *) 0x3FFFC020)) |          |

| #define FIO1MASK       | (*((volatile unsigned long *) 0x3FFFC030)) |          |

| #define FIO1PIN        | (*((volatile unsigned long *) 0x3FFFC034)) |          |

| #define FIO1SET        | (*((volatile unsigned long *) 0x3FFFC038)) |          |

| #define FIO1CLR        | (*((volatile unsigned long *) 0x3FFFC03C)) |          |

### Case 1 Example code (1)

```

(C) Umang Gajera | Power user EX - www.ocfreaks.com 2011-13.

More Embedded tutorials @ www.ocfreaks.com/cat/embedded

Soruce for Interrupt Tutorial Case #1.

License: GPL.

*/

#include < lpc214x.h>

#define MR0I

(1 << 0)

// Interrupt When TC matches MR0

#define MR0R

(1 << 1)

// Reset TC when TC matches MR0

#define DELAY MS

500

// 0.5 Second(s) Delay

#define PRESCALE

// 60000 PCLK clock cycles to increment TC by 1

60000

void initClocks(void);

void initTimer0(void);

irq void TOISR(void);

void initClocks(void);

```

# Case 1 Example code (2)

```

int main(void)

{

initClocks(); //Initialize CPU and Peripheral Clocks @ 60Mhz

initTimer0(); //Initialize Timer0

IOODIR = 0xFFFFFFFF; //Configure all pins on Port 0 as Output

IOOPIN = 0x0;

TOTCR = 0x01; //Enable timer

while(1); //Infinite Idle Loop

//return 0; //normally this wont execute ever :P

}

```

# Case 1 Example code (3)

```

void initTimer0(void)

/*Assuming that PLL0 has been setup with CCLK = 60Mhz and PCLK also = 60Mhz.*/

//----Configure Timer0-----

TOCTCR = 0x0;

TOPR = PRESCALE-1; //(Value in Decimal!) - Increment TOTC at every 60000 clock cycles

//Count begins from zero hence subtracting 1

//60000 clock cycles @60Mhz = 1 mS

TOMRO = DELAY MS-1; //(Value in Decimal!) Zero Indexed Count - hence subtracting 1

TOMCR = MR0I | MR0R; //Set bit0 & bit1 to High which is to: Interrupt & Reset TC on MR0

//----Setup Timer0 Interrupt-----

VICVectAddr4 = (unsigned )TOISR; //Pointer Interrupt Function (ISR)

VICVectCntI4 = 0x20 | 4; //0x20 (i.e bit5 = 1) -> to enable Vectored IRQ slot

//0x4 (bit[4:0]) -> this the source number - here its timer0 which has VIC channel mask # as 4

//You can get the VIC Channel number from Lpc214x manual R2 - pg 58 / sec 5.5

VICIntEnable = 0x10; //Enable timer0 int

TOTCR = 0x02; //Reset Timer

http://www.ocfreaks.com/lpc2148-interrupt-tutorial/

```

### Case 1 Example code (4)

## Case 2 Example code (1)

```

/*

(C) Umang Gajera | Power user EX - www.ocfreaks.com 2011-13.

More Embedded tutorials @ www.ocfreaks.com/cat/embedded

LPC2148 Interrupt Example.

License: GPL.

*/

#include <lpc214x.h>

#define PLOCK

0x00000400

// Interrupt When TC matches MR0

#define MR0L

(1 << 0)

#define MR1I

// Interrupt When TC matches MR1

(1 << 3)

// Interrupt When TC matches MR2

#define MR2L

(1 << 6)

#define MR2R

(1 << 7)

// Reset TC when TC matches MR2

// Interrupt Flag for MR0

#define MR0I FLAG

(1 << 0)

// Interrupt Flag for MR1

#define MR1I FLAG

(1 << 1)

#define MR2I FLAG

(1 << 2)

// Interrupt Flag for MR2

#define MR0 DELAY MS

500

// 0.5 Second(s) Delay

#define MR1 DELAY MS

1000

// 1 Second Delay

#define MR2 DELAY MS

// 1.5 Second(s) Delay

1500

#define PRESCALE

60000

// 60000 PCLK clock cycles to increment TC by 1

```

## Case 2 Example code (2)

```

void delayMS(unsigned int milliseconds);

void initClocks(void);

void initTimer0(void);

irq void myTimer0_ISR(void);

void setupPLL0(void);

void feedSeq(void);

void connectPLL0(void);

int main(void)

initClocks();

// Initialize CPU and Peripheral Clocks @ 60Mhz

initTimer0();

// Initialize Timer0

IOODIR = 0xFFFFFFFF; // Configure all pins on Port 0 as Output

IOOPIN = 0x0;

TOTCR = 0x01;

// Enable timer

while(1);

// Infinite Idle Loop

//return 0;

// normally this wont execute ever

:P

```

### Case 2 Example code (3)

```

void initTimer0(void)

/*Assuming that PLL0 has been setup with CCLK = 60Mhz and PCLK also = 60Mhz.*/

//----Configure Timer0-----

TOCTCR = 0x0;

TOPR = PRESCALE-1;

// 60000 clock cycles @60Mhz = 1 mS

// 0.5sec (Value in Decimal!) Zero Indexed Count - hence subtracting 1

T0MR0 = MR0 DELAY MS-1;

TOMR1 = MR1 DELAY MS-1;

// 1sec

TOMR2 = MR2 DELAY MS-1;

// 1.5secs

TOMCR = MR0I | MR1I | MR2I | MR2R;

// Set the Match control register

//----Setup Timer0 Interrupt-----

// I've just randomly picked-up slot 4

VICVectAddr4 = (unsigned) myTimer0 ISR; // Pointer Interrupt Function (ISR)

VICVectCntl4 = 0x20 | 4;

VICIntEnable = 0x10;

// Enable timer0 int

TOTCR = 0x02;

// Reset Timer

```

### Case 2 Example code (4)

```

irq void myTimer0_ISR(void)

long int regVal;

regVal = TOIR;

// read the current value in T0's Interrupt Register

if(TOIR & MROI FLAG) {

//do something for MR0 match

IOOPIN ^= (1<<0);

// Toggle GPIO0 PIN0 .. P0.0

else if ( TOIR & MR1I_FLAG )

//do something for MR1 match

IOOPIN ^= (1<<1);

// Toggle GPIO0 PIN1 .. P0.1

else if (TOIR & MR2I_FLAG)

I/do something for MR0 match

IOOPIN ^= (1<<2);

// Toggle GPIO0 PIN2 .. P0.2

TOIR = regVal;

// write back to clear the interrupt flag

VICVectAddr = 0x0;

// Acknowledge that ISR has finished execution

```

### Case 2 Example code (5)

6/11/23

### Case 2 Example code (6)

```

//-----PLL Related Functions :-----

// Using PLL settings as shown in : http://www.ocfreaks.com/lpc214x-pll-tutorial-for-cpu-and-peripheral-clock/

void setupPLL0(void)

// Note: Assuming 12Mhz Xtal is connected to LPC2148.

PLL0CON = 0x01;

PLL0CFG = 0x24;

void feedSeq(void)

PLL0FEED = 0xAA;

PLL0FEED = 0x55;

void connectPLL0(void)

while(!( PLL0STAT & PLOCK ));

PLL0CON = 0x03;

```

## Case 3 Example code (1)

```

//-----Setup TIMER0 Interrupt------ // Using Slot 0 for TIMER0

VICVectAddr0 = (unsigned) myTimer0_ISR; // Pointer Interrupt Function (ISR)

VICVectCntl0 = 0x20 | 4;

VICIntEnable |= (1<<4); // Enable timer0 int , 4th bit=1

//------Setup UART0 Interrupt------- // Any Slot with Lower Priority than TIMER0's slot will suffice

VICVectAddr1 = (unsigned) myUart0_ISR; // Pointer Interrupt Function (ISR)

VICVectCntl1 = 0x20 | 6;

VICIntEnable |= (1<<6); //Enable Uart0 interrupt , 6th bit=1

```

## Case 3 Example code (2)

```

irq void myTimer0_ISR(void)

long int regVal;

regVal = TOIR;

// read the current value in T0's Interrupt Register

IOOPIN ^= (1<<2);

// Toggle 3rd Pin in GPIO0 .. P0.2

TOIR = regVal;

// write back to clear the interrupt flag

VICVectAddr = 0x0;

// Acknowledge that ISR has finished execution

irq void myUart0_ISR(void)

long int regVal;

regVal = U0IIR;

// Reading U0IIR also clears it!

//Recieve Data Available Interrupt has occured

// dummy read

regVal = U0RBR;

IOOPIN ^= (1<<3);

// Toggle 4th Pin in GPIO0 .. P0.3

// Acknowledge that ISR has finished execution

VICVectAddr = 0x0;

```

### Case 4 Example code (1)

```

VICDefVectAddr = (unsigned) myDefault_ISR; // Pointer to Default ISR

//-----Enable (Non-Vectored) TIMERO Interrupt-----

VICIntEnable |= (1<<4); // Enable timer0 int , 4th bit=1

//-----Enable (Non-Vectored) UARTO Interrupt------

VICIntEnable |= (1<<6); // Enable UartO interrupt , 6th bit=1

```

# Case 4 Example code (2)

```

irq void myDefault_ISR(void)

long int T0RegVal, U0RegVal;

TORegVal = TOIR;

// read the current value in T0's Interrupt Register

U0RegVal = U0IIR;

if(TOIR)

// Toggle 3rd Pin in GPIO0 .. P0.2

100PIN ^= (1 << 2);

TOIR = TORegVal;

// write back to clear the interrupt flag

if(!(U0RegVal & 0x1))

//Recieve Data Available Interrupt has occured

U0RegVal = U0RBR;

// dummy read

100PIN ^= (1 << 3);

// Toggle 4th Pin in GPIO0 .. P0.3

VICVectAddr = 0x0; // Acknowledge that ISR has finished execution

```

#### References

- [1] http://wiki.osdev.org/ARM\_RaspberryPi\_Tutorial\_C

- [2] http://blog.bobuhiro11.net/2014/01-13-baremetal.html

- [3] http://www.valvers.com/open-software/raspberry-pi/

- [4] https://www.cl.cam.ac.uk/projects/raspberrypi/tutorials/os/downloads.html