# Cache Memory

Young Won Lim 5/23/16 Copyright (c) 2010-2016 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice.

Young Won Lim 5/23/16

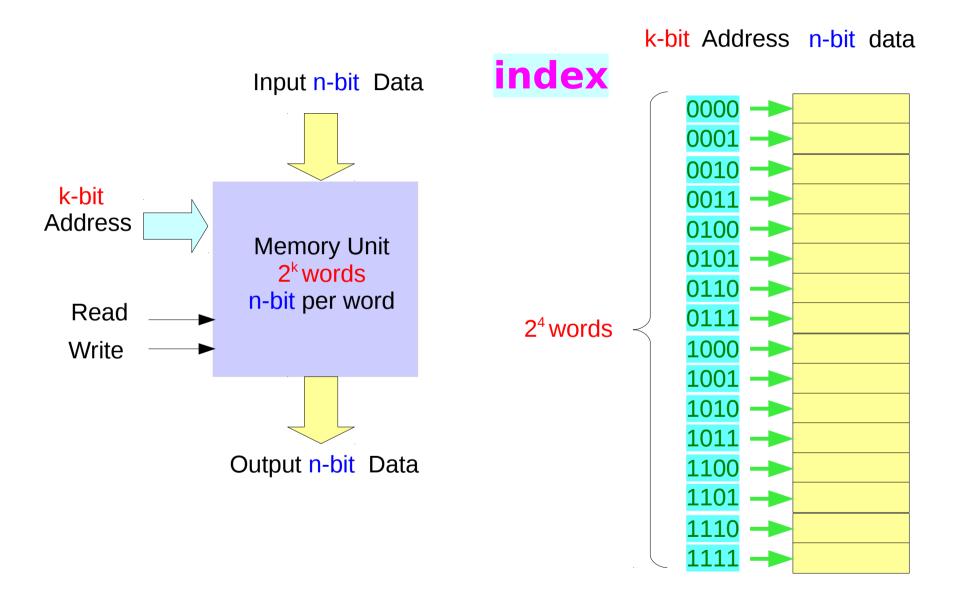

### Address is used as an index to a data array

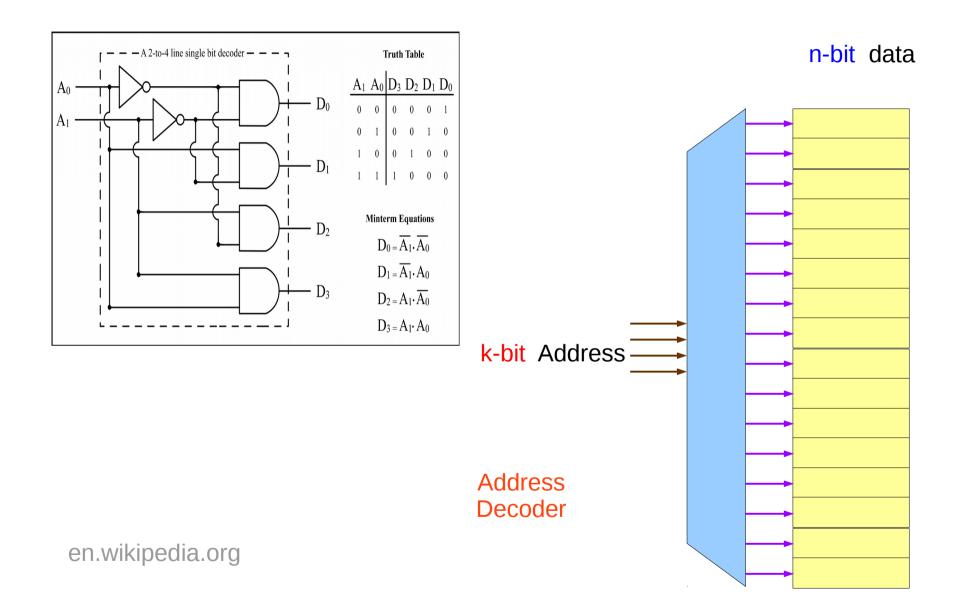

#### MM Address Decoder

4

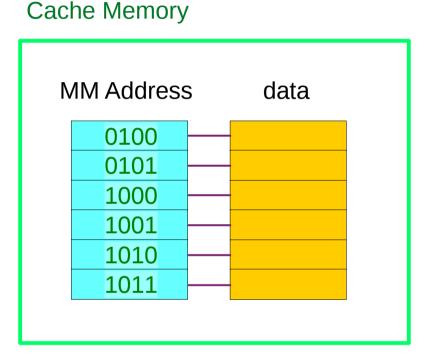

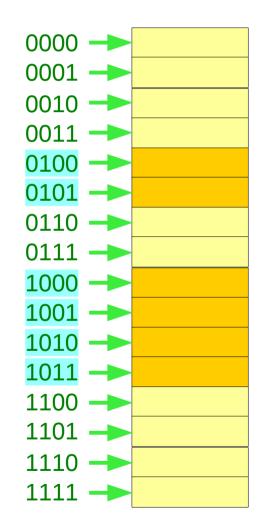

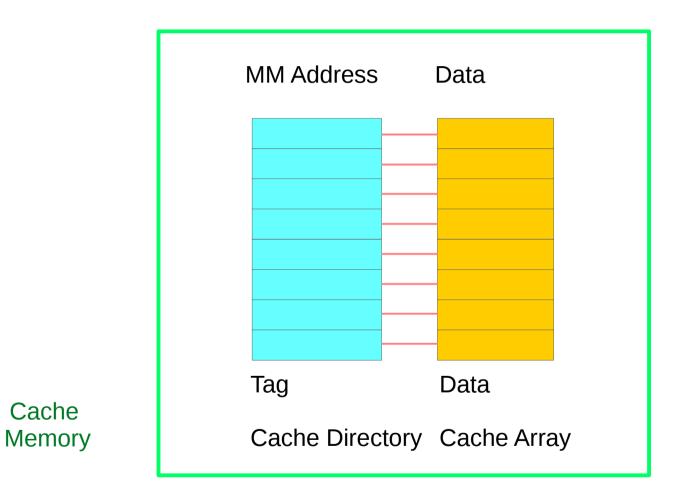

## Cache : Storing a partial copy of MM

#### (MM Address, Data) pair

#### Main Memory

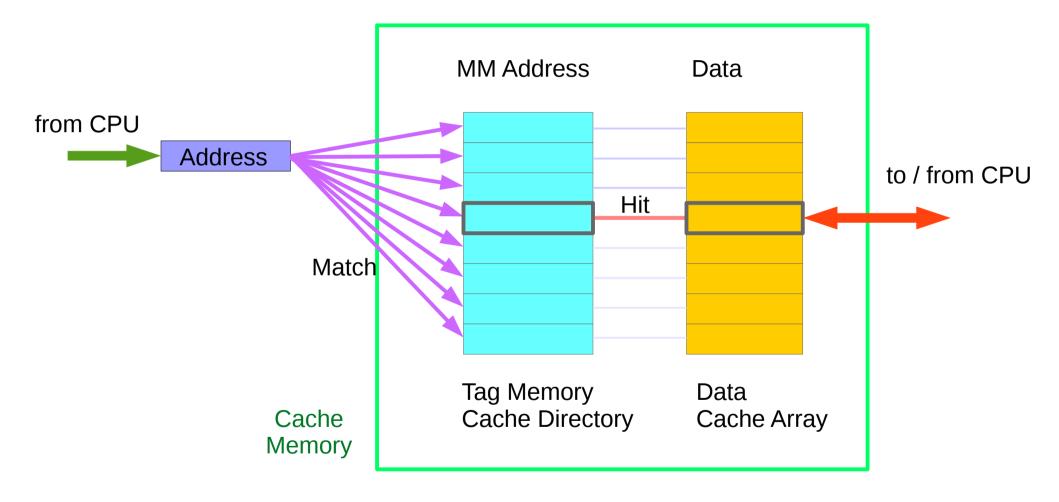

## Accessing Cache Memory : Address Matching

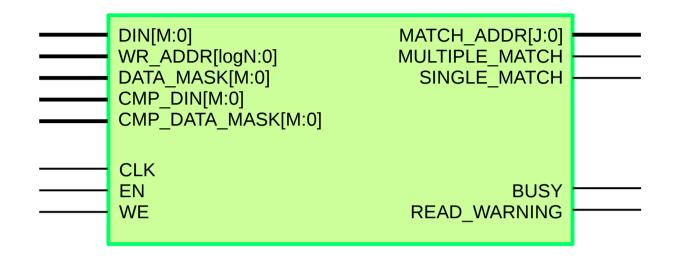

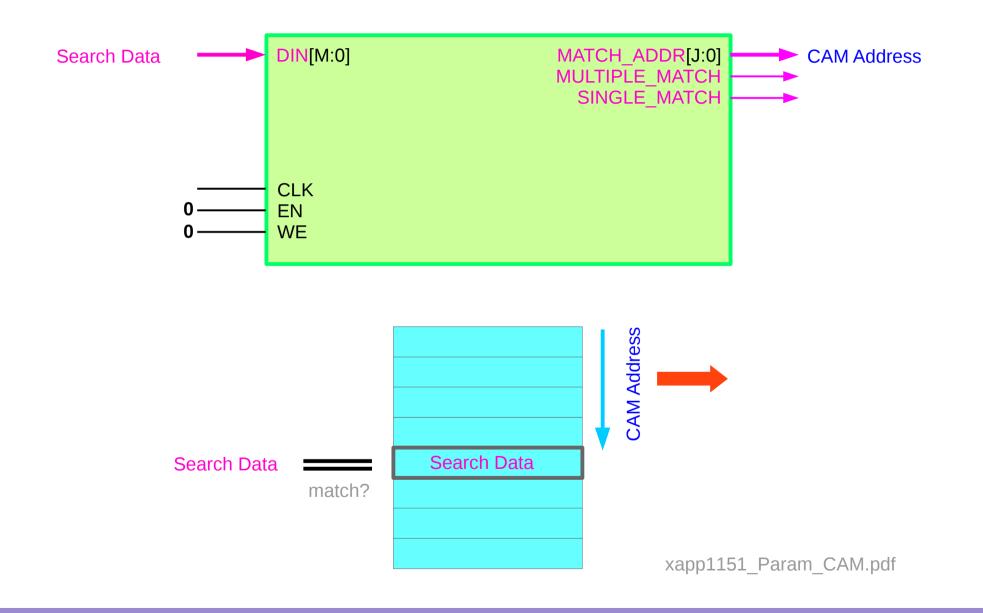

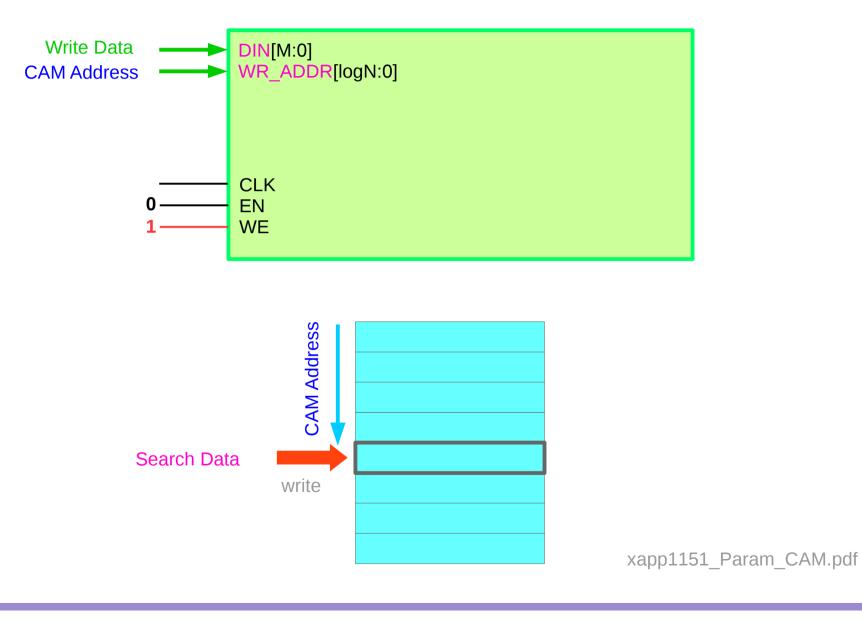

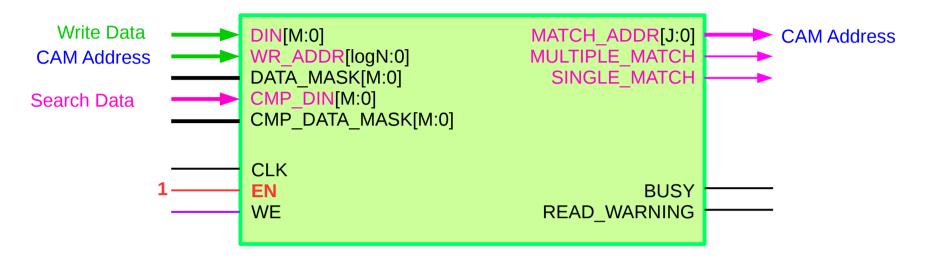

#### CAM (Content Addressable Memory) Interface

Xilinx CAM

xapp1151\_Param\_CAM.pdf

**Cache Memory**

Young Won Lim 5/23/16

#### CAM Read Operation – Search a key

**Cache Memory**

#### Write Operation

**Cache Memory**

EN=1 simultaneous write/read

Simultaneous Read/Write

Simultaneous write and search operations

With an output to warn the user of possible collision

Read warning flag:

The data applied to the CAM for a read

Matches the data that is currently being written into the CAM

By unfinished write operation

xapp1151\_Param\_CAM.pdf

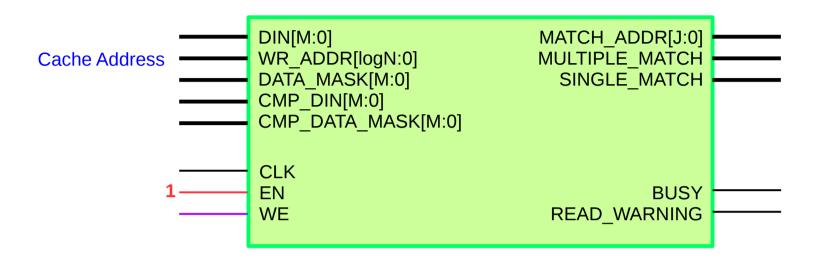

#### CAM (Content Addressable Memory)

EN=1 simultaneous write/read

| DIN[M:0] Data ir      | n Bus              |             |

|-----------------------|--------------------|-------------|

| The                   | data to be written | into        |

| The                   | data read from th  | e CAM       |

| Simultaneo            | ous read/write mo  | ode         |

| CMP                   | DIN for the read   | d operation |

| Standard Ternary mode |                    |             |

| DIN                   | DATÁ MASK          |             |

| 0                     | 0 -                | 0           |

| 1                     | 0                  | 1           |

| 0                     | 1                  | Х           |

| 1                     | 1                  | Х           |

CMP\_DIN[M:0] Compare Data In Bus Simultaneous read/write The data read from the CAM Ternary mode One of the two input buses To determine the bit value During read operation

xapp1151\_Param\_CAM.pdf

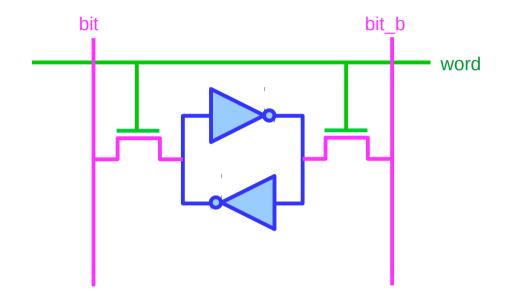

CMOS VLSI Design 4<sup>th</sup> ed, Weste

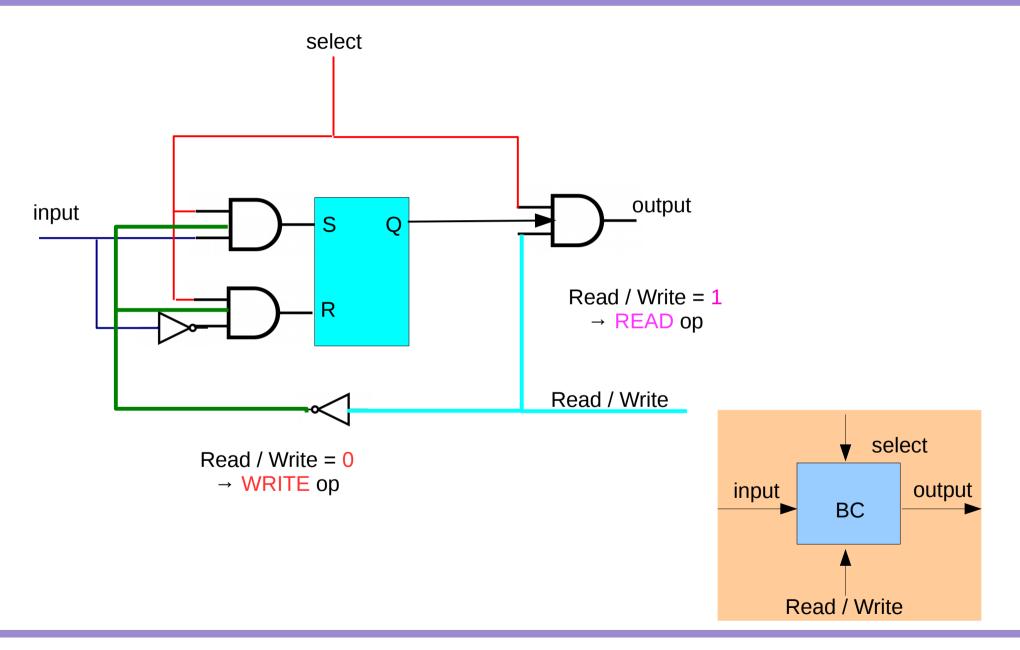

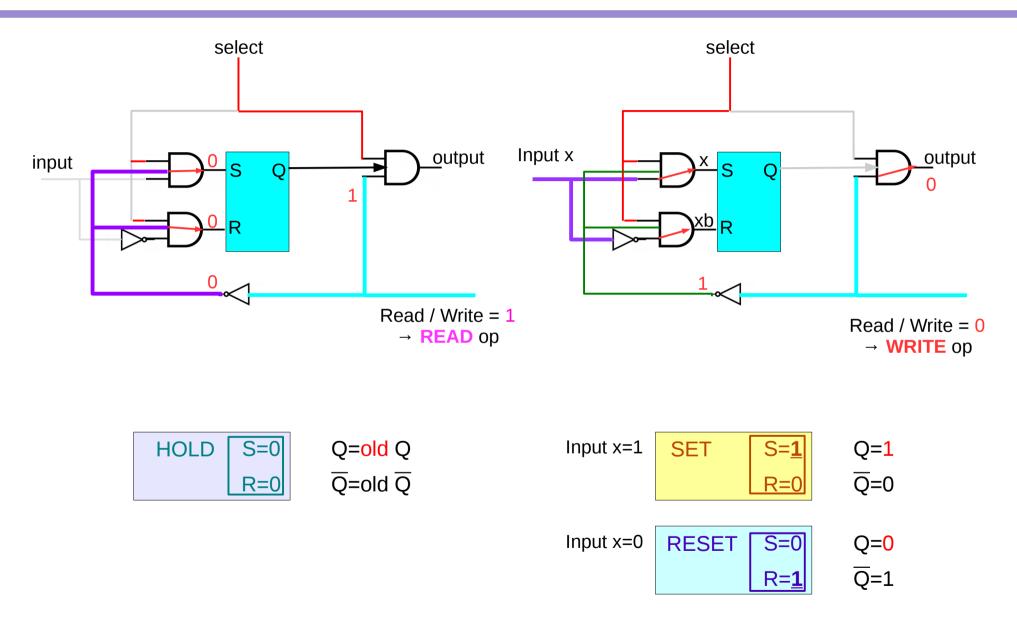

#### SRAM Bit Cell RTL Model

#### SRAM Bit Cell Read & Write Operations

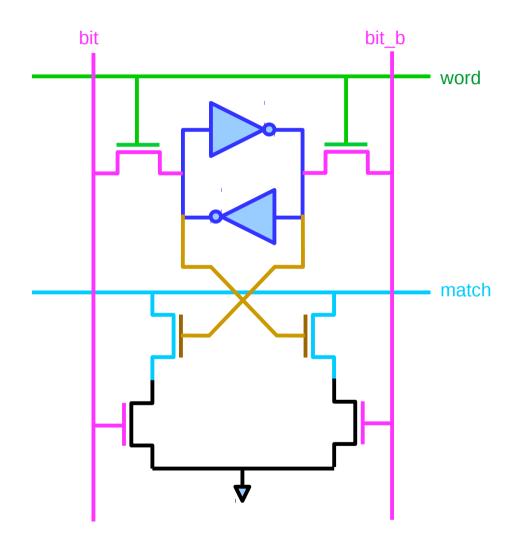

#### 10T CAM Cell

CMOS VLSI Design 4<sup>th</sup> ed, Weste

#### SRAM Bit Cell RTL Model

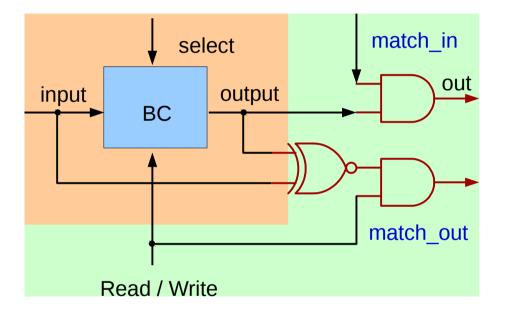

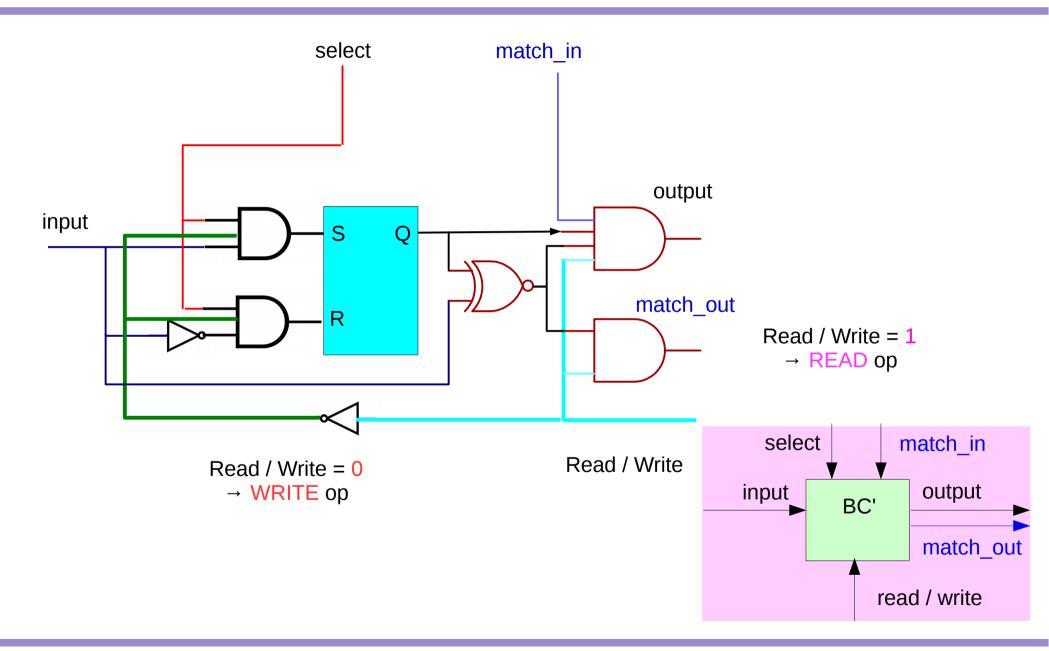

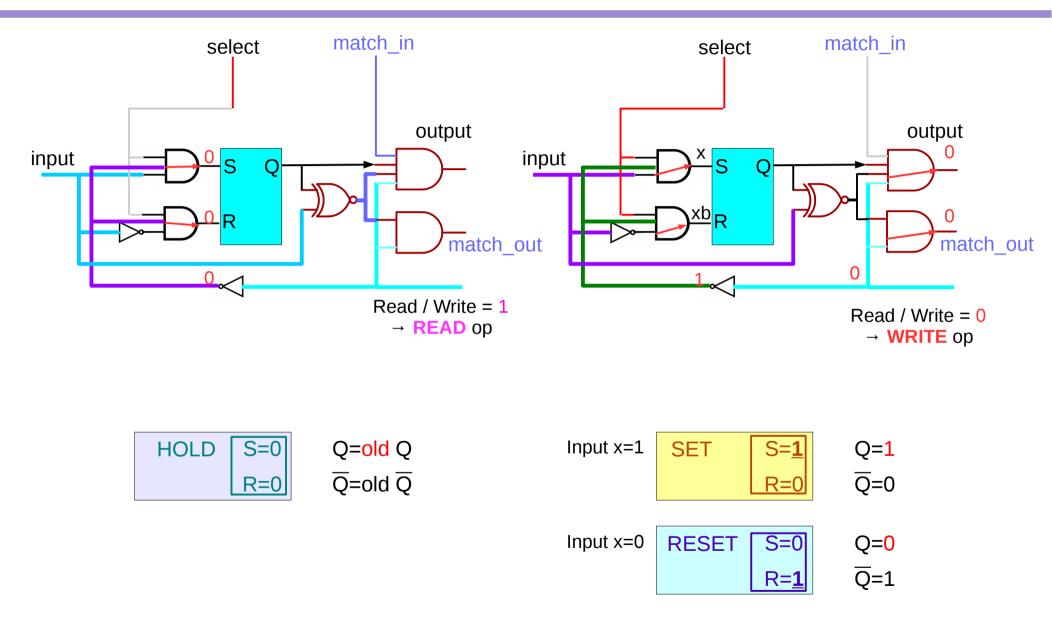

### CAM Bit Cell RTL Model

**Cache Memory**

### CAM Bit Cell RTL Model – Read / Write Operations

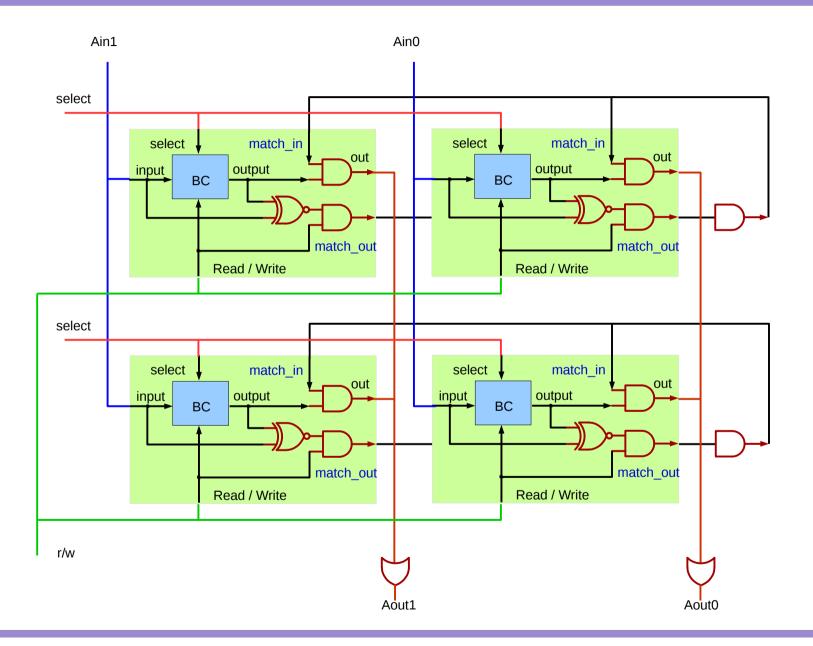

#### 2x2 CAM Bit Cell RTL Model

**Cache Memory**

20

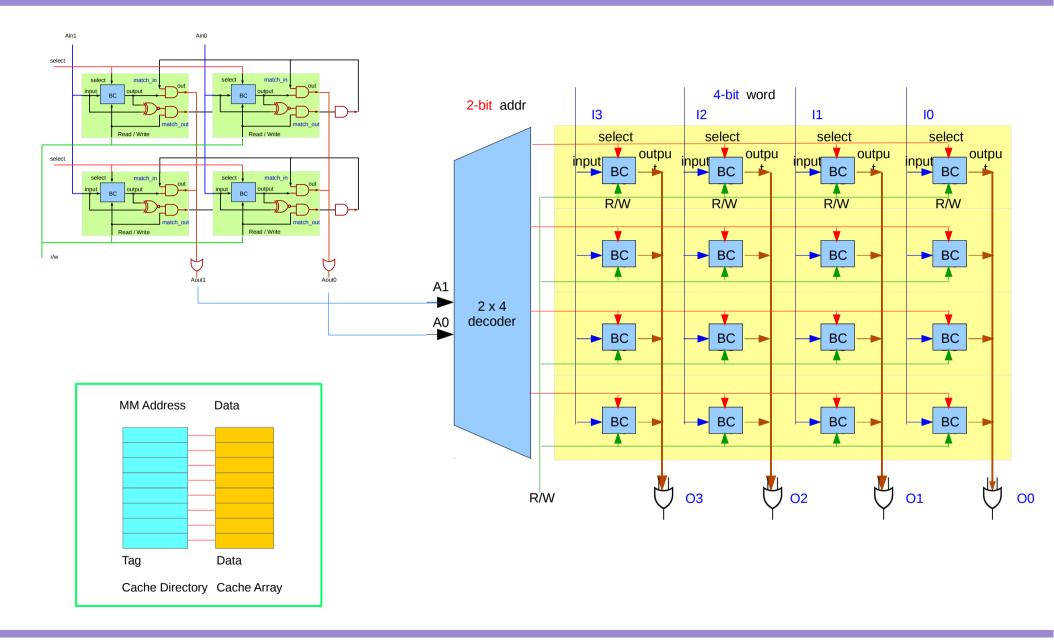

#### Diagram for a 4x4 Memory

#### **Cache Memory**

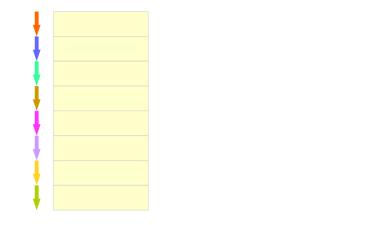

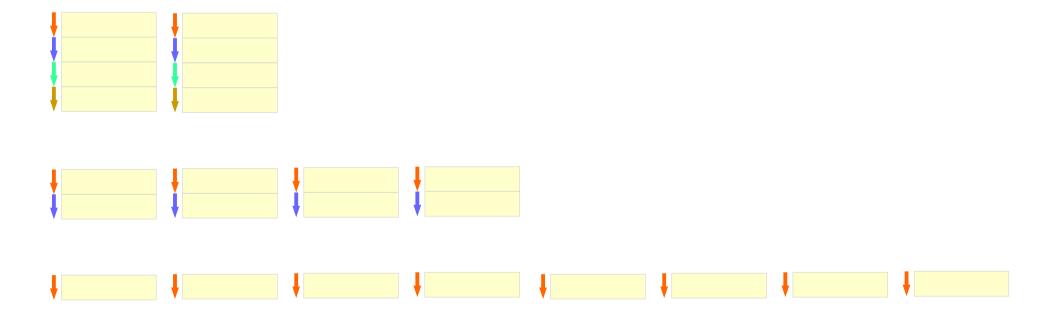

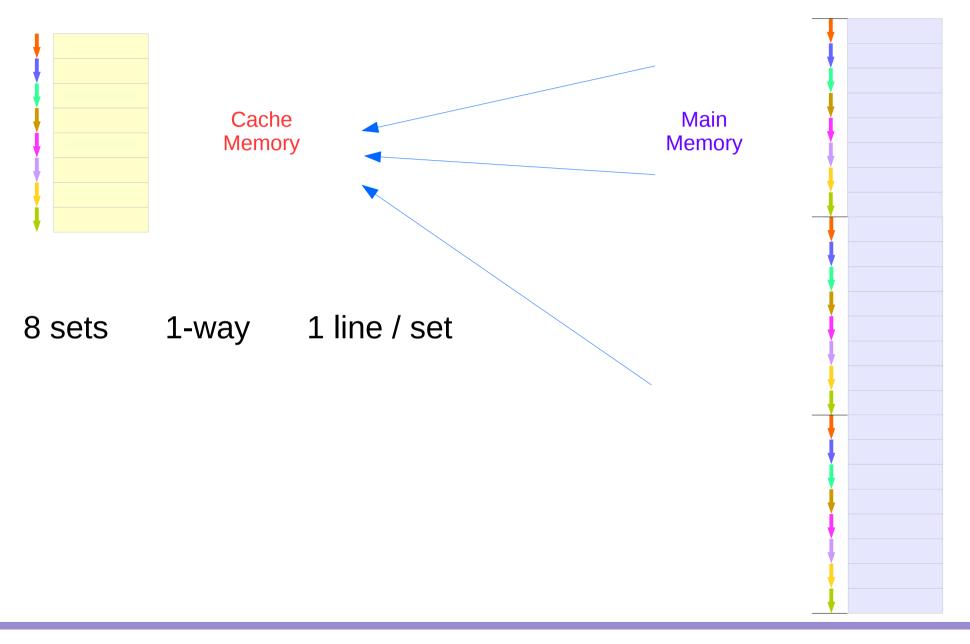

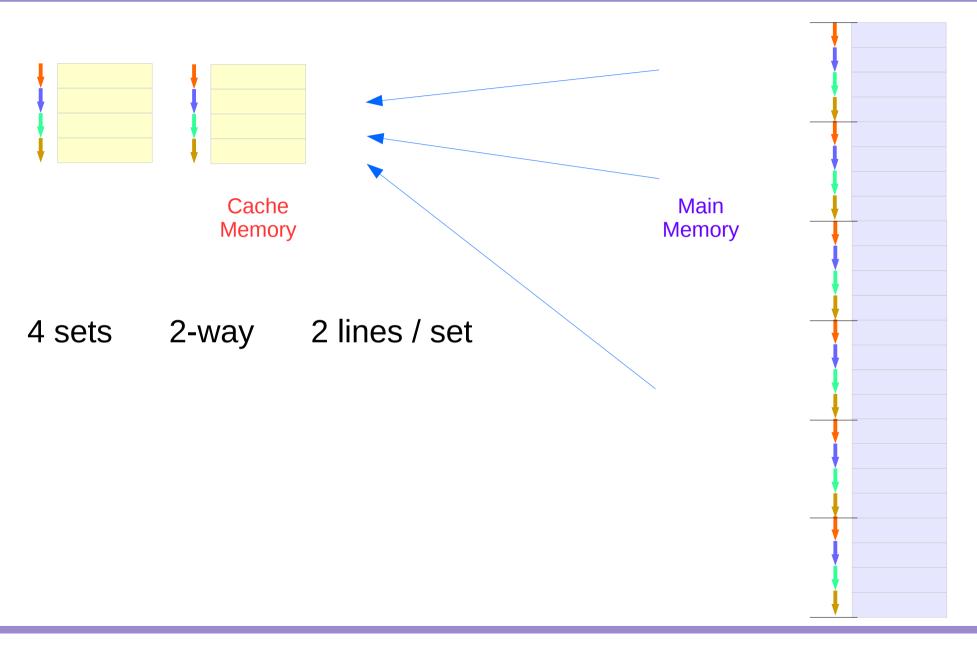

#### **Cache Organization**

| 8 sets | 1-way | 1 line / set  |

|--------|-------|---------------|

| 4 sets | 2-way | 2 lines / set |

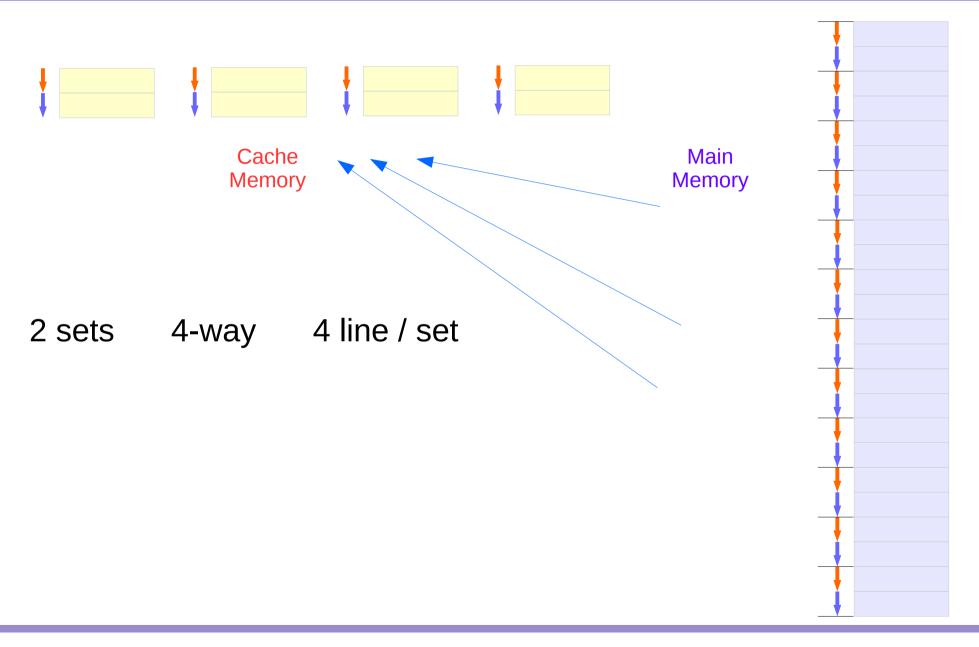

| 2 sets | 4-way | 4 lines / set |

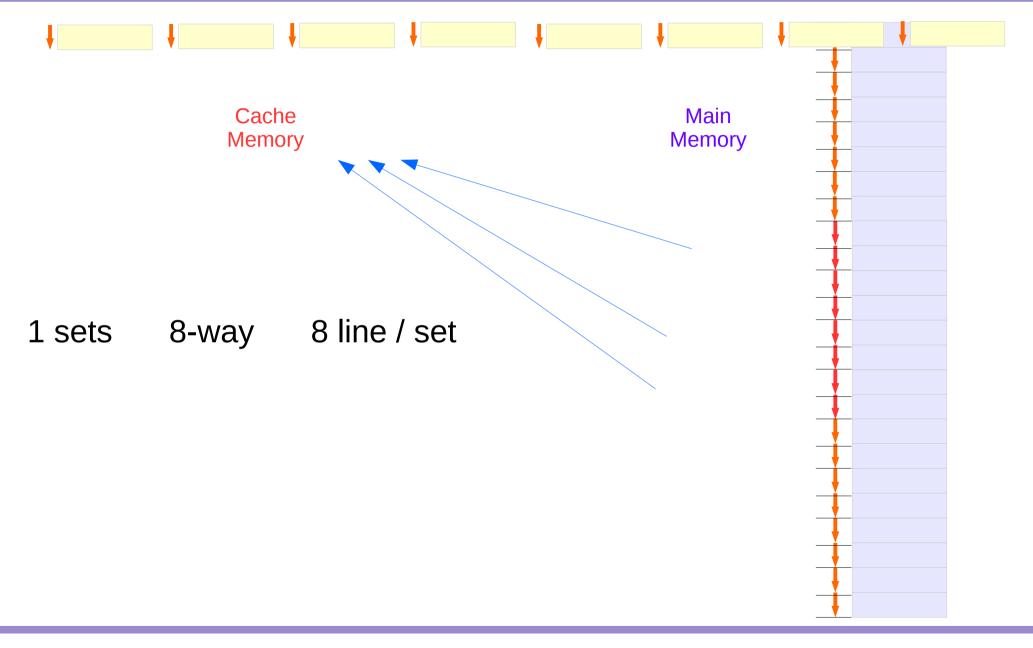

| 1 set  | 8-way | 8 lines / set |

## **Direct Mapping**

### 2-Way Set Associative Mapping

### 4-way Set Associative Mapping

## **Fully Associative Mapping**

# Tag Field

| tag set block |        |       |               |

|---------------|--------|-------|---------------|

|               | 8 sets | 1-way | 1 line / set  |

|               | 4 sets | 2-way | 2 lines / set |

|               | 2 sets | 4-way | 4 lines / set |

|               | 1 set  | 8-way | 8 lines / set |

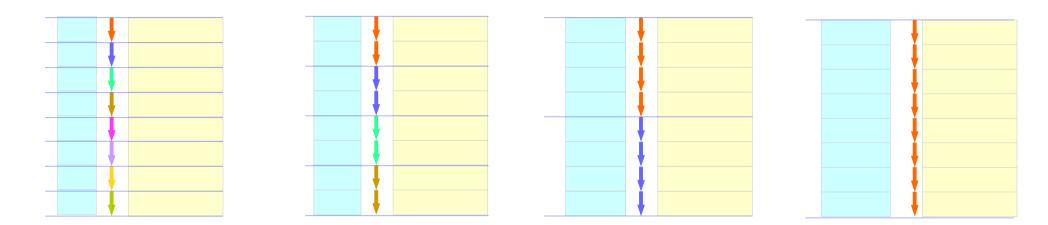

# Cache Mapping Method (set-view)

| 8 sets | 1-way | 1 line / set  |

|--------|-------|---------------|

| 4 sets | 2-way | 2 lines / set |

| 2 sets | 4-way | 4 lines / set |

| 1 set  | 8-way | 8 lines / set |

|        |       |               |

|        |       |               |

|        |       |               |

|        |       |               |

|        |       |               |

|        |       |               |

|        |       | ••••          |

#### Cache Mapping Method (set-view)

| 8 sets | 1-way | 1 line / set  |

|--------|-------|---------------|

| 4 sets | 2-way | 2 lines / set |

| 2 sets | 4-way | 4 lines / set |

| 1 set  | 8-way | 8 lines / set |

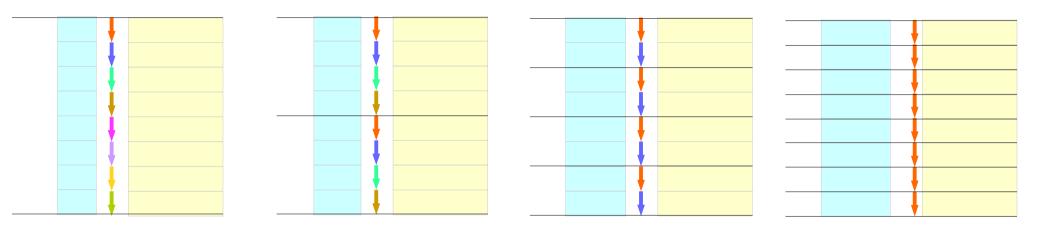

#### Cache Mapping Method (way-view)

| 8 sets | 1-way | 1 line / set  |

|--------|-------|---------------|

| 4 sets | 2-way | 2 lines / set |

| 2 sets | 4-way | 4 lines / set |

| 1 set  | 8-way | 8 lines / set |

#### CAM (Content Addressable Memory)

#### CAM (Content Addressable Memory)

#### References

- [1] http://en.wikipedia.org/

- [2] https://en.wikiversity.org/wiki/The\_necessities\_in\_SOC\_Design

- [3] https://en.wikiversity.org/wiki/The\_necessities\_in\_Digital\_Design

- [4] https://en.wikiversity.org/wiki/The\_necessities\_in\_Computer\_Design

- [5] https://en.wikiversity.org/wiki/The\_necessities\_in\_Computer\_Architecture

- [6] https://en.wikiversity.org/wiki/The\_necessities\_in\_Computer\_Organization

- [7] https://en.wikiversity.org/wiki/Understanding\_Embedded\_Software

- [8] Digital Systems, Hill, Peterson, 1987