# **Exceptions and Interrupts**

Young Won Lim 7/15/21 Copyright (c) 2021 - 2014 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using LibreOffice.

ARM System-on-Chip Architecture, 2<sup>nd</sup> ed, Steve Furber

Introduction to ARM Cortex-M Microcontrollers – Embedded Systems, Jonathan W. Valvano

Digital Design and Computer Architecture, D. M. Harris and S. L. Harris

ARM assembler in Raspberry Pi Roger Ferrer Ibáñez

https://thinkingeek.com/arm-assembler-raspberry-pi/

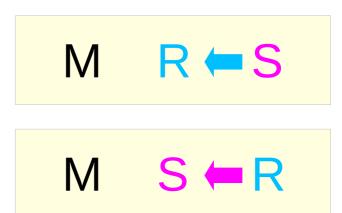

#### Status Reg to General Reg Transfer Instructions

Status Register to General Register Transfer Instructions MRS {<cond>} Rd, CPSR | SPSR

| MRS               | Rd, CPSR |

|-------------------|----------|

| MRS               | Rd, SPSR |

| MRS <cond></cond> | Rd, CPSR |

| MRS <cond></cond> | Rd, SPSR |

ISA (4A) Assembler Format – Data Processing Young Won Lim 7/15/21

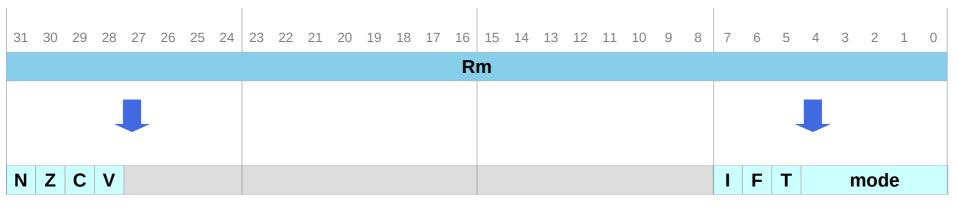

#### General Reg to Status Reg Transfer Instructions

General Register to Status Register Transfer Instructions MSR {<cond>} CPSR f | SPSR f, #<32-bit immediate> MSR {<cond>} CPSR <field> | SPSR <field>, Rm

- <field> is one of

- c : the control field PSR[7:0]

- x : the extension field

- s : the status field

- f : the flag field

- PSR[31:24]

- PSR[15: 8] (unused on current ARMs)

- PSR[23:16] (unused on current ARMs)

- MSR CPSR f, #<32-bit immediate> **MSR** SPSR f, #<32-bit immediate> MSR <cond> CPSR f, #<32-bit immediate> MSR <cond> SPSR f, #<32-bit immediate> **MSR** CPSR <field>, Rm MSR SPSR <field>, Rm CPSR <field>, Rm MSR <cond> MSR <cond> SPSR <field>, Rm

Young Won Lim 7/15/21

M S  $\leftarrow$  R

#### **ISA (4A) Assembler** Format – Data Processing

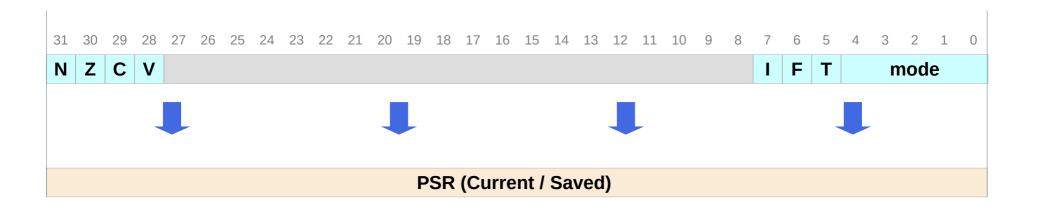

#### **CPSR** and **SPSR**

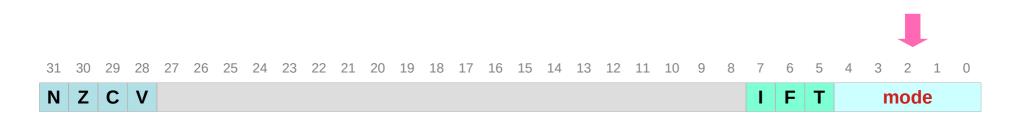

#### 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 0 31 1 Ν Z C V Т F Т mode

#### Current Program Status Register (CPSR) Saved Program Status Register (SPSR)

N Negative flag

Z Zero flag

C Carry flag

V Overflow flag

To disable Interrupt (IRQ), set I To disable Fast Interrupt (FIQ), set F the **T** bit shows running in the Thumb state

| Usr (usr)            | 1 | 0 | 0 | 0 | 0 |

|----------------------|---|---|---|---|---|

| Fast Interrupt (fiq) | 1 | 0 | 0 | 0 | 1 |

| Interrupt (irq)      | 1 | 0 | 0 | 1 | 0 |

| Supervisor (svc)     | 1 | 0 | 0 | 1 | 1 |

| Abort (abt)          | 1 | 0 | 1 | 1 | 1 |

| Undefined (und)      | 1 | 1 | 0 | 1 | 1 |

| System (sys)         | 1 | 1 | 1 | 1 | 1 |

#### CPSR and SPSR Fields

| 31 30 29 28 27 26 25 24              | 23 22 21 20 19 18 17 16    | 15 14 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |

|--------------------------------------|----------------------------|-----------------------|-----------------|--|--|--|--|--|--|--|

|                                      | <b>Current Program Sta</b> | tus Register (CPSR)   |                 |  |  |  |  |  |  |  |

|                                      |                            |                       |                 |  |  |  |  |  |  |  |

| CPSR_f                               | CPSR_s                     | CPSR_x                | CPSR_c          |  |  |  |  |  |  |  |

|                                      |                            |                       |                 |  |  |  |  |  |  |  |

|                                      |                            |                       |                 |  |  |  |  |  |  |  |

| Saved Program Status Register (SPSR) |                            |                       |                 |  |  |  |  |  |  |  |

|                                      |                            |                       |                 |  |  |  |  |  |  |  |

| SPSR_f                               | SPSR_s                     | SPSR_x                | SPSR_c          |  |  |  |  |  |  |  |

|                                      |                            |                       |                 |  |  |  |  |  |  |  |

|                                      |                            |                       |                 |  |  |  |  |  |  |  |

|                                      |                            |                       |                 |  |  |  |  |  |  |  |

| NZCV                                 |                            |                       | I F T mode      |  |  |  |  |  |  |  |

|                                      |                            |                       |                 |  |  |  |  |  |  |  |

| flag field                           | status field               | extension field       | control field   |  |  |  |  |  |  |  |

#### To a General Reg From a Status Reg

MRS Rd, CPSR MRS Rd, SPSR

#### To a Status Reg From a General Reg

| 3 | . 3 | 80 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18  | 17  | 16    | 15  | 14   | 13  | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |

|---|-----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|-------|-----|------|-----|----|----|----|---|---|---|---|---|---|---|-----|---|---|

|   |     |    |    |    |    |    |    |    |    |    |    |    | ÷  | #<3 | 2-b | it in | nme | edia | te> | ,  |    |    |   |   |   |   |   |   |   |     |   |   |

|   |     |    |    |    |    |    |    |    |    |    |    |    |    |     |     |       |     |      |     |    |    |    |   |   |   |   |   |   |   |     |   |   |

|   |     |    |    |    |    |    |    |    |    |    |    |    |    |     |     |       |     |      |     |    |    |    |   |   |   |   |   |   |   |     |   |   |

|   |     |    |    |    |    |    |    |    |    |    |    |    |    |     |     |       |     |      |     |    |    |    |   |   |   |   |   |   |   |     |   |   |

| N | I Z | Z  | С  | V  |    |    |    |    |    |    |    |    |    |     |     |       |     |      |     |    |    |    |   |   | I | F | Т |   | n | nod | е |   |

MSR CPSR\_f , #<32-bit immediate> MSR SPSR\_f , #<32-bit immediate> MSR CPSR\_c , #<32-bit imm> MSR SPSR\_c , #<32-bit imm>

MSR CPSR\_f , Rm MSR SPSR\_f , Rm MSR CPSR\_c , Rm MSR SPSR\_c , Rm

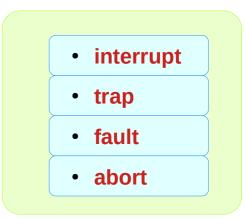

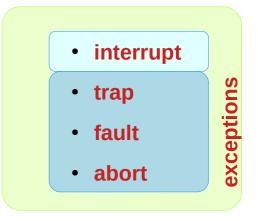

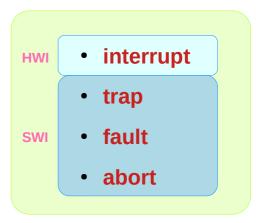

#### Interrupt is an Exception

#### There are four classes of exception:

- interrupt

- trap

- fault

- abort

Interrupt is one of the classes of exception.

**Interrupt** occurs asynchronously and it is triggered by signal which is from I/O device that are external by processor.

After exception handler finish handling this interrupt (exception processing), handler will always return to <u>next instruction</u>.

#### exceptions

https://stackoverflow.com/questions/7295936/what-is-the-difference-between-interrupt-and-exception-context

### Exceptions vs interrupts (1)

Interrupts and exceptions both alter the program flow.

- **interrupts** are used to handle external events (serial ports, keyboard)

- **exceptions** are used to handle instruction faults (division by zero, undefined opcode).

**interrupts** are handled by the processor <u>after</u> finishing the <u>current</u> <u>instruction</u>.

If it finds a signal on its interrupt pin, it will look up the address of the interrupt handler in the interrupt table and pass that routine control.

After <u>returning</u> from the <u>interrupt handler</u> routine, it will <u>resume</u> program execution at the next instruction after the interrupted instruction.

https://stackoverflow.com/questions/7295936/what-is-the-difference-between-interrupt-and-exception-context

#### Assembly Programming Exceptions and Interrupts

### Exceptions vs interrupts (2)

Exceptions on the other hand are divided into three kinds. Faults, Traps and Aborts.

**Faults** are detected and serviced by the processor before the <u>faulting instructions</u>.

**Traps** are serviced after the <u>instruction</u> causing the <u>trap</u>.

User defined interrupts go into this category and can be said to be traps;

this includes the MS- DOS **INT 21h** software interrupt, for example.

Aborts are used only to signal <u>severe</u> system <u>problems</u>, when operation is <u>no longer possible</u>.

https://stackoverflow.com/questions/7295936/what-is-the-difference-between-interrupt-and-exception-context

#### Trap

It is typically a type of synchronous interrupt caused by an exceptional condition (e.g., breakpoint, division by zero, invalid memory access).

#### Fault

Fault exception is used in a client application to catch contractually-specified SOAP faults. By the simple exception message, you <u>can't identify</u> the <u>reason</u> of the exception, that's why a Fault Exception is useful.

#### Abort

It is a type of exception occurs when an instruction fetch causes an error. SOAP (formerly an acronym for Simple Object Access Protocol) is a messaging protocol specification for exchanging structured information in the implementation of web services in computer networks.

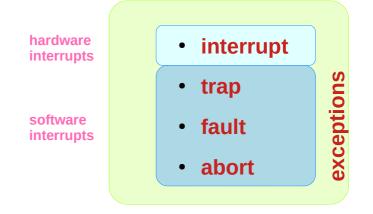

Interrupt is one of the classes of Exception. There are 4 classes of Exception - interrupt, trap, fault and abort.

Even though there are many differences, **interrupt** belongs to **exception** still

In any computer, during its normal execution of a program, there could be events that can cause the CPU to temporarily halt. Events like this are called interrupts.

Interrupts can be caused by either software or hardware faults.

- hardware interrupts are called Interrupts

- software interrupts are called Exceptions

https://www.geeksforgeeks.org/difference-between-interrupt-and-exception/

external, asynchronous internal, instruction

### Exceptions vs interrupts (5)

The term **Interrupt** is usually reserved for hardware interrupts.

They are program control interruptions caused by external hardware events.

Here, external means external to the CPU.

Hardware interrupts usually come from many different sources

- timer chip

- peripheral devices (keyboards, mouse, etc.)

- I/O ports (serial, parallel, etc.)

- disk drives, CMOS clock

- expansion cards (sound / video card, etc)

That means hardware interrupts almost <u>never</u> occur due to some event related to the <u>executing</u> program.

https://www.geeksforgeeks.org/difference-between-interrupt-and-exception/

**Exception** is a software interrupt, which can be identified as a special handler routine.

Exception can be identified as an automatically occurring **trap**.

Generally, there are no specific instructions associated with exceptions

traps are generated

using a specific instruction

int is x86 jargon for "trap instruction"

a call to a predefined interrupt handler.

So, an **exception** occurs due to an "exceptional" condition that occurs <u>during program execution</u>.

### Exceptions vs interrupts (6)

| Interrupt                                                                                                          | Exception                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| These are Hardware interrupts.                                                                                     | These are Software Interrupts.                                                                                                                                    |

| • Occurrences of hardware interrupts usually disable other hardware interrupts.                                    | <ul> <li>This is not a true case in terms of<br/>Exception. (does not disable other<br/>exceptions)</li> </ul>                                                    |

| <ul> <li>These are <u>asynchronous</u> <u>external</u><br/>requests for <u>service</u></li> </ul>                  | <ul> <li>These are <u>synchronous</u> internal<br/>requests for service based upon</li> </ul>                                                                     |

| (like keyboard or printer needs service).                                                                          | <u>abnormal events</u><br>(think of illegal instructions, illegal<br>address, overflow etc).                                                                      |

| <ul> <li>Being asynchronous, interrupts can<br/>occur at any place in the program.</li> </ul>                      | <ul> <li>Being synchronous, exceptions occur<br/>when there is abnormal event in your<br/>program like, divide by zero or illegal<br/>memory location.</li> </ul> |

| <ul> <li>These are normal events and<br/>shouldn't interfere with the normal<br/>running of a computer.</li> </ul> | • These are abnormal events and often result in the termination of a program                                                                                      |

#### Interrupt examples

An event like a key press on the keyboard, or an internal hardware timer timing out can *raise* this kind of interrupt and can *inform* the CPU that a certain device needs some attention.

the CPU will stop whatever it was doing, provides the service required by the device and will get back to the normal program.

When hardware interrupts occur and the CPU starts the **ISR**, other hardware interrupts are *disabled* (e.g. in 80×86 machines). If you need other hardware interrupts to occur while the ISR is running, you need to do that explicitly by clearing the interrupt flag with CLI / STI instruction in 80x86 with MSR in ARM

In 80×86 machines, clearing the interrupt flag will only affect hardware interrupts.

Division by zero, execution of an illegal opcode or memory related fault could cause exceptions.

Whenever an exception is raised, the CPU temporarily *suspends* the program it was executing and starts the **ISR**.

**ISR** will contain what to do with the exception.

It may correct the problem or if it is not possible, it may abort the program gracefully by printing a suitable error message. Although a specific instruction does <u>not</u> cause an exception, an exception will always be caused by an instruction.

For example, the division by zero error can only occur during the execution of the division instruction.

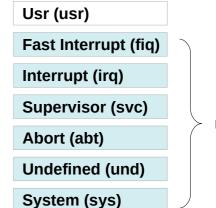

### (1) Mode of operations

- 7 modes of operation.

- most application programs execute in user mode

- Non user modes (called **privileged** modes) are entered to serve **interrupts** or **exceptions**

non-user

### (2) Mode of operations

• The **system** mode is special mode for <u>accessing protected resources</u>.

Because **exception handlers** in **system mode** does <u>not</u> use *registers*,

errors in exception handler <u>cannot</u> <u>corrupt</u> registers

| Usr (usr)            |    |

|----------------------|----|

| Fast Interrupt (fiq) |    |

| Interrupt (irq)      |    |

| Supervisor (svc)     |    |

| Abort (abt)          | 11 |

| Undefined (und)      |    |

| System (sys)         |    |

non-user

### (3) Mode of operations

• **switching** between modes can be done <u>manually</u> through modifying the **mode bits** in the **CPSR** register.

| Usr (usr)            | 1 | 0 | 0 | 0 | 0 |

|----------------------|---|---|---|---|---|

| Fast Interrupt (fiq) | 1 | 0 | 0 | 0 | 1 |

| Interrupt (irq)      | 1 | 0 | 0 | 1 | 0 |

| Supervisor (svc)     | 1 | 0 | 0 | 1 | 1 |

| Abort (abt)          | 1 | 0 | 1 | 1 | 1 |

| Undefined (und)      | 1 | 1 | 0 | 1 | 1 |

| System (sys)         | 1 | 1 | 1 | 1 | 1 |

### (4) Mode of operations

| Process | sor Mode   | Description                               |

|---------|------------|-------------------------------------------|

| USR     | User       | Normal program execution mode             |

| FIQ     | FIQ        | Fast data processing mode                 |

| IRQ     | IRQ        | For general purpose interrupts            |

| SVC     | Supervisor | A protected mode for the OS               |

| ABT     | Abort      | When data or instruction fetch is aborted |

| UND     | Undefined  | For undefined instructions                |

| SYS     | System     | Privileged mode for OS Tasks              |

#### Switching between these modes requires saving/loading register values

### (4) Mode of operations

- User mode is an unprivileged mode, and has restricted access to system resources.

- Non-user modes

- have full access to system resources in the <u>current</u> security state,

- can <u>change</u> mode freely,

- <u>execute</u> software as <u>privileged</u>.

- Non-user mode are entered

- to service exceptions,

- or to <u>access</u> privileged resources.

- Applications that require task protection usually execute in User mode.

- Some **embedded applications** might run entirely in **Non-user** mode.

- An **application** that requires **full** access to system resources usually executes in **System** mode.

https://www.keil.com/support/man/docs/armasm/armasm\_dom1359731126962.htm

### (5) Mode of operations

- **Supervisor** (**svc**) mode: A **privileged** mode entered whenever the CPU is reset or when an SVC instruction is executed.

- whereas System mode is the only privileged mode that is <u>not</u> entered <u>by an exception</u>.

- It can only be entered by executing an instruction that <u>explicitly</u> writes to the **mode bits** of the Current Program Status Register (CPSR).

- So, the exception handlers <u>modify</u> the CPSR to enter System mode.

- Usage: **Corruption** of the **link register** can be a problem when handling **multiple exceptions** of the same.

- the System mode <u>shares</u> the same registers as User mode, it can run <u>tasks</u> that require <u>privileged access</u>, and exceptions <u>no longer overwrite</u> the link register.

- Linux kernel has done it this way, so that whenever any interrupt occurs in first level IRQ handler, it copies IRQ registers to SVC registers and switch the ARM to SVC mode.

https://www.quora.com/In-ARM-processor-what-is-the-difference-in-supervisor-mode-and-system-mode

### (3) ARM Register Set

- ARM processor has **37** 32-bit registers.

- 31 registers are general purpose registers.

- 6 registers are control registers

- Registers are named from R0 to R16 with some registers banked in different modes

- R13 is the stack pointer SP (banked)

R13, R13\_fiq, R13\_irq, R13\_svc, R13\_abt, R13\_und

- **R14** is subroutine link register **LR** (banked) R14, R14\_fiq, R14\_irq, R14\_svc, R14\_abt, R14\_und

- R15 is program counter PC

- **R16** is current program status register **CPSR** (banked) CPSR, SPSR\_irq, SPSR\_irq, SPSR\_svc, SPSR\_abt, SPSR\_und

htti Banked registers lio/mc404-2013/arm-manuals/ARM\_exception\_slides.pdf

- R8, R8\_fiq

- R9, R9\_fiq

- R10, R10\_fiq

- R11, R11\_fiq

- R12, R12\_fiq

#### The same registers across different modes

| User     | System   | Fast Interrupt | Interrupt | Supervisor | Abort    | Undefined |

|----------|----------|----------------|-----------|------------|----------|-----------|

| R0       | R0       | R0             | R0        | R0         | R0       | R0        |

| R1       | R1       | R1             | R1        | R1         | R1       | R1        |

| R2       | R2       | R2             | R2        | R2         | R2       | R2        |

| R3       | R3       | R3             | R3        | R3         | R3       | R3        |

| R4       | R4       | R4             | R4        | R4         | R4       | R4        |

| R5       | R5       | R5             | R5        | R5         | R5       | R5        |

| R6       | R6       | R6             | R6        | R6         | R6       | R6        |

| R7       | R7       | R7             | R7        | R7         | R7       | R7        |

| R8       | R8       | R8_fiq         | R8        | R8         | R8       | R8        |

| R9       | R9       | R9_fiq         | R9        | R9         | R9       | R9        |

| R10      | R10      | R10_fiq        | R10       | R10        | R10      | R10       |

| R11      | R11      | R11_fiq        | R11       | R11        | R11      | R11       |

| R12      | R12      | R12_fiq        | R12       | R12        | R12      | R12       |

| R13 (SP) | R13 (SP) | R13_fiq        | R13_irq   | R13_svc    | R13_abt  | R13_und   |

| R14 (LR) | R14 (LR) | R14_fiq        | R14_irq   | R14_svc    | R14_abt  | R14_und   |

| R15 (PC) | R15 (PC) | R15 (PC)       | R15 (PC)  | R15 (PC)   | R15 (PC) | R15 (PC)  |

| CPSR     | CPSR     | CPSR           | CDSD      | CDSD       | CPSR     | CPSR      |

| Crok     | CPSK     |                | CPSR      | CPSR       |          |           |

|          |          | SPSR_fiq       | SPSR_irq  | SPSR_svc   | SPSR_abt | SPSR_und  |

http://www.cs.otago.ac.nz/cosc440/readings/arm-syscall.pdf

#### ARM Architecture (1A) Programmer's Model

### Actual number of different registers

| 16+1     | 0            | 7+1      | 2+1            | 2+1            | 2+1      | 2+1      |

|----------|--------------|----------|----------------|----------------|----------|----------|

| R0       | R0           | R0       | R0             | R0             | R0       | R0       |

| R1       | R1           | R1       | R1             | R1             | R1       | R1       |

| R2       | R2           | R2       | R2             | R2             | R2       | R2       |

| R3       | R3           | R3       | R3             | R3             | R3       | R3       |

| R4       | R4           | R4       | 31 general pur | oose registers | R4       | R4       |

| R5       | R5           | R5       | R5             | R5             | R5       | R5       |

| R6       | R6           | R6       | R6             | R6             | R6       | R6       |

| R7       | R7           | R7       | R7             | R7             | R7       | R7       |

| R8       | R8           | R8_fiq   | R8             | R8             | R8       | R8       |

| R9       | R9           | R9_fiq   | R9             | R9             | R9       | R9       |

| R10      | R10          | R10_fiq  | R10            | R10            | R10      | R10      |

| R11      | R11          | R11_fiq  | R11            | R11            | R11      | R11      |

| R12      | R12          | R12_fiq  | R12            | R12            | R12      | R12      |

| R13 (SP) | R13 (SP)     | R13_fiq  | R13_irq        | R13_svc        | R13_abt  | R13_und  |

| R14 (LR) | R14 (LR)     | R14_fiq  | R14_irq        | R14_svc        | R14_abt  | R14_und  |

| R15 (PC) | R15 (PC)     | R15 (PC) | R15 (PC)       | R15 (PC)       | R15 (PC) | R15 (PC) |

|          |              |          |                |                |          |          |

| CPSR     | CPSR         | CPSR     | CPSR           | CPSR           | CPSR     | CPSR     |

| 6 contro | ol registers | SPSR_fiq | SPSR_irq       | SPSR_svc       | SPSR_abt | SPSR_und |

http://www.cs.otago.ac.nz/cosc440/readings/arm-syscall.pdf

#### ARM Architecture (1A) Programmer's Model

#### **ARM Processor Registers**

| User     | System   | Fast Interrupt | Interrupt | Supervisor | Abort    | Undefined |

|----------|----------|----------------|-----------|------------|----------|-----------|

| R0       | R0       | R0             | R0        | R0         | R0       | R0        |

| R1       | R1       | R1             | R1        | R1         | R1       | R1        |

| R2       | R2       | R2             | R2        | R2         | R2       | R2        |

| R3       | R3       | R3             | R3        | R3         | R3       | R3        |

| R4       | R4       | R4             | R4        | R4         | R4       | R4        |

| R5       | R5       | R5             | R5        | R5         | R5       | R5        |

| R6       | R6       | R6             | R6        | R6         | R6       | R6        |

| R7       | R7       | R7             | R7        | R7         | R7       | R7        |

| R8       | R8       | R8_fiq         | R8        | R8         | R8       | R8        |

| R9       | R9       | R9_fiq         | R9        | R9         | R9       | R9        |

| R10      | R10      | R10_fiq        | R10       | R10        | R10      | R10       |

| R11      | R11      | R11_fiq        | R11       | R11        | R11      | R11       |

| R12      | R12      | R12_fiq        | R12       | R12        | R12      | R12       |

| R13 (SP) | R13 (SP) | R13_fiq        | R13_irq   | R13_svc    | R13_abt  | R13_und   |

| R14 (LR) | R14 (LR) | R14_fiq        | R14_irq   | R14_svc    | R14_abt  | R14_und   |

| R15 (PC) | R15 (PC) | R15 (PC)       | R15 (PC)  | R15 (PC)   | R15 (PC) | R15 (PC)  |

| CPSR     | CPSR     | CPSR           | CPSR      | CPSR       | CPSR     | CPSR      |

|          |          | SPSR_fiq       | SPSR_irq  | SPSR_svc   | SPSR_abt | SPSR_und  |

http://www.cs.otago.ac.nz/cosc440/readings/arm-syscall.pdf

#### ARM Architecture (1A) Programmer's Model

### (4) Exceptions

An exception is any condition that needs to halt normal execution of the instructions

#### Examples

- Resetting ARM core

- Failure of fetching instructions

- HWI

- SWI

#### exceptions

Each exception causes the ARM core to enter a specific mode.

| Exception               | Mode | Purpose                         |     |

|-------------------------|------|---------------------------------|-----|

| Fast Interrupt Request  | FIQ  | Fast Interrupt handling         |     |

| Interrupt Request       | IRQ  | Normal interrupt handling       |     |

| SWI and RESET           | SVC  | Protected mode for OS           |     |

| Pre-fetch or data abort | ABT  | Memory protection handling      | Swi |

| Undefined Instruction   | UND  | SW emulation of HW coprocessors |     |

### (6) Vector table

a table of addresses that the ARM core branches to when an exception is raised there is always branching instructions that direct the core to the ISR.

At this place in memory, we find a branching instruction

#### ldr pc, [pc, #\_IRQ\_handler\_offset]

| 0x0000 0000 | ldr pc, [pc, #offset0]                |

|-------------|---------------------------------------|

| 0x0000 0004 | ldr pc, [pc, #offset1]                |

| 0x0000 0008 | ldr pc, [pc, #offset2]                |

| 0x0000 000C | ldr pc, [pc, #offset <mark>3</mark> ] |

| 0x0000 0010 | ldr pc, [pc, #offset4]                |

| 0x0000 0014 | ldr pc, [pc, #offset5]                |

| 0x0000 0018 | ldr pc, [pc, #offset6]                |

| 0x0000 001C | ldr pc, [pc, #offset7]                |

|             |                                       |

## (7) Exception priorities

| Exception  | Priority | l bit | F bit |

|------------|----------|-------|-------|

| Reset      | 1        | 1     | 1     |

| Data Abort | 2        | 1     | -     |

| FIQ        | 3        | 1     | 1     |

| IRQ        | 4        | 1     | -     |

| Prefetch   | 5        | 1     | -     |

| SWI        | 6        | 1     | -     |

| Undefined  | 6        | 1     | -     |

| Mode | Priority                 |

|------|--------------------------|

| FIQ  | 3                        |

| IRQ  | 4                        |

| SVC  | 6, 1                     |

| ABT  | 5, 2                     |

| UND  | 6                        |

|      | FIQ<br>IRQ<br>SVC<br>ABT |

Priority decides which of the currently raised exceptions is more important

I bit and **F** bit decide if the exception handler itself can be interrupted during execution or not?

SWI and Undefined instruction : both are caused by an instruction entering the execution stage of the ARM instruction pipeline

Link Register OffsetThis register is used to return the PC to the appropriate place in the interrupted task since this is not always the old PCvalue. It is modified depending on the type of exception.

The PChas advanced beyond the instruction causing the exception. Upon exit of the prefetch abort exception handler, software must re-load the PC back one instruction from the PCsaved at the time of the exception

| Exception                  | <b>Returning Address</b> |

|----------------------------|--------------------------|

| Reset                      | None                     |

| Data Abort                 | LR-8                     |

| FIQ, IRQ, prefetch Abort   | LR-4                     |

| SWI, Undefined Instruction | LR                       |

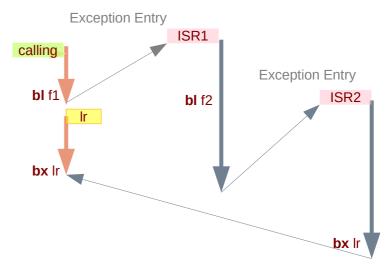

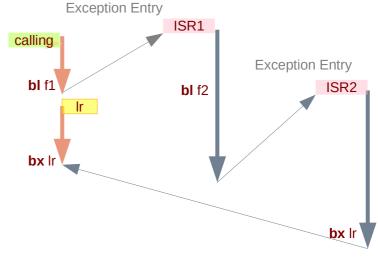

### (9) Entering and returning exception handler

Entering exception handler1.Save the address of the next instruction in the appropriate Link Register LR.2.Copy CPSRto the SPSRof new mode.3.Change the mode by modifying bits in CPSR.4.Fetch next instruction from the vector table.

Leaving exception handler 1.Move the Link Register LR(minus an offset) to the PC. 2.Copy SPSRback to CPSR, this will automatically changes the mode back to the previous one. 3.Clear the interrupt disable flags (if they were set)

It is up to the system designer who can decide which HW peripheral can produce which interrupt.

But system designers have adopted a standard design for assigning interrupts:

SWI are used to call privileged OS routines.

IRQ are assigned to general purpose interrupts like periodic timers.

•FIQ is reserved for one single interrupt source that requires fast response time.

It is the interval of time from an external interrupt signal being raised to the first fetch of an instruction of the ISR of the raised interrupt signal.

System architects try to achieve two main goals:

- •To handle multiple interrupts simultaneously.

- •To minimize the interrupt latency.

And this can be done by 2 methods: •allow nested interrupt handling •give priorities to different interrupt sources

## (12) Enabling and disabling interrupts

This is done by modifying the CPSR, this is done using only 3 ARM instruction:

MRSTo read CPSRMSRTo store in CPSRBICBit clear instructionORROR instruction

Enabling an IRQ/FIQ Interrupt MRS r1, cpsr BIC r1, r1, #0x80/0x40 MSR cpsr\_c, r1

Disabling an IRQ/FIQ Interrupt MRS r1, cpsr ORR r1, r1, #0x80/0x40 MSR cpsr\_c, r1

Stacks are needed extensively for context switching between different modes when interrupts are raised.

The design of the exception stack depends on two factors: •OS Requirements.

•Target hardware.

A good stack design tries to avoid stack overflow because it cause instability in embedded systems.

# (14) Interrupt stack

Two design decisions need to be made for the stacks:

The location

•The size

Traditional memory layout

The benefit of this layout is that the vector table remains untouched if a stack overflow occured!!

# (15) Interrupt handling

Non-nested interrupt handling scheme

This is the simplest interrupt handler.

Interrupts are disabled until control is returned back to the interrupted task.

One interrupt can be served at a time.

Not suitable for complex embedded systems.

# (15) Nested interrupt handling

#### Nested interrupt handling scheme(1)

•Handling more than one interrupt at a time is possible by enabling interrupts before fully serving the current interrupt.

- •Latency is improved.

- •System is more complex.

- •No difference between interrupts by priorities, so normal interrupts can block critical interrupts.

# (16) Nested interrupt handling

•The handler tests a flag that is updated by the ISR

•Re enabling interrupts requires switching out of current interrupt mode to either SVC or system mode.

•Context switch involves emptying the IRQ stack into reserved blocks of memory on SVC stack called stack frames

associate a priority level with a particular interrupt source.

Handling prioritization can be done by means of software or hardware.

When an interrupt signal is raised, a fixed amount of comparisons is done.

So the interrupt latency is deterministic.

But this could be considered a disadvantage!!

There are some other schemes, which are actually modifications to the previous schemes as follows:

•"Re-entrant interrupt handler": re-enable interrupts earlier and support priorities, so the latency is reduced.

• "Prioritized standard interrupt handler": arranges priorities in a special way to reduce the time needed to decide on which interrupt will be handled.

• "Prioritized grouped interrupt handler": groups some interrupts into subset which has a priority level, this is good for large amount of interrupt sources.

Availability of different modes of operation in ARM helps in exception handling in a structured way.

Context switching is one of the main issues affecting interrupt latency, and this is resolved in ARM FIQ mode by increasing number of banked registers.

We can't decide on one interrupt handling scheme to be used as a standard in all systems, it depends on the nature of the system:

What type of interrupts are there? How many interrupts are there?

#### Exception entry and return sequence (1)

At exception entry, the processor saves **R0-R3**, **R12**, **LR**, **PC** and **PSR** on the stack.

Saving **PC** means that the address of the next instruction to be executed after return from the exception handler is saved on the stack.

LR is also <u>updated</u> with EXC\_RETURN and that when the EXC\_RETURN value is <u>loaded</u> to the PC, the exception return sequence begins.

$LR \leftarrow EXC\_RETURN \\ PC \leftarrow LR$

| R0  | a0 |    |

|-----|----|----|

| R1  | a1 |    |

| R2  | a2 |    |

| R3  | a3 |    |

| R4  | v1 |    |

| R5  | v2 |    |

| R6  | v3 |    |

| R7  | v4 |    |

| R8  | v5 |    |

| R9  | v6 | SB |

| R10 | v7 |    |

| R11 | v8 | FP |

| R12 |    | IP |

| R13 |    | SP |

| R14 |    | LR |

| R15 |    | PC |

|     |    |    |

### Exception entry and return sequence (2)

the EXC\_RETURN values are <u>special values</u> that are recognized by the <u>hardware</u> rather than proper <u>pc</u> values.

Loading an EXC\_RETURN value into the PC initiates the hardware sequence – the reverse of the interrupt sequence – the return sequence

That reverse sequence will then load the actual pc to resume at.

You <u>don't explicitly load</u> the various registers, that is all done <u>automatically</u> by the <u>return sequence</u>. **Return Sequence**

LR ← EXC\_RETURN PC ← LR

**Automatic Hardware Sequence**

- no explicit register loading

- only have to <u>change</u> the EXC\_RETURN value

#### Exception entry and return sequence (3)

Loading **PC** with the value of **LR** is <u>suffiient</u>.

LR <u>already</u> holds EXC\_RETURN, and you do not have to worry about which stack you need to use; the EXC\_RETURN in LR is pre-encoded with the correct value.

Normally you only have to <u>change</u> the EXC\_RETURN value when you're writing a context-switcher.

$LR \leftarrow EXC\_RETURN \\ PC \leftarrow LR$

#### Exception entry and return sequence (4)

The EXC\_RETURN is a nice feature of the Cortex architecture.

No need to have a RFI instruction (Return From Interrupt)

*no difference* in writing an interrupt-routine and a normal subroutine for a **Cortex-M** based microcontroller.

#### Exception entry and return sequence (5)

- 1. An interrupt is signalled; a pending-flag is set.

- 2. The interrupt is started, the registers xPSR, PC, LR, R12, R3-R0 are all pushed onto the interrupt-stack.

- 3. The processor state is changed to use the interrupt-state.

- 4. The LR is loaded with the EXC\_RETURN value (which is one of these: 0xFFFFFF1, 0xFFFFFF9, 0xFFFFFFD, 0xFFFFFE1, 0xFFFFFE9 or 0xFFFFFED).

- 5. The PC is loaded with the address from the interrupt-vector.

- 6. Your Interrupt Service Routine (ISR) is executed.

- 7. You make sure the LR register is saved/restored if it's changed.

- 8. You finish your Interrupt Service Routine by executing a **BX LR** instruction.

- The EXC\_RETURN value from the LR register is now moved into PC. The core now sees that this is a special return-address, so it restores the registers from the current stack.

- 10. When the registers are restored, the execution continues where it was interrupted.

#### Exception entry and return sequence (5)

- 2. The interrupt is started, the registers xPSR, PC, LR, R12, R3-R0 are all pushed onto the interrupt-stack.

- 9. The EXC\_RETURN value from the LR register is now moved into PC. The core now sees that this is a special return-address, so it restores the registers from the current stack.

Interrupt code typically uses stacks. And there is a <u>separate</u> R13 for each mode (except one). So there is a <u>separate</u> stack per mode and at machine startup, it needs to be <u>initialized</u>.

- Initialization via a MSR (move into status register) instruction to change mode.

- Then store a value to (that) SP.

- Then use a **MSR** to put mode back

http://www2.unb.ca/~owen/courses/2253-2017/slides/08-interrupts.pdf

#### Exception entry and return sequence (5)

Mrs. MRS

MSR moves to a status register.

Status registers are CPSR, SPSR

Underscores after (eg CPSR\_cf) indicate

which sub-parts of the status register are affected.

Used in book code but not described... \_cxsf is all of it?.

MRS moves a status register into a regular register.

### Exception entry and return sequence (6)

the hardware entry and return sequence allows the processor <u>not</u> actually to do the return sequence if there is a **pending interrupt**

Instead, it immediately <u>start</u> <u>handling the new interrupt</u> <u>without having to load</u> the registers on return and then <u>store</u> them again before entering the new interrupt handler.

Exception Return

## Exception entry and return sequence (7)

If an exception is still in pending state when another exception handler has been completed,

instead of returning to the interrupted program and then entering the exception sequence again,

a **tail-chain** scenario will occur, where the processor will <u>not have to</u> <u>restore</u> all register values from the stack and push them back to the stack again.

The tail-chaining of exceptions allows <u>lower</u> exception processing <u>overhead</u> and <u>better energy efficiency</u>.

Exception Return

https://stackoverflow.com/questions/13029201/tail-chaining-of-interrupts

### Exception entry and return sequence (8)

it's possible that another interrupt will be handled by tail-chaining.

This may occur between step 8 and step 9.

- 8. You finish your Interrupt Service Routine by executing a **BX LR** instruction.

- The EXC\_RETURN value from the LR register is now moved into PC. The core now sees that this is a special return-address, so it restores the registers from the current stack.

the registers **R0-R3** and **R12** will <u>not</u> contain values <u>identical</u> to what is on the stack on <u>interrupt entry</u>.

In fact, you can <u>never trust</u> what's in **R0-R3** and **R12**, so if you need those values for instance if you're using SVC, or if you're making some debug-facility, then <u>fetch</u> them from the stack.

**R0 a0 R1 a1 R2** a2 **R3 a3** R4 R5 R6 R7 R8 R9 R10 R11 **R12** IP **R14** LR **R15** PC

#### Exception entry and return sequence (9)

That makes sense given the wonderful features such as Tail chaining or pop pre-emption.

As the **AAPCS** calls for, **R0-R3** can be used as input parameters/arguments to the function being called, but it is rather <u>safer</u> that the function/subroutine should <u>fetch</u> the values <u>from stack</u> instead of directly referring to.

It is seemed that the handler would not know under which circumstances it is executing either because of tail chaining or it entering the handler from the thread mode.

If the handler is entered from thread mode executing normal user program, then the **R0-R3** will be having <u>correct value</u> but if it is something like tail chaining, those may <u>not</u> be <u>correct</u>.

#### References

- [1] http://wiki.osdev.org/ARM\_RaspberryPi\_Tutorial\_C

- [2] http://blog.bobuhiro11.net/2014/01-13-baremetal.html

- [3] http://www.valvers.com/open-software/raspberry-pi/

- [4] https://www.cl.cam.ac.uk/projects/raspberrypi/tutorials/os/downloads.html