Copyright (c) 2011-2013 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

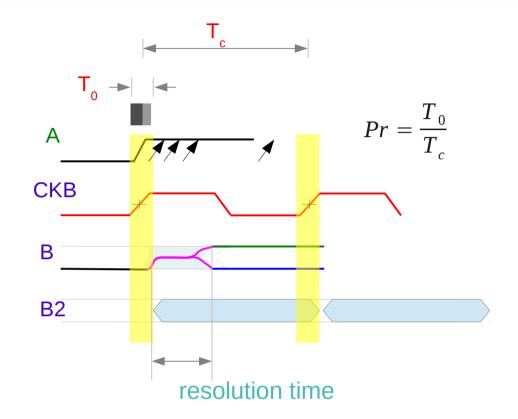

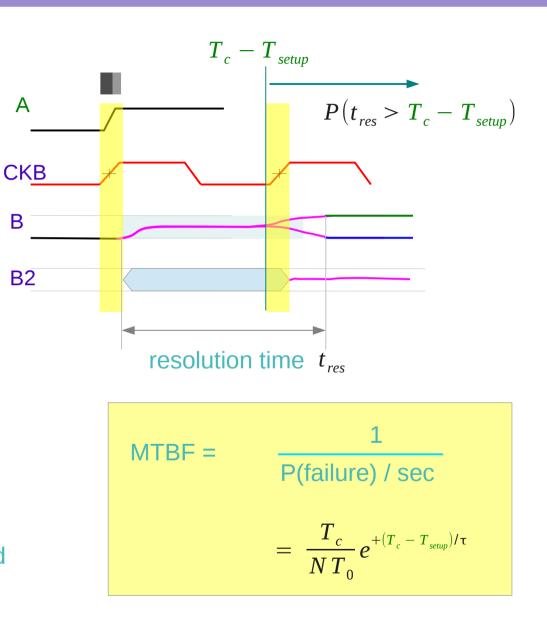

### **Resolution Time**

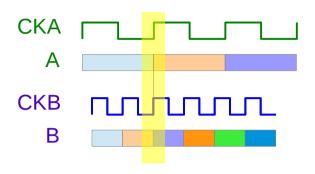

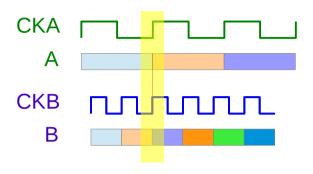

unrelated clock domain

$$P(t_{res} > t) = \frac{T_0}{T_c} e^{-t/\tau}$$

τ time constant depending on a specific flip flop implementation

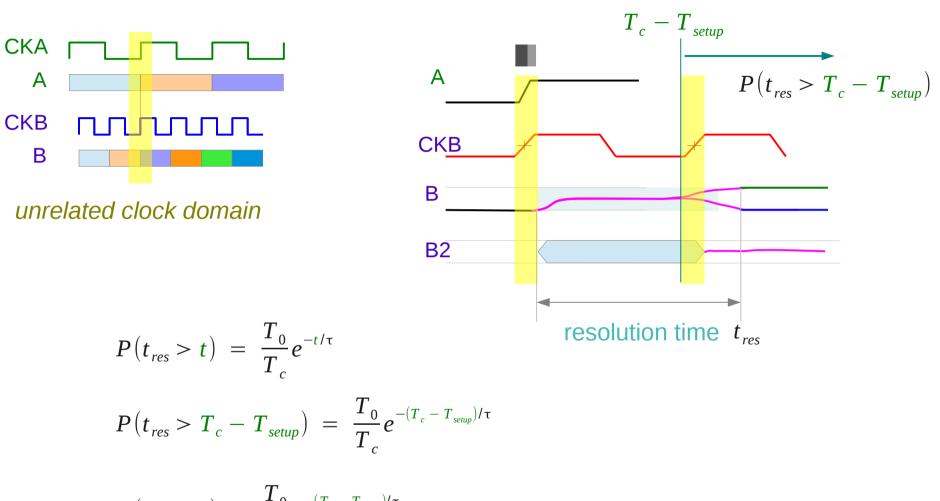

## P(failure)

$$P(failure) = \frac{T_0}{T_c} e^{-(T_c - T_{setup})/\tau}$$

### Mean Time Between Failures

unrelated clock domain

$$P(t_{res} > t) = \frac{T_0}{T_c} e^{-t/\tau}$$

$$P(t_{res} > T_c - T_{setup}) = \frac{T_0}{T_c} e^{-(T_c - T_{setup})/\tau}$$

$$P(failure) = \frac{T_0}{T_c} e^{-(T_c - T_{setup})/\tau}$$

input A changes N times per second

#### **Resolution Time**

#### References

[1] http://en.wikipedia.org/

[2] M. M. Mano, C. R. Kime, "Logic and Computer Design Fundamentals", 4<sup>th</sup> ed.

[3] J. Stephenson, Understanding Metastability in FPGAs. Altera Corporation white paper. July 2009.