## CMOS Delay-4 (H.4) Inverter Chain

20160927

Copyright (c) 2015 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

| References                                                                         |

|------------------------------------------------------------------------------------|

|                                                                                    |

|                                                                                    |

| Some Figures from the following sites                                              |

|                                                                                    |

| [1] http://pages.hmc.edu/harris/cmosvlsi/4e/index.html<br>Weste & Harris Book Site |

| [2] en.wikipedia.org                                                               |

| [2] critwin pediatory                                                              |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

|                                                                                    |

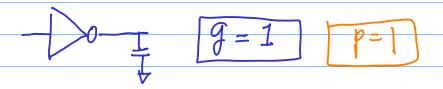

#### **Inverter Delay**

## Normalized Delay

$$d = (p + g \cdot k) = (p + k)$$

$$= \frac{dabs}{Zref}$$

## Absolute Delay

### Inverter Delay

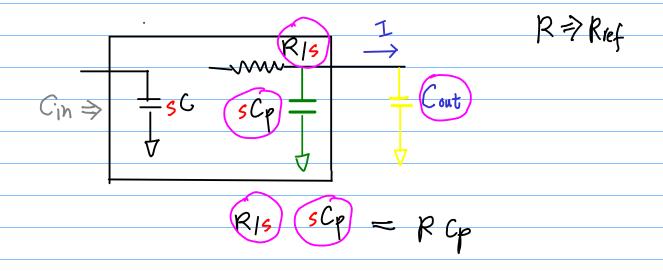

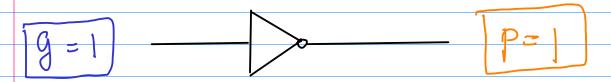

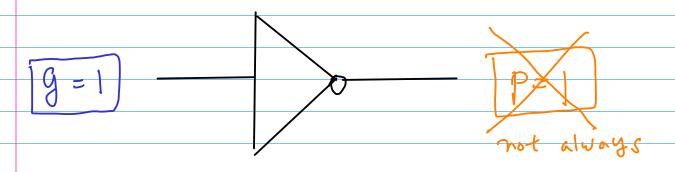

$$g = 1$$

#### Absolute Delay

#### Normalized Delay

$$d = \frac{dabs}{c} = (p + h)$$

#### 7 reference time constant

$$R$$

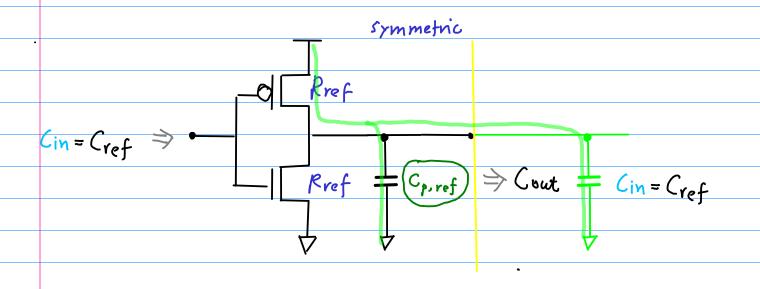

: Electrical Effort  $\left(\frac{C_{out}}{C_{in}}\right) \leftarrow C_{out}$

$$R:$$

Electrical Effort  $\left(\frac{C_{out}}{C_{in}}\right) \leftarrow C_{out}$

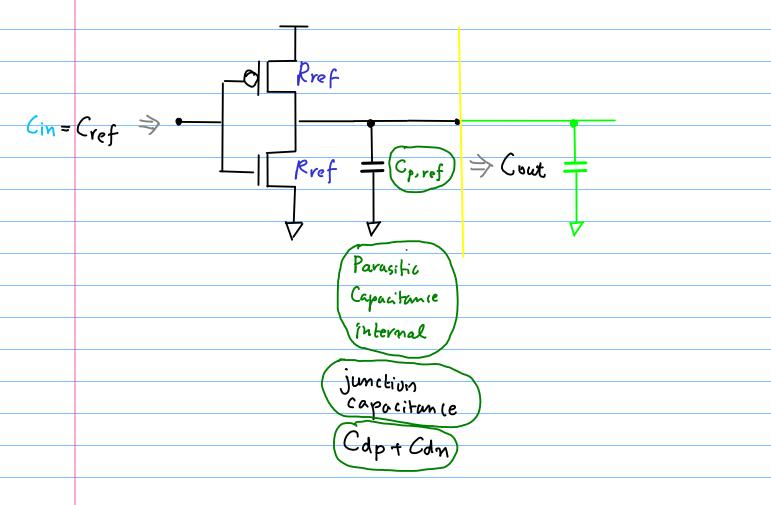

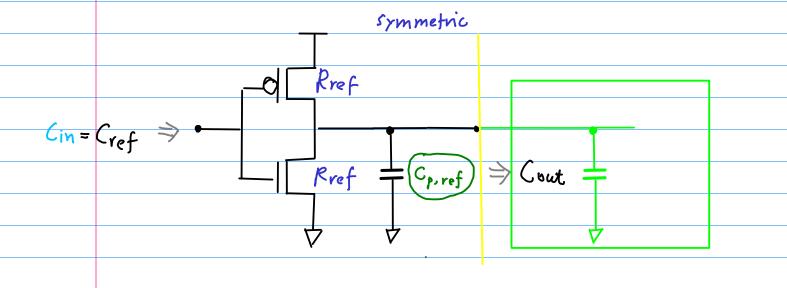

P: Parasitic Delay  $\left(\frac{C_{p,ref}}{C_{ref}}\right) \leftarrow C_{p,ref}$

# parasitic delay (p)

- delay due to internal parasitic capacitance

- 5Cp

- excluding external load cap Cout

- count only diffusion capacitance of the output

- delay without output load

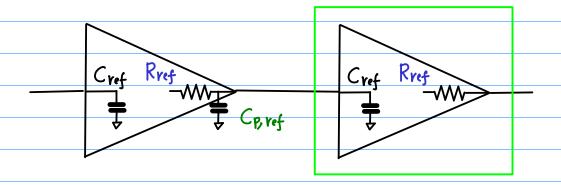

Pref (Cdp+Cdn) drain parasitic cap

Cref Cin of the ref inventer

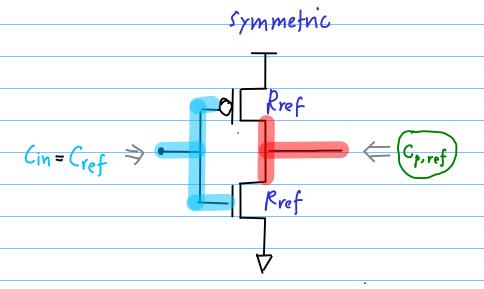

(Symmetric Inventer)

P =

$$\frac{Cp, ref}{Cref}$$

=  $\frac{internal diffusion cap}{gate cap of ref inv}$

=  $\frac{Zpan}{Cref}$  =  $\frac{Rref \cdot Cp, ref}{Rref \cdot Cref}$

Con of a reference inventer

Commetric inventer

Con of a reference inventer

Commetric inventer

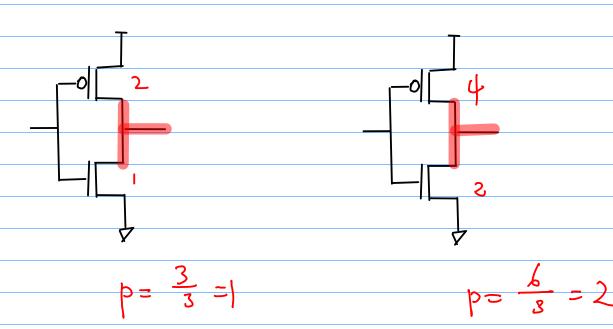

$$p = \frac{1}{3} \left( \sum_{i=1}^{n} \text{Output Scaling factors} \right)$$

$$p = \frac{1}{3} \left( \sum_{i=1}^{n} \text{Output Scaling factors} \right)$$

$$p = \frac{1}{3} = 1$$

$$p = \frac{1}{3} = 2$$

## reference inverter

## scaled inventers

For the ref inventer

$$dabs = Z_{ref}(h+1)$$

$$d = \frac{dabs}{Z_{ref}} = (h+1)$$

# absolute delay

$$R = k \cdot Rref \cdot (Cp, vef + Cout)$$

$$k = ln(q) = 2.2$$

#### Symmetric Inventer

to get the same current, need bigger inverter

$$7 = kR_{ref}C_{ref}$$

reference time const.

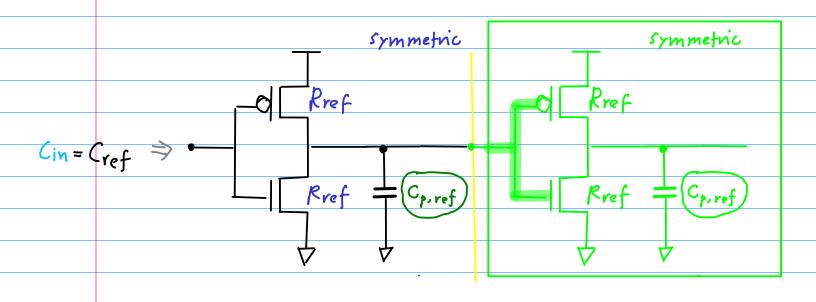

## Scaling Factor \$ >1

$$R = \frac{R \operatorname{ref}}{S}$$

$$Cp = S \cdot Cp, \operatorname{ref}$$

$$C_{in} = S \cdot C_{p,ref}$$

$$C_{in} = S \cdot C_{ref}$$

$$dabs = k \text{ Kref } (Cp, vef + Cout)$$

$$after scaling \implies k \frac{Rref}{S} (S \cdot Cp, ref + Cout)$$

$$= k Rref \cdot Cp, ref + k \frac{Rref}{S} \cdot Cout$$

$$= k Rref \cdot Cp, ref + k \frac{Rref}{S} \cdot \left(\frac{Cout}{Cvef}\right) \cdot Cvef$$

$$= k Rref \cdot Cp, ref + k Rref \cdot \left(\frac{Cout}{Cin}\right) \cdot Cvef$$

$$= k Rref \cdot Cvef \cdot \left(\frac{Cp, ref}{Cvef}\right) + k Rref \cdot Cvef \cdot \left(\frac{Cout}{Cin}\right)$$

dabs =

$$k Rref Cvef \left( \frac{Cp, ref}{Cvef} \right) + k Rref Cvef \left( \frac{Cout}{Cin} \right)$$

=  $k Rref Cvef \left( \frac{kRref}{Cvef} \right) + \left( \frac{Cout}{Cin} \right) \right]$

=  $7 \left( \frac{cpas}{c} \right) + \left( \frac{cout}{cin} \right) \right]$

=  $7 \left( \frac{cpas}{c} \right) + \left( \frac{cout}{cin} \right) \right]$

=  $7 \left( \frac{cpas}{c} \right) + \left( \frac{cout}{cin} \right) \right]$

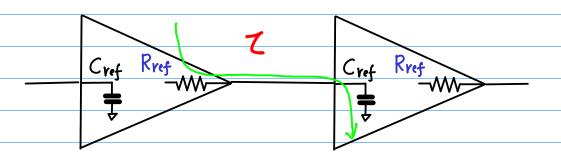

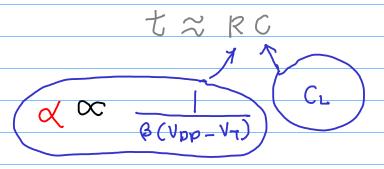

$$7 = k R_{ref} C_{ref}$$

reference time const.

7= KRRFCref

reference time const.

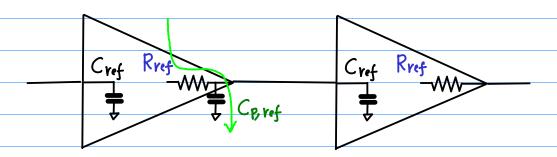

7 per= k Rref Cp. ref

parastic time const

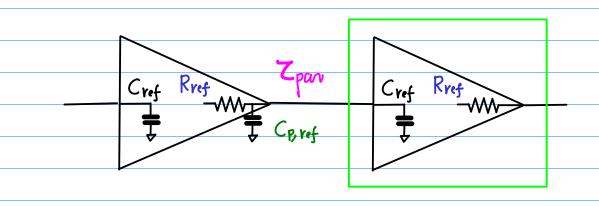

7: reference time const. 7= k Rref Cref

Zpa: parasitic time const. Zpan= k Rref Cp, ref

junction Parasific capacitan le Capacitance Cdp + Cdn Internal

### Electrical Effort

$$h = \frac{C_{out}}{C_{in}}$$

### Panasitic Delay

p =

$$\frac{7pa}{7}$$

=  $\frac{k Rref}{k Rref} \frac{Cp, ref}{Cvef}$  =  $\frac{Cp, ref}{Cvef}$

$$p = \frac{2pa}{2} = \frac{k \operatorname{Ref} C_{p, ref}}{k \operatorname{Ref} C_{vef}} = \frac{C_{p, ref}}{C_{vef}}$$

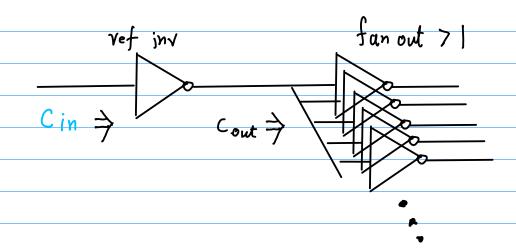

$$f_{i} \times \operatorname{d} f_{o} \times \operatorname{d} n \text{ inverter}$$

$$h = \frac{C_{out}}{C_{in}}$$

B: Device Transconductance Parameter

k: Process Transconductance Parameter

M: Electron/Hole Mobility

PMOS

$$\beta_{P} = k'_{P} \left(\frac{\omega}{L}\right)_{P}$$

$k'_{P} = \mu_{P} C_{OX}$   $C_{OX} = \frac{\varepsilon_{OX}}{t_{OX}}$

$n MOS$   $\beta_{n} = k'_{n} \left(\frac{\omega}{L}\right)_{n}$   $k'_{n} = \mu_{n} C_{OX}$   $C_{OX} = \frac{\varepsilon_{OX}}{t_{OX}}$

Saturation Current

$$I_{d_P} = \frac{\rho_P}{2} \left( V_{GSR} - |V_{TP}| \right)^2 \qquad V_{TP} < 0$$

$$I_{dn} = \frac{\rho_n}{2} \left( V_{GSn} - V_{Tn} \right)^2 \qquad V_{Tn} > 0$$

$$\frac{\beta_{n}}{\beta_{p}} = \frac{k'_{n} \left(\frac{\omega}{L}\right)_{n}}{k'_{p} \left(\frac{\omega}{L}\right)_{p}}$$

$$\frac{k'_n}{k'_p} = 2 \sim 3$$

$$\frac{k'_n}{k'_p} = \frac{\mu_n}{\mu_p} = r$$

$$\left(\frac{W}{L}\right)_{p} = Y\left(\frac{W}{L}\right)_{n}$$

$$\gamma = \frac{\mu_n}{\mu_p} = \frac{k_n}{k_p} > 1$$

$$\begin{cases} V_{\text{out}}(t) = V_{\text{pv}}(1 - e^{-t/z}) \\ V_{\text{out}}(t) = V_{\text{pv}}(1 - e^{-t/z}) \end{cases}$$

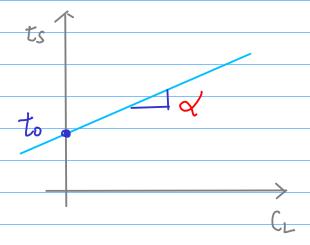

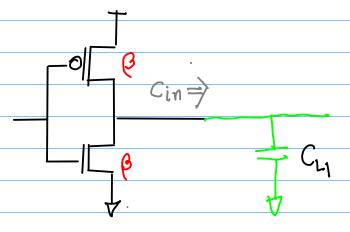

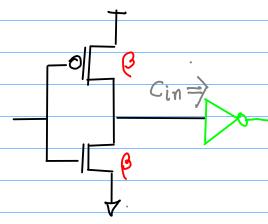

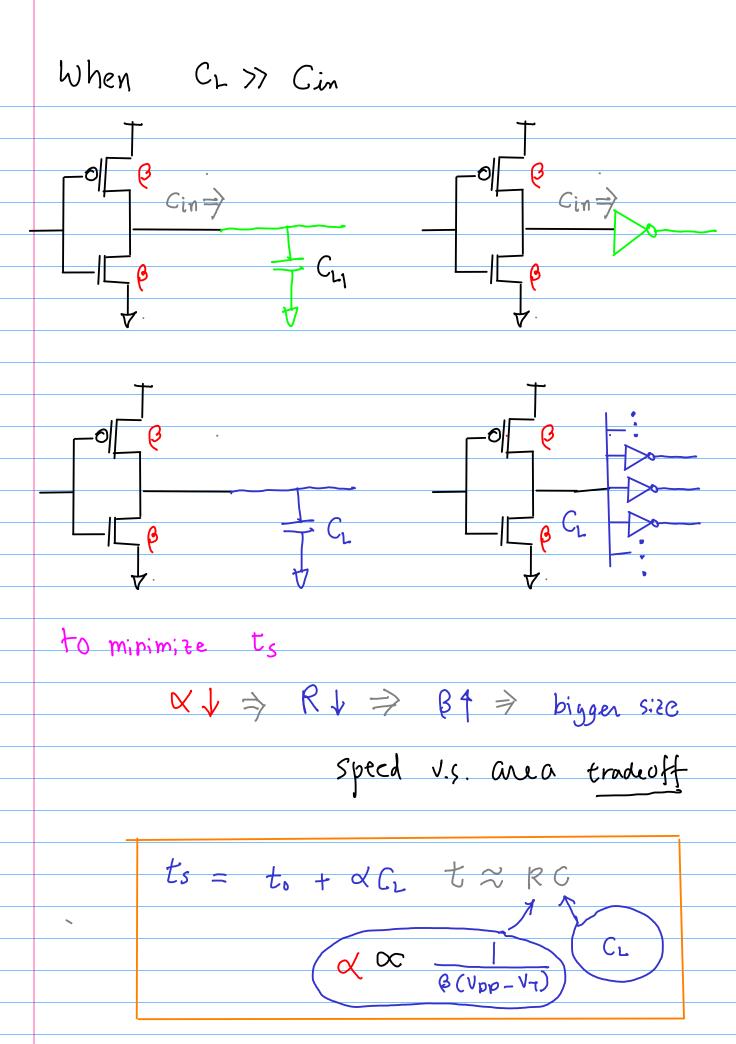

#### Generic Switching Delay

$$ts = t_0 + \alpha C_2 \Rightarrow t_s = t_r - t_f$$

#### Generic Switching Delay

to: zero delay

reference case

Generic Switching Delay of

$$ts_1 = t_0 + \alpha C_{in}$$

$$= t_0 + \alpha C_{in}$$

the channel length L assumed

$$Cin = Cox L (W_n + W_p)$$

$$= Cox L (W_n + Y_{w_p})$$

$$= Cox L W_n (1+Y)$$

$$= Con (1+Y)$$

to minimize ts

Speed V.s. area tradeoff

Scaling Factor S

$$R' = \frac{R}{s}$$

$$\alpha' = \alpha'$$

$$ts = t_0 + \frac{\alpha}{\beta} C_L$$

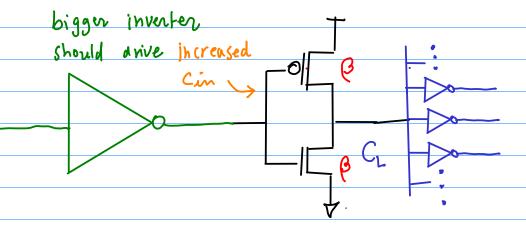

Compensation Factor (5

enables a NOT gate drive larger values of CL

If CL = 5 Cin (increased by the scaling factor \$)

then the switching time is the same

## Scaling Factor S

$$R' = SR$$

$$R' = R$$

$$X' = X$$

$$ts = t_0 + \frac{\alpha}{s} c_1$$

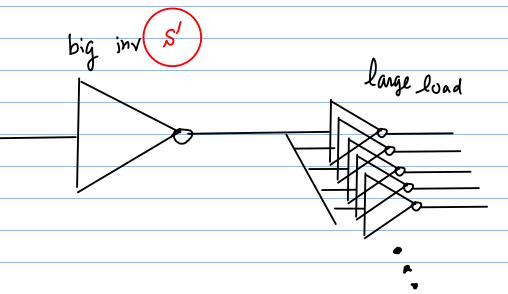

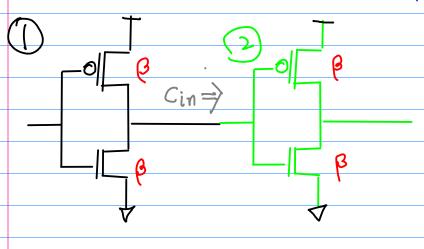

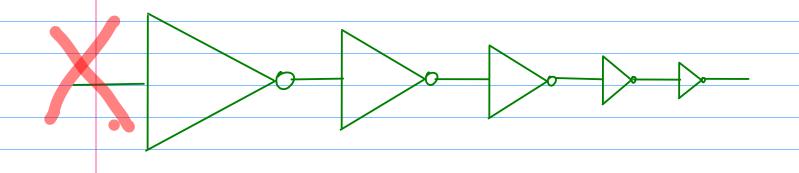

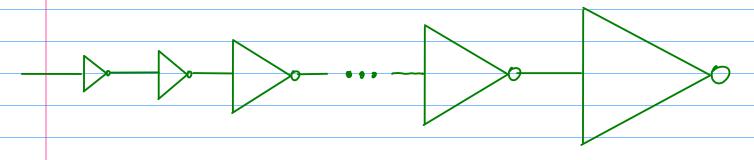

## Delay Minimization in an inverter cascade

$$\beta_2 = 5\beta_1$$

$$\beta_3 = 5\beta_2 = 5\beta_1$$

$$\beta_4 = 5\beta_3 = 5\beta_1$$

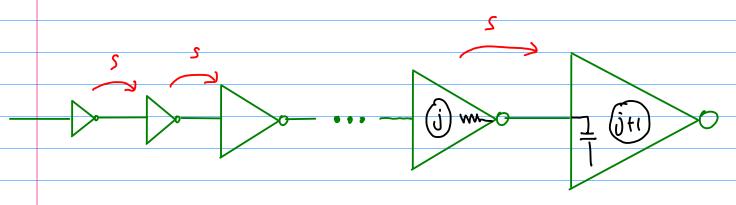

N-stage inverter Chain

$$= R_1 S C_1 + \frac{R_1}{S} S^2 C_1 + \frac{R_1}{S^2} S^3 C_1 + \cdots + \frac{R_1}{S^{n-1}} S^n C_1$$

Equalize the signal delay through each Stage

$$\ln (S^{N}) = \ln \left( \frac{C_{L}}{c_{I}} \right) = N \ln (S)$$

$$N = \frac{\ln\left(\frac{C_L}{C_1}\right)}{\ln\left(\frac{S}{S}\right)}$$

$$2d = N \stackrel{\circ}{S} 2r = Z_r ln\left(\frac{C_L}{C_1}\right) \left(\frac{S^1}{ln \stackrel{\circ}{S}}\right)$$

$$\frac{\partial \mathcal{U}}{\partial \mathcal{S}} = \frac{\partial}{\partial S} \left[ \frac{S}{\ln(S)} \right] = 0$$

$$\ln(s) = 1$$

$$\ln(s) - s \cdot \frac{1}{2} = 0$$

$$(\ln s)^{2}$$

$$N = \ln \left( \frac{c_i}{c_i} \right)$$

# \* Example

normalized

puth delay

$$D = Z$$

individual delays

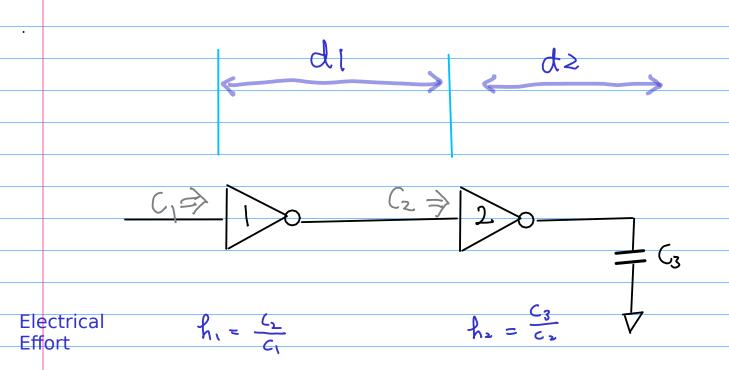

$$= d_1 + d_2$$

$$= (h_1 + p_1) + (h_2 + p_2)$$

$$= \left(\frac{C_2}{C_1} + p_1\right) + \left(\frac{C_3}{C_2} + p_2\right)$$

#### Path Electrical Effort

$$H = \frac{C_{last}}{C_{first}} = \frac{C_3}{G} = \left(\frac{C_2}{C_1}\right) \cdot \left(\frac{C_3}{C_2}\right) = h_1 h_2$$

Minimize path delay (h, h)

$$\frac{\partial D}{\partial h_1} = \frac{\partial}{\partial h_1} \left[ \left( \frac{h_1}{h_1} + \frac{h_2}{h_1} \right) + \left( \frac{h_1}{h_1} + \frac{h_2}{h_2} \right) \right] = 0$$

$$= \frac{H}{h_1^2} = 0$$

$$\frac{1}{h_1^2} (h_1^2 - h_1 h_2) = \frac{1}{h_1} (h_1 - h_2) = 0$$

When hi=hr , D (h, hz) has a minimum.

minimum delay by equalizing the delay through each stage T di = d L

$$\frac{h_1 + h_2 + h_3}{3} > \sqrt{h_1 h_2 h_3}$$

$$h_1 + h_2 + h_3$$

$\frac{1}{3}$   $\frac{1}{h_1 \cdot h_2 \cdot h_3} = 3 H^3$

arithmetic geometric average average

$$N = \ln\left(\frac{c_i}{c_i}\right)$$

$$N = \ln\left(\frac{c_i}{c_i}\right) = \ln\left(64\right) = 4.15 \Rightarrow N=4$$

$$2d = e \ln \left(\frac{C_i}{C_i}\right)^{2r} = e \ln (64) 2r$$

$(2r)^{p}$

$$(z_r)$$

?

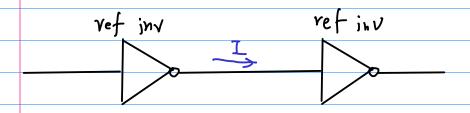

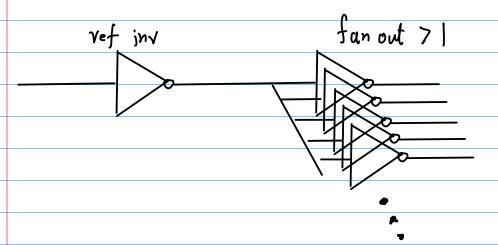

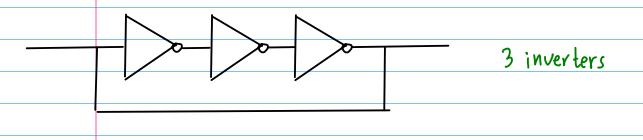

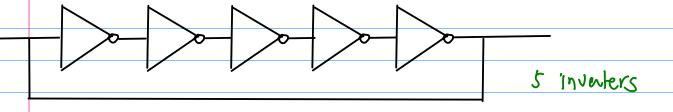

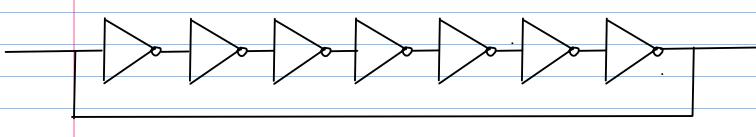

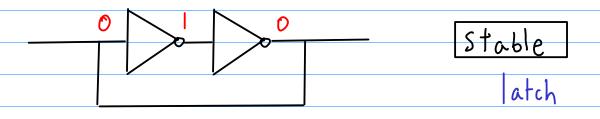

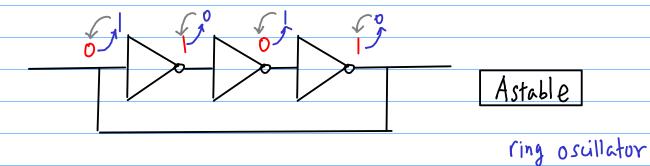

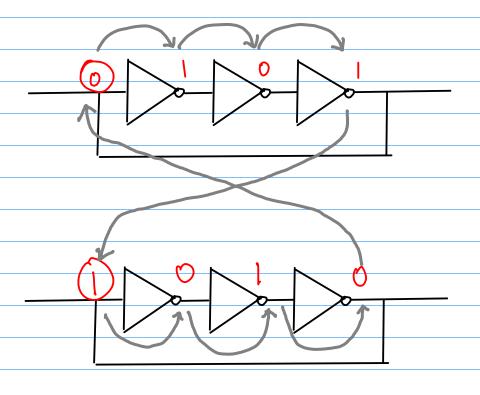

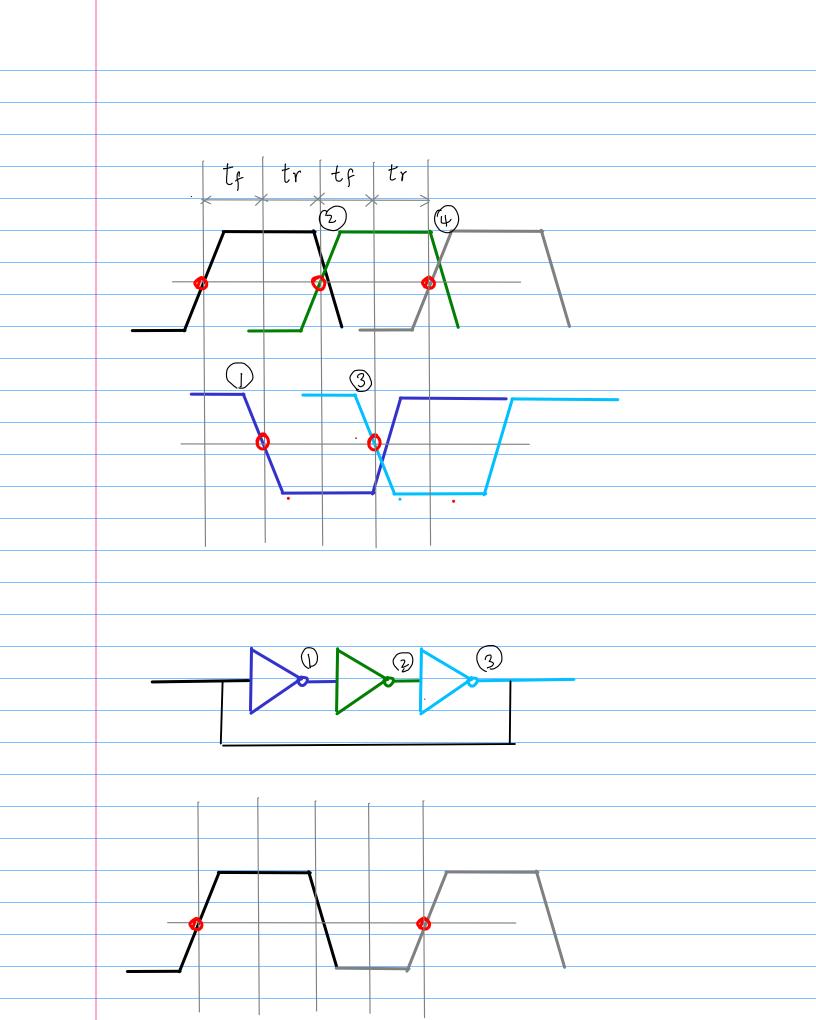

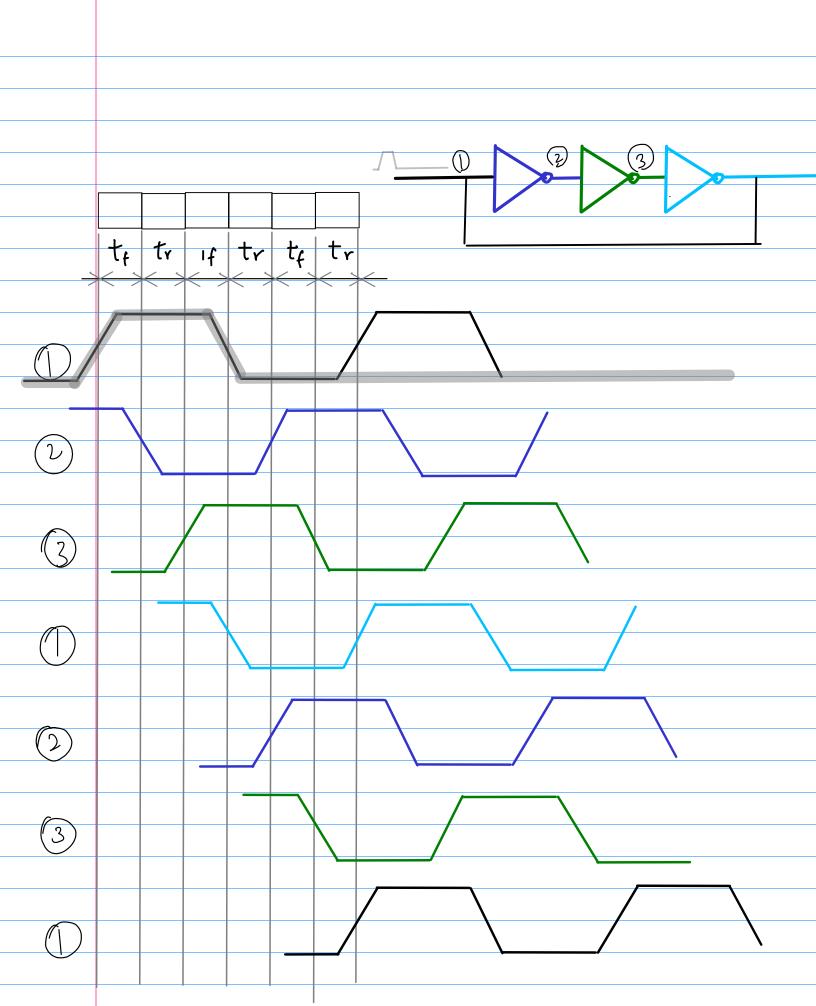

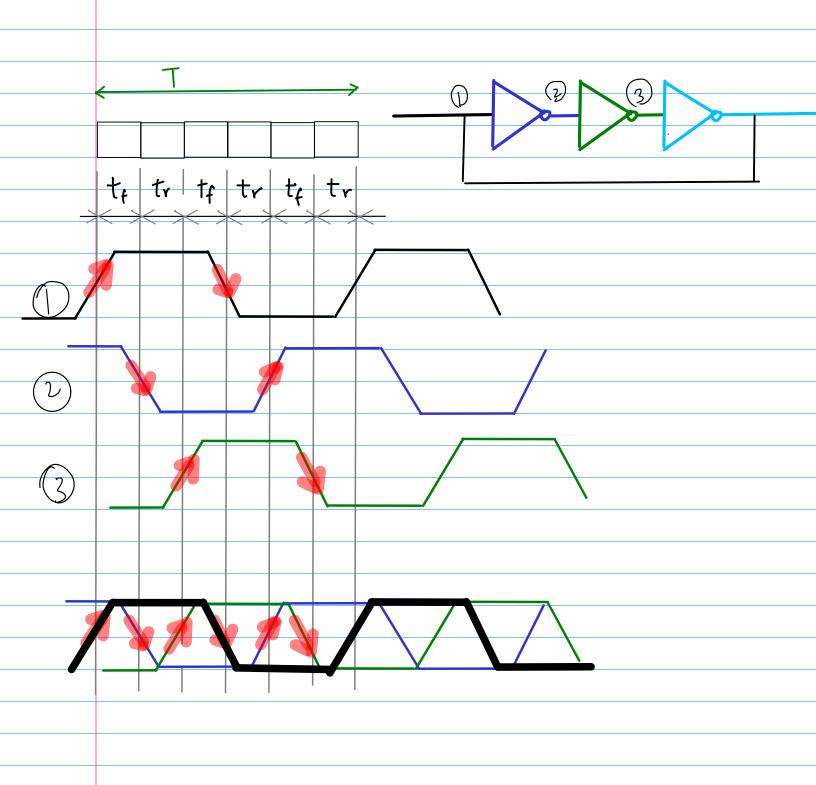

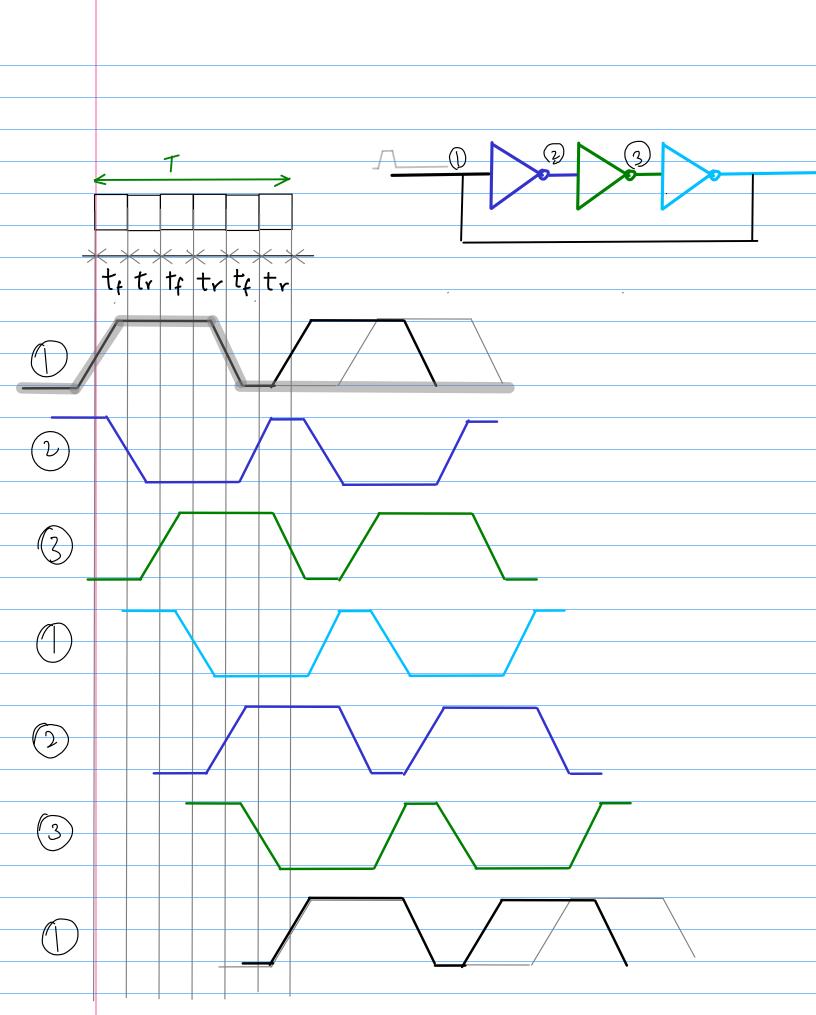

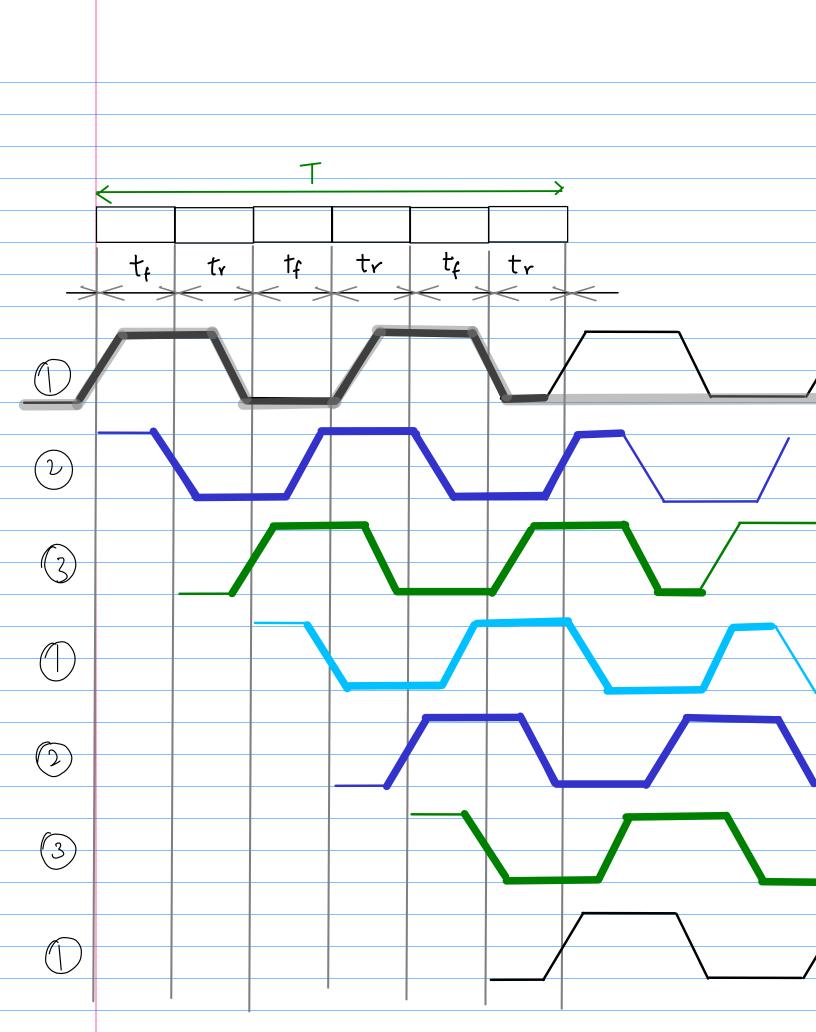

## Ring Oscillators

a uniform way of measuring  $t_p = \frac{t_{pr} + t_{pf}}{2}$

ring Oscillator

odd number of inverters

Connected in circular chain

## Odd Number of Inverters

1 inverters

Odd number of inverters

No Stable operating points -> Oscillating

ring oscillator

tp: propagation delay N: # of inverters in chain

T>> tf + tr

- used to measure

the average propagation delay

of a typical inverter

with minimum capacitive landing

$$t\rho = \frac{.T}{2.N}$$

Characterise a particular design/fabrication process

- used as a simple on chip clock

## N inventors (odd number)

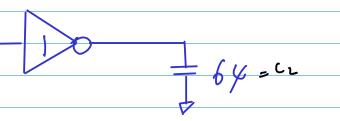

$$P = \left(\frac{C_{p, ref}}{C_{ref}}\right) = \left(\frac{\text{internal diffusion cap}}{\text{gate cap of ref inv}}\right) = \frac{3}{3} = 1$$

$$d = gh + P = 2$$

$$free_b = \frac{1}{2N \, das} = \frac{1}{4N \, T}$$