Copyright (c) 2011-2013 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

## Periodic Table

| Group →<br>↓ Period | ▶ 1      | 2        | 3        | 4         | 5         | 6                 | 7         | 8         | 9         | 10        | 11        | 12        | 13         | 14        | 15         | 16        | 17         | 18         |

|---------------------|----------|----------|----------|-----------|-----------|-------------------|-----------|-----------|-----------|-----------|-----------|-----------|------------|-----------|------------|-----------|------------|------------|

| 1                   | 1<br>H   |          |          |           |           | $\langle \rangle$ |           |           |           |           |           |           |            |           |            |           |            | 2<br>He    |

| 2                   | 3<br>Li  | 4<br>Be  |          | (         | В         |                   | Si        |           |           | P         |           |           | 5<br>B     | 6<br>C    | 7<br>N     | 8<br>O    | 9<br>F     | 10<br>Ne   |

| 3                   | 11<br>Na | 12<br>Mg |          |           |           |                   | -         |           |           |           |           |           | 13<br>Al   | 14<br>Si  | 15<br>P    | 16<br>S   | 17<br>Cl   | 18<br>Ar   |

| 4                   | 19<br>K  | 20<br>Ca | 21<br>Sc | 22<br>Ti  | 23<br>V   | 24<br>Cr          | 25<br>Mn  | 26<br>Fe  | 27<br>Co  | 28<br>Ni  | 29<br>Cu  | 30<br>Zn  | 31<br>Ga   | 32<br>Ge  | 33<br>As   | 34<br>Se  | 35<br>Br   | 36<br>Kr   |

| 5                   | 37<br>Rb | 38<br>Sr | 39<br>Y  | 40<br>Zr  | 41<br>Nb  | 42<br>Mo          | 43<br>Tc  | 44<br>Ru  | 45<br>Rh  | 46<br>Pd  | 47<br>Ag  | 48<br>Cd  | 49<br>In   | 50<br>Sn  | 51<br>Sb   | 52<br>Te  | 53<br>I    | 54<br>Xe   |

| 6                   | 55<br>Cs | 56<br>Ba |          | 72<br>Hf  | 73<br>Ta  | 74<br>W           | 75<br>Re  | 76<br>Os  | 77<br>Ir  | 78<br>Pt  | 79<br>Au  | 80<br>Hg  | 81<br>Tl   | 82<br>Pb  | 83<br>Bi   | 84<br>Po  | 85<br>At   | 86<br>Rn   |

| 7                   | 87<br>Fr | 88<br>Ra |          | 104<br>Rf | 105<br>Db | 106<br>Sg         | 107<br>Bh | 108<br>Hs | 109<br>Mt | 110<br>Ds | 111<br>Rg | 112<br>Cn | 113<br>Uut | 114<br>Fl | 115<br>Uup | 116<br>Lv | 117<br>Uus | 118<br>Uuo |

|                     |          |          |          |           |           |                   |           |           |           |           |           |           |            |           |            |           |            |            |

| Lanthanides         |          |          |          | 57<br>La  | 58<br>Ce  | 59<br>Pr          | 60<br>Nd  | 61<br>Pm  | 62<br>Sm  | 63<br>Eu  | 64<br>Gd  | 65<br>Tb  | 66<br>Dy   | 67<br>Ho  | 68<br>Er   | 69<br>Tm  | 70<br>Yb   | 71<br>Lu   |

| Actinides           |          |          |          | 89<br>Ac  | 90<br>Th  | 91<br>Pa          | 92<br>U   | 93<br>Np  | 94<br>Pu  | 95<br>Am  | 96<br>Cm  | 97<br>Bk  | 98<br>Cf   | 99<br>Es  | 100<br>Fm  | 101<br>Md | 102<br>No  | 103<br>Lr  |

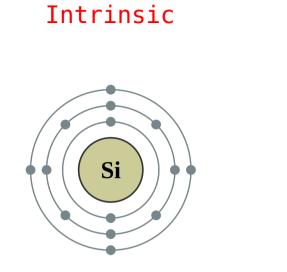

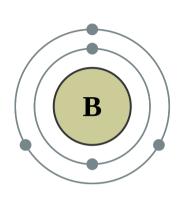

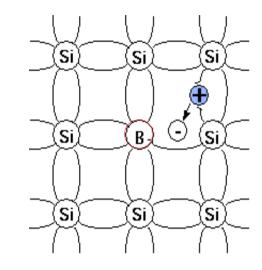

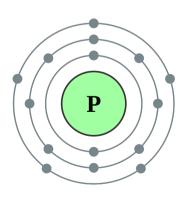

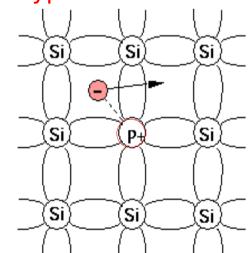

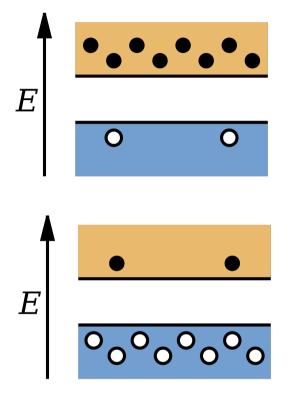

## Acceptor & Donor

Acceptor

p-type

Donor

n-type

Young Won Lim 4/30/13

## Polycrystal

Polycrystalline

Microscopically, a crystal has atoms in a near-perfect periodic arrangement;

a polycrystal is composed of many microscopic crystals (called "crystallites" or "grains");

Amorphous

an amorphous solid, such as glass, has no periodic arrangement even microscopically. A photo of electrical steel (coating removed) showing polycrystalline structure

### **Polycrystalline materials**

solids that are composed of many crystallites of varying size and orientation. The variation in direction can be random (called random texture) or directed, possibly due to growth and processing conditions. Fiber texture is an example of the latter.

### Polycrystalline

- composed of a number of smaller crystals or crystallites.

- a material consisting of multiple small silicon crystals.

- recognized by a visible grain, a "metal flake effect".

- semiconductor grade polycrystalline silicon  $\rightarrow$  single crystal silicon

- the randomly associated crystallites of silicon in "polycrystalline silicon" are converted to a large "single" crystal.

- poly is used both at the macro-scale and micro-scale (component) level.

### Single crystal silicon

- the crystalline framework is homogeneous

- recognized by an even external coloring

- the crystal lattice of the entire sample is continuous and unbroken with no grain boundaries.

- large single crystals are exceedingly rare in nature

- also difficult to produce in the laboratory.

- used to manufacture most Si-based microelectronic devices.

- as much as 99.9999% pure.

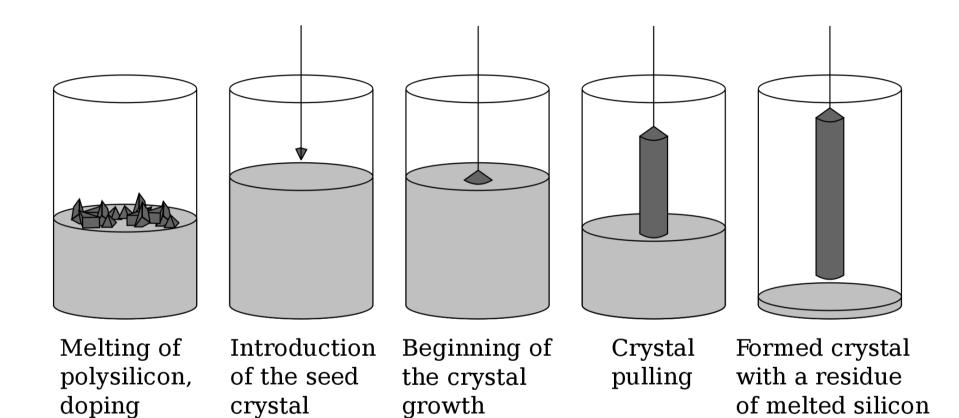

## Single Crystalline Silicon Formation

Wafers are formed of highly pure (99.9999999% purity), nearly defect-free single crystalline material.

### Czochralski growth

- invented by the Polish chemist Jan Czochralski.

- high purity monocrystalline semiconductor (silicon or germanium)

- a cylindrical ingot is formed by pulling a seed crystal from a 'melt'.

- impurity atoms in order to dope the crystal (n-type, p-type)

- The ingot is then sliced with a wafer saw (wire saw)

- and polished to form wafers.

- The size of wafers for photovoltaics is 100–200 mm square

- the thickness is 200–300  $\mu m$

- Electronics use wafer sizes from 100–300 mm diameter

Bridgman Growth Float Zone Growth

## Czochralski Growth

8

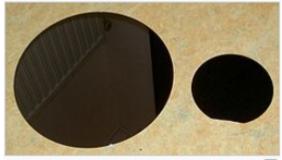

## Wafer Production

Ingot Growing

Shaping

Polishing

Cleansing

Polished 12" and 6" silicon wafers. The flat cut into the right wafer indicates its doping and crystallographic orientation (see below)

Silicon boule for the production of wafers

Crystal Growth and Wafer Slicing Process Step 1: Obtaining the Sand Step 2: Preparing the Molten Silicon Bath Step 3: Making the Ingot Step 4: Preparing the Wafers Thickness Sorting Lapping & Etching Processes Thickness Sorting and Flatness Checking Polishing Process Final Dimensional and Electrical Properties Qualification

Remove any cracked and damaged surface silicon on the surface

## **Types of Silicon Wafers**

### Bulk polished Silicon Wafer

### Epi Silicon Wafer

#### Silicon on Insulator Wafer

<u>Heavily doped</u> bulk wafers with <u>moderately</u> to <u>lightly doped</u> epitaxial silicon layer

Immunity to latch-up

increase performance Eliminate latch-up

silicon dioxide or sapphire

the Greek roots epi (above) and taxis (in ordered manner)--> "to arrange upon".

**Epitax**: the deposition of a crystalline overlayer on a crystalline substrate

**Epitaxial growth**: there must be one or more preferred orientations of the overlayer with respect to the substrate

the overlayer - an epitaxial film or epitaxial layer

Epitaxial films may be grown from gaseous or liquid precursors. VPE (Vapor Phase Epitaxy) LPE (Liquid Phase Epitaxy) SPE (Solid Phase Epitaxy)

If an epitaxial film is deposited on a substrate of the same composition, the process is called **homoepitaxy**; otherwise it is called **heteroepitaxy**.

## Wafer Fabrication (1)

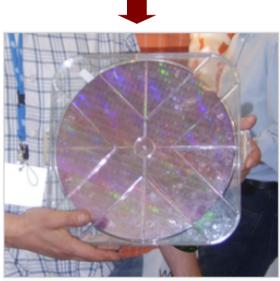

Polished 12" and 6" silicon wafers. The flat cut into the right wafer indicates its doping and crystallographic orientation (see below)

VLSI microcircuits fabricated on a 12-inch (300 mm) silicon wafer, before dicing and packaging

### Wafer production

#### Wafer fabrication

a procedure composed of many repeated sequential processes to produce complete electrical or photonic circuits.

electrical circuit specifications

circuit layout programs (computer aided design)

photomask production

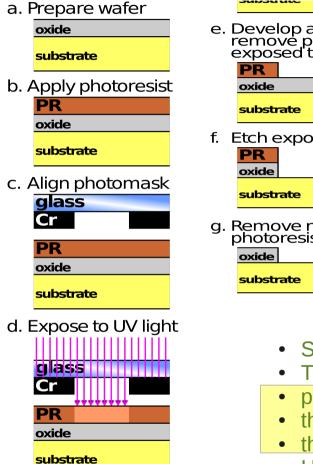

## Wafer Fabrication (2)

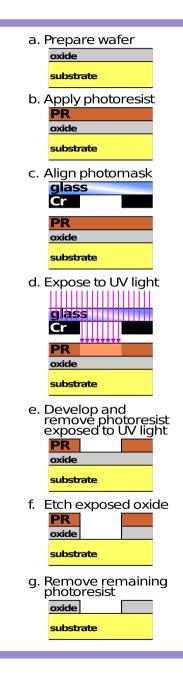

e. Develop and remove photoresist exposed to UV light

e. Develop and remove photoresist exposed to UV light f. Etch exposed oxide g. Remove remaining photoresist

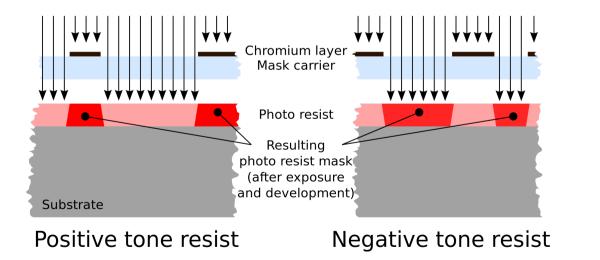

### Photolithography

- Apply oxide

- Photoresist application (PR)

- Exposure and developing (Cr + glass)

- **Etching Oxide**

- Photoresist removal

- Silicon wafers start out blank and pure.

- The circuits are built in layers.

- photo-sensitive resistance patterns are photo-masked

- then exposed to short-wave ultraviolet light

- the unexposed areas are thus etched away and cleaned.

- Hot chemical vapors are deposited on to the desired zones and baked

- the vapors are permeated into the desired zones.

- In some cases, ions, such as O2+ or O+, are implanted

These steps are often repeated many hundreds of times

## Wafer Fabrication (3)

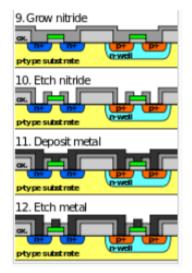

Simplified illustration of the process of fabrication of a CMOS inverter Each etch step is detailed in the previous slide

| 1. Grow field oxide           |

|-------------------------------|

| GK.                           |

| ptype substrate               |

| 2. Etch axide for pMOSFET     |

| ak.                           |

| ptype substrate               |

| 3. Diffuse n-well             |

| ak.                           |

| ptype substrate               |

| 4. Etch axidefor nMOSFET      |

| <b>a</b>                      |

| ptype substrate               |

| 5. Grow gate oxide            |

| ax.                           |

| ptype substrate               |

| 6. Deposit polysilic on       |

|                               |

| ptype substrate               |

| 7. Etch polysilicon and oxide |

| ax                            |

| ptype substrate               |

| 8. Implant sources and drains |

|                               |

| n+ n+ p+                      |

| ptype substrate               |

Oxidation Layering Photo lithography Etching Diffusion Thin Film

- Silicon wafers start out blank and pure.

- The circuits are built in layers.

- photo-sensitive resistance patterns are photo-masked

- then exposed to short-wave ultraviolet light

- the unexposed areas are thus etched away and cleaned.

- Hot chemical vapors are deposited on to the desired zones and baked

- the vapors are permeated into the desired zones.

- In some cases, ions, such as O2+ or O+, are implanted

## **Thermal Oxidation**

### $SiO_2$ :

### \* Insulator

\* A good diffusion mask

Very good etching selectivity

#### Thermal oxidation is a way to

- produces a thin layer of oxide (usually silicon dioxide) on the surface of a wafer : High Temperature Oxide layer (HTO)

- forces an oxidizing agent to diffuse into the wafer at high temperature and react with it.

- may use either water vapor (wet oxidation) or molecular oxygen (dry oxidation) as the oxidant

- performed in furnaces, at temperatures between 800 and 1200°C.

- a single furnace accepts many wafers at the same time

## Photolithography

- a process to pattern parts of a thin film or the bulk of a substrate

- uses light to transfer a geometric pattern from a photomask to a lightsensitive chemical "photoresist" on the substrate.

- either engraves the exposure pattern into, or enables deposition of a new material in the desired pattern upon, the material underneath the photo resist.

## Etching

used to chemically remove layers from the surface of a wafer part of the wafer is protected from the etchant by a "masking" material the masking material is a photoresist which has been patterned using photolithography. a more durable mask, such as silicon nitride

#### Wet etching

liquid-phase ("wet") etchants the wafer can be immersed in a bath of etchant buffered hydrofluoric acid (BHF)

#### Anisotropic wet etching

Orientation dependent etching Some wet etchants etch crystalline materials at very different rates depending upon which crystal face is exposed

#### **Plasma etching**

Modern VLSI processes avoid wet etching, and use plasma etching instead. Plasma etchers can operate in several modes by adjusting the parameters of the plasma.

## Doping

Extrinsic semiconductors with a larger electron concentration than hole concentration are known as n-type semiconductors. The phrase 'n-type' comes from the negative charge of the electron. In n-type semiconductors, electrons are the majority carriers and holes are the minority carriers. N-type semiconductors are created by doping an intrinsic semiconductor with donor impurities.

As opposed to n-type semiconductors, p-type semiconductors have a larger hole concentration than electron concentration. The phrase 'p-type' refers to the positive charge of the hole. In p-type semiconductors, holes are the majority carriers and electrons are the minority carriers. P-type semiconductors are created by doping an intrinsic semiconductor with acceptor impurities.

**Diffusion :** The spread of particles through random motion from regions of higher concentration to regions of lower concentration

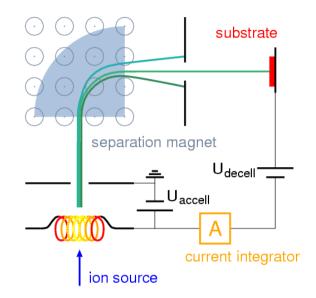

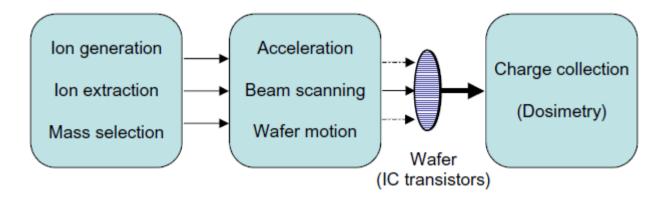

Ion implantation : Bombarding the substrate with ions accelerated to high velocities

## Diffusion

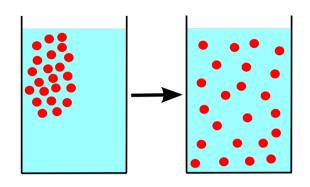

A diffusion process in science. Some particles are dissolved in a glass of water. Initially, the particles are all near one corner of the glass. If the particles all randomly move around ("diffuse") in the water, then the particles will eventually become distributed randomly and uniformly, and organized (but diffusion will still continue to occur, just that there will be no net flux).

**Predeposition** : to introduce the required dose of dopant into the substrate.

**Drive-In** : a subsequent drive-in anneal then redistributes the dopant giving the required junction depth and surface concentration.

## Ion Implantation

Ion implantation is a materials engineering process by which ions of a material are accelerated in an electrical field and impacted into a solid. This process is used to change the physical, chemical, or electrical properties of the solid.

## Thin Film Deposition

- **thin**: a layer of material ranging from fractions of a nanometer (monolayer) to several micrometers in thickness.

- the act of applying a thin film to a surface

- onto a substrate or onto previously deposited layers

- molecular beam epitaxy: a single layer of atoms

**Chemical deposition**

**Physical deposition**

## **Chemical Deposition**

- a fluid precursor undergoes a chemical change at a solid surface, leaving a solid layer.

- like the formation of soot on a cool object when it is placed inside a flame.

- deposition happens on every surface, with little regard to direction;

- tend to be conformal, rather than directional.

A **conformal** film defines a morphologically <u>uneven interface</u> with another body and has a thickness that is the same everywhere along the interface.

- Plating

- Chemical solution deposition (CSD) or Chemical bath deposition (CBD)

- Spin coating or spin casting

- Chemical vapor deposition (CVD)

- Plasma enhanced CVD (PECVD)

- Atomic layer deposition (ALD)

## **Physical Deposition**

- mechanical, electromechanical or thermodynamic means

- like the formation of frost

- most engineering materials are held together by relatively high energies

- chemical reactions are not used to store these energies

- require a low-pressure vapor environment to function properly

- most can be classified as physical vapor deposition (PVD).

- Thermal evaporator

- Electron beam evaporator

- Molecular beam epitaxy (MBE)

- Sputtering

- Pulsed laser deposition

- Cathodic arc deposition (arc-PVD)

- Electrohydrodynamic deposition (Electrospray deposition)

coating **metal** on the surface of non-metallic objects.

Plating relies on liquid precursors, often a solution of water with a salt of the metal to be deposited. Some plating processes are driven entirely by reagents in the solution (usually for noble metals), but by far the most commercially important process is electroplating.

Chemical vapor deposition (CVD) generally uses a gas-phase precursor, often a halide or hydride of the element to be deposited. In the case of MOCVD, an organometallic gas is used. Commercial techniques often use very low pressures of precursor gas.

**Physical vapor deposition (PVD)**. The material to be deposited is placed in an **energetic, entropic environment**, so that particles of material **escape** its surface. Facing this source is a **cooler surface** which draws energy from these particles as they arrive, allowing them to form a solid layer. The whole system is kept in a vacuum deposition chamber, to allow the particles to travel as freely as possible. Since particles tend to follow a straight path, films deposited by physical means are commonly **directional**, rather than **conformal**.

### Insulator: SiO2 Si2N4 SiON

**Plasma enhanced CVD (PECVD)** uses an ionized vapor, or plasma, as a precursor. Unlike the soot example above, commercial PECVD relies on electromagnetic means (electric current, microwave excitation), rather than a chemical reaction, to produce a plasma.

**Spin coating** or spin casting, uses a liquid precursor, or sol-gel precursor deposited onto a smooth, flat substrate which is subsequently spun at a high velocity to centrifugally spread the solution over the substrate. The speed at which the solution is spun and the viscosity of the sol determine the ultimate thickness of the deposited film. Repeated depositions can be carried out to increase the thickness of films as desired. Thermal treatment is often carried out in order to crystallize the amorphous spin coated film (orientations).

Atomic layer deposition (ALD) uses gaseous precursor to deposit conformal thin films one layer at a time. Two half reactions, run in sequence and repeated for each layer, in order to ensure total layer saturation. As a result of the stepwise, the process is slower than CVD, however it can be run at low temperatures, unlike CVD.

### Mask

### References

[1] http://en.wikipedia.org/