# Carry Skip Adder (5A)

- - •

Copyright (c) 2024 – 2013 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

https://en.wikipedia.org/wiki/AND\_gate https://en.wikipedia.org/wiki/OR\_gate https://en.wikipedia.org/wiki/XOR\_gate https://en.wikipedia.org/wiki/NAND\_gate

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

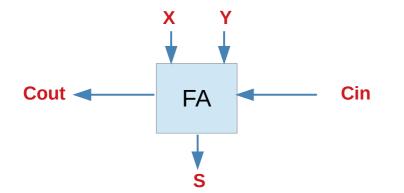

| Х | Y |   |                           |

|---|---|---|---------------------------|

| 0 | 0 | K | Kill (= <mark>PG</mark> ) |

| 0 | 1 | Р | Propagate                 |

| 1 | 0 | Р | Propagate                 |

| 1 | 1 | G | Generate                  |

https::/electronics.stackexchange.com/questions/21251/critical-path-for-carry-skip-adder

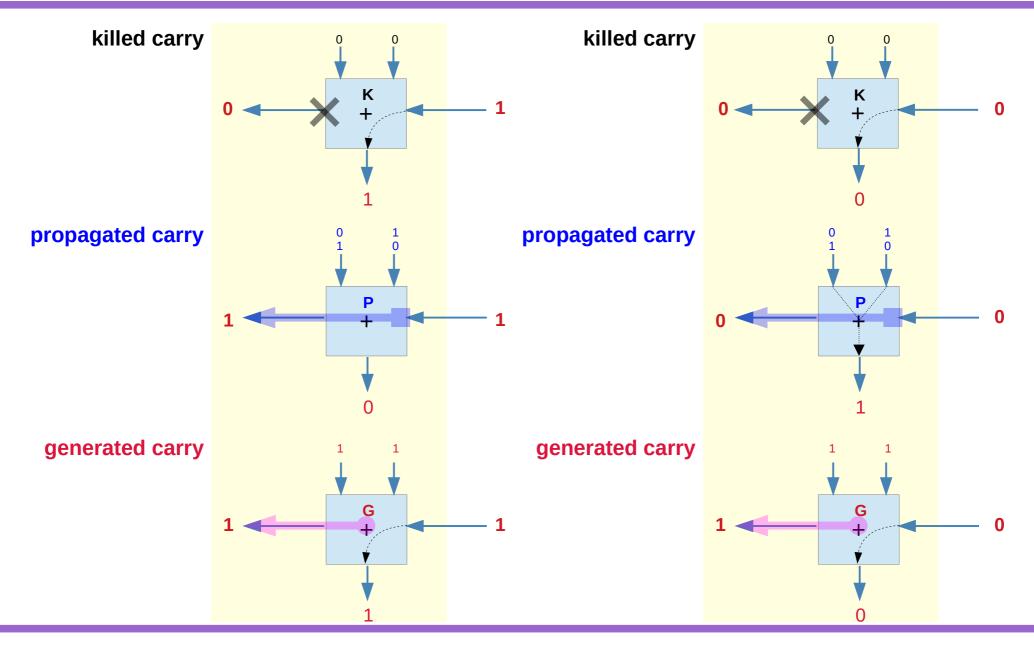

#### Carry Kill, Propagate, Generate conditions (2)

| Х | Y |   |                           |

|---|---|---|---------------------------|

| 0 | 0 | K | Kill (= <mark>PG</mark> ) |

| 0 | 1 | P | Propagate                 |

| 1 | 0 | P | Propagate                 |

| 1 | 1 | G | Generate                  |

Unless the two FA's are in propagate mode, the transition of Cin does <u>not</u> affect the transition of Cout

Critical path – all FA's in propagate mode

Broken paths for any FA in other mode - kill mode, generate mode

https::/electronics.stackexchange.com/questions/21251/critical-path-for-carry-skip-adder

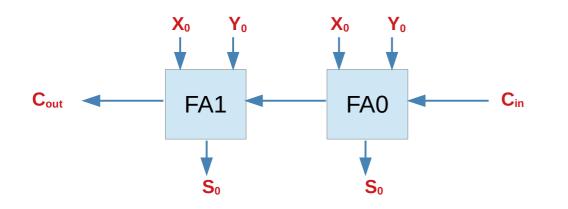

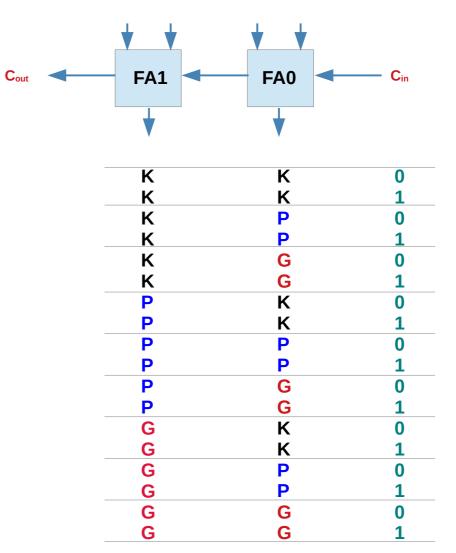

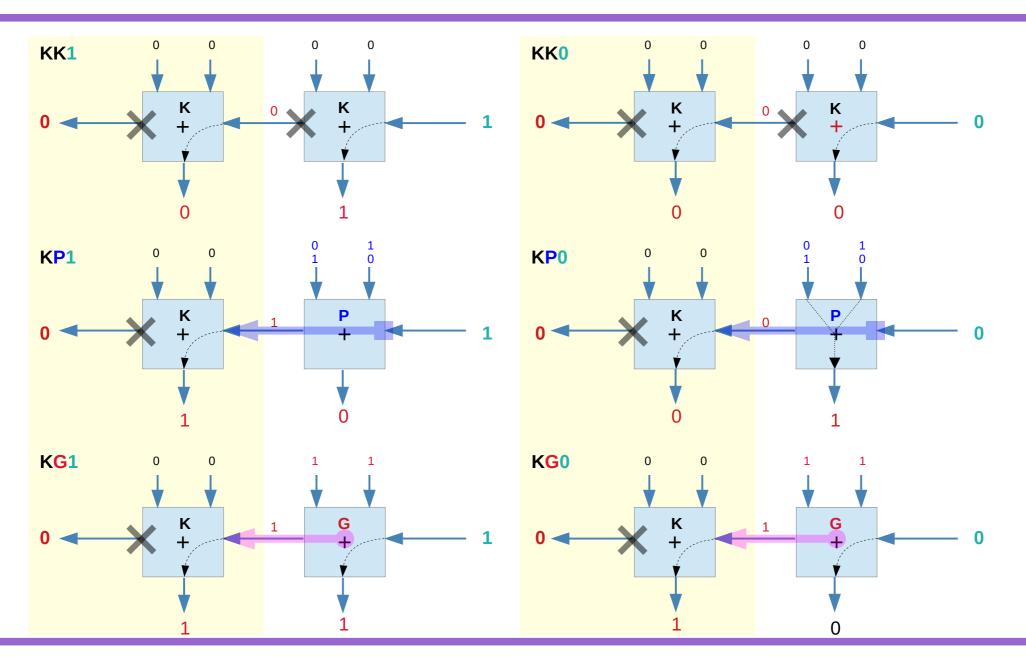

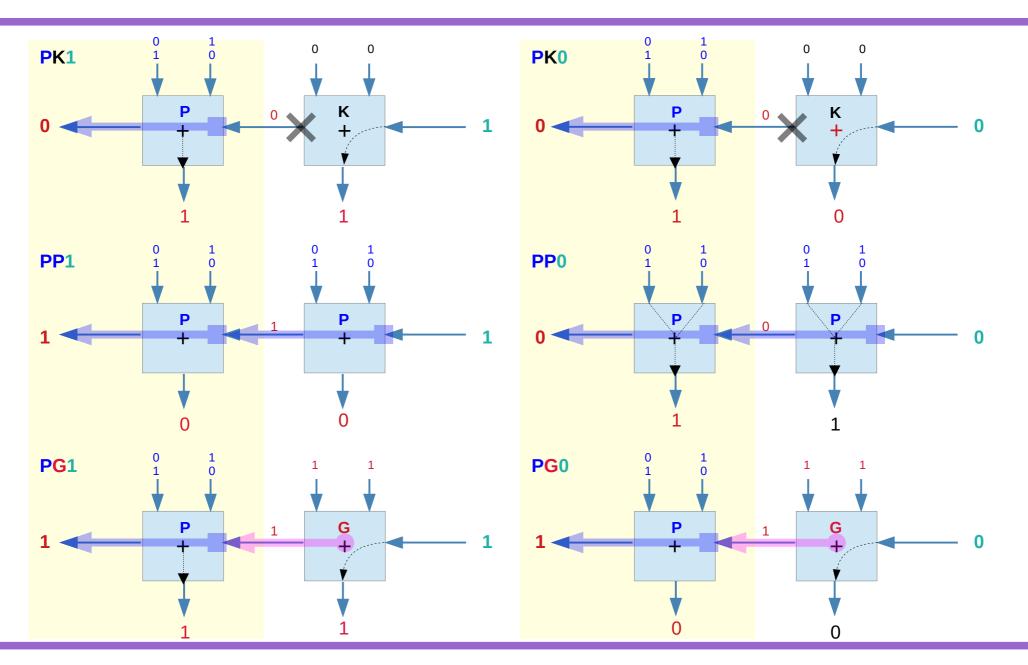

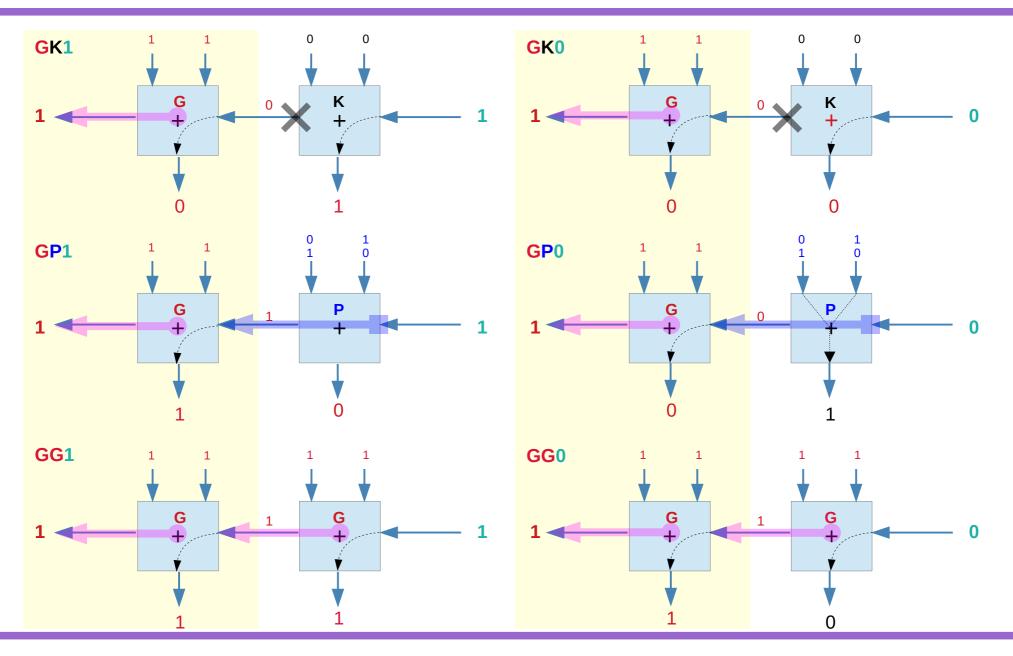

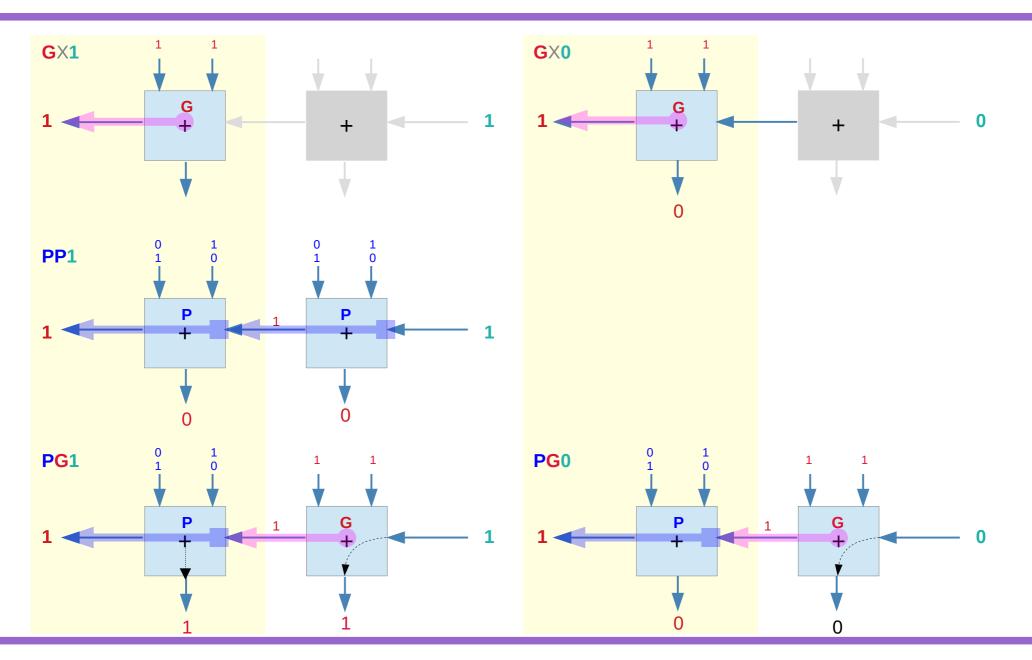

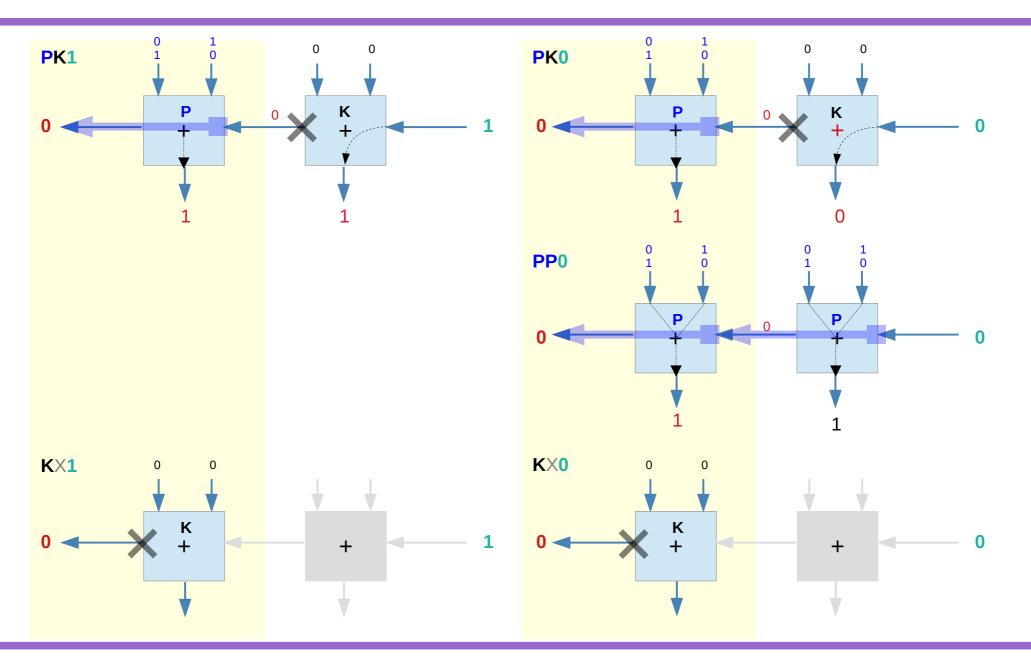

#### K, P, and G conditions in a 2-bit adder (2)

| Х | Y |   |                           |

|---|---|---|---------------------------|

| 0 | 0 | K | Kill (= <mark>PG</mark> ) |

| 0 | 1 | Р | Propagate                 |

| 1 | 0 | Р | Propagate                 |

| 1 | 1 | G | Generate                  |

#### 1. Cases when **FA1** is in the **K** mode

#### 2. Cases when **FA1** is in the **P** mode

#### 3. Cases when **FA1** is in the **G** mode

#### Cases for C<sub>out</sub> = 1

#### Cases for $C_{out} = 0$

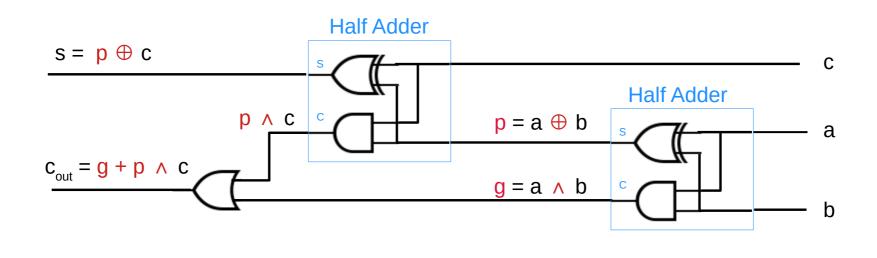

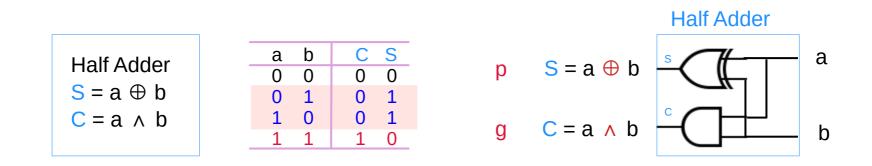

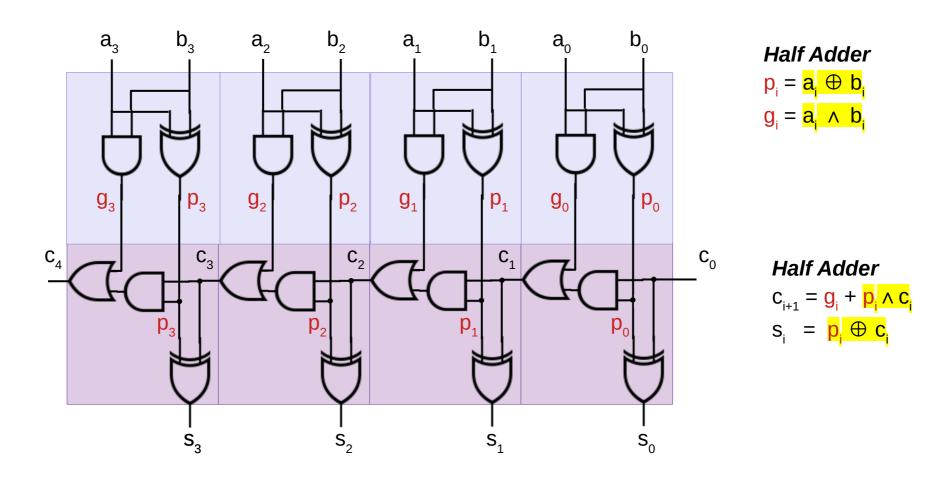

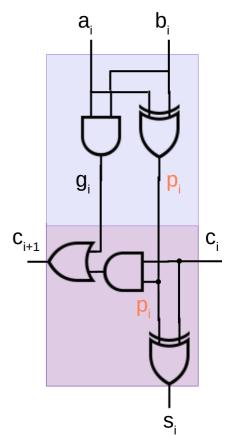

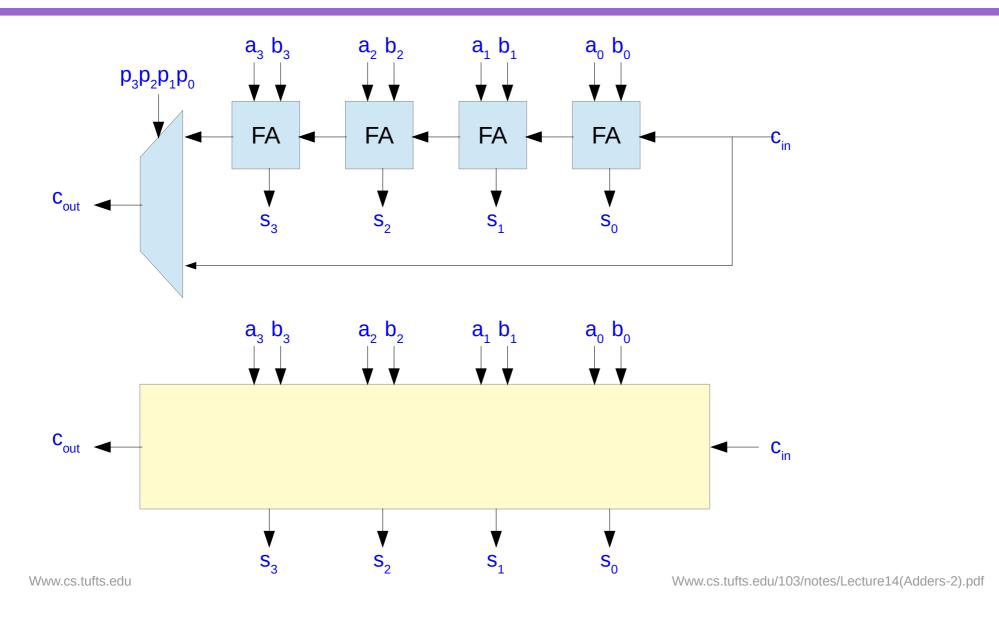

## FA with P & G

https://en.wikipedia.org/wiki/Carry-skip\_adder

Full adder with additional generate and propagate signals.

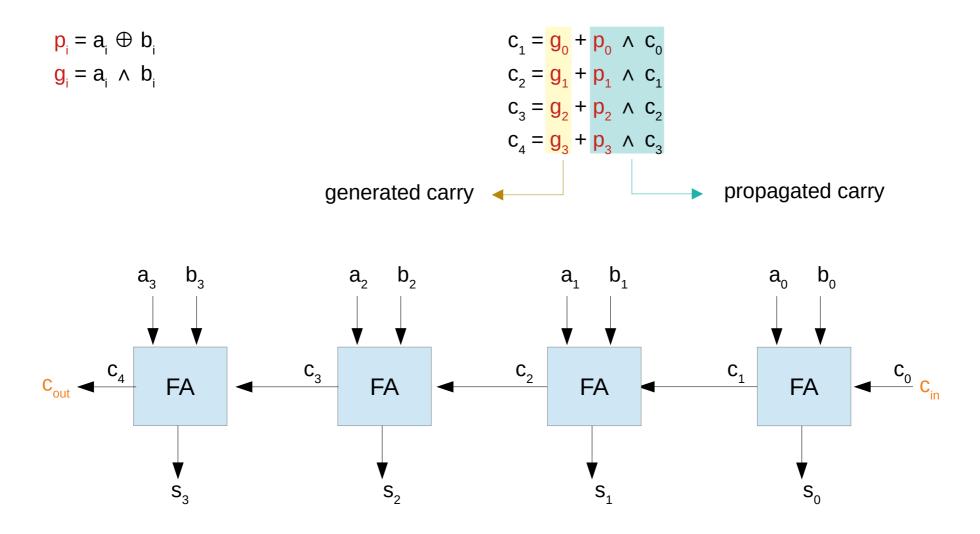

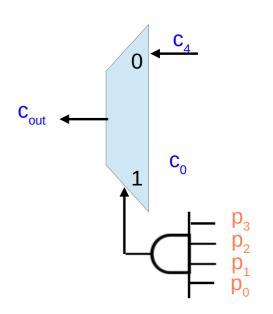

### Ripple Carry Adder

#### 4-bit Full Adder with P and G

https://upload.wikimedia.org/wikiversity/en/1/18/ RCA.Note.H.1.20151215.pdf

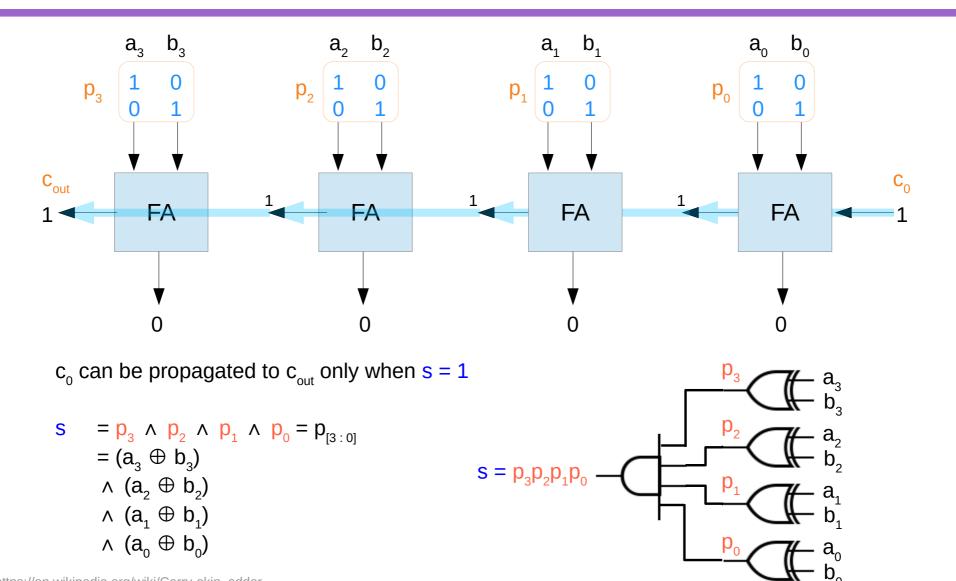

## C<sub>0</sub> propagation condition

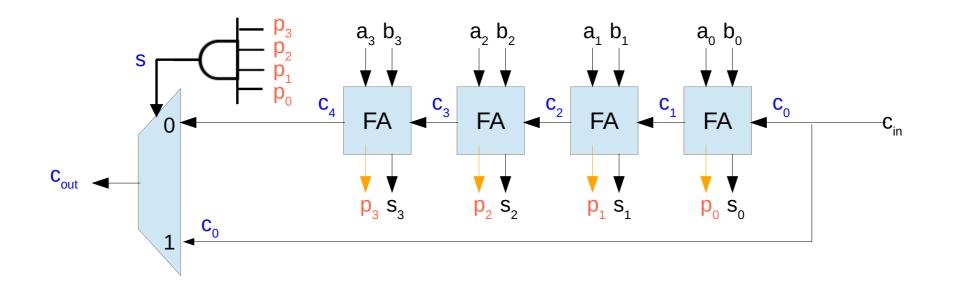

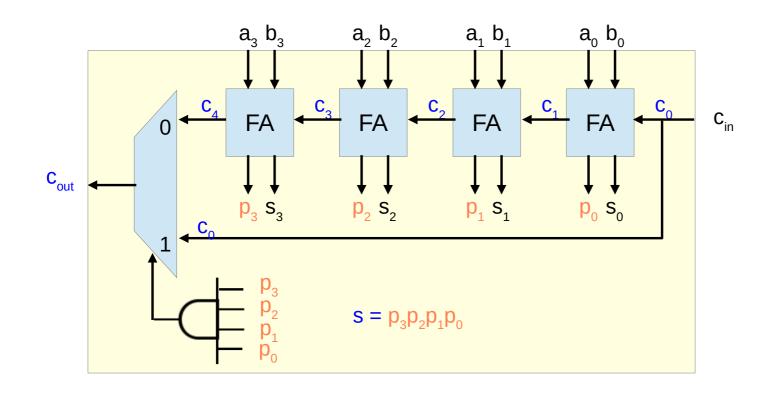

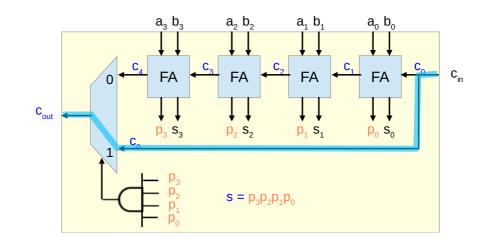

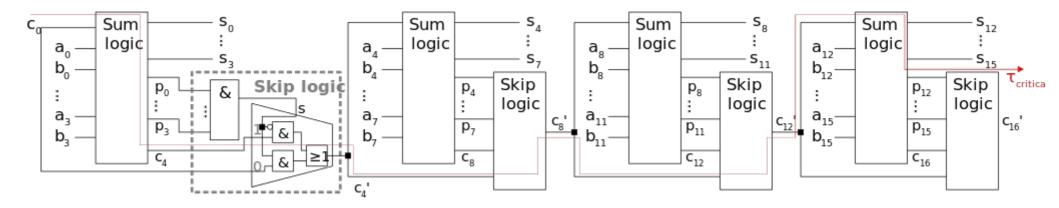

The n-bit Carry Skip Adder consists of

a n-bit **carry-ripple-chain**, a n-input **AND-gate** and one **multiplexer**.

a multiplexer switches either the last carry-bit  $c_n$  or the carry-in  $c_0$  to the carry-out signal  $c_{out}$

$\mathbf{s} = \mathbf{p}_3 \wedge \mathbf{p}_2 \wedge \mathbf{p}_1 \wedge \mathbf{p}_0 = \mathbf{p}_{[3:0]}$

when s = 1,  $c_{out} \leftarrow c_0$ otherwise, internally generated carries can be propagated to  $c_{out} \leftarrow c_4$

The critical path of a Carry Skip Adder begins at the first full adder, passes through all adders and ends at the sum bit  $s_{n-1}$

Since a <u>single *n-bit*</u> Carry Skip Adder has <u>no</u> real speed <u>benefit</u> compared to a *n-bit* Ripple Carry Adder

$T_{CSA}(n) = T_{RCA}(n)$

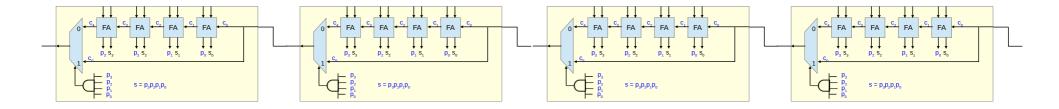

Carry Skip Adders are <u>chained</u> to reduce the <u>overall</u> critical path, (Block Carry Skip Adders)

The skip logic consists of a m-input AND gate and one MUX

$$T_{SK} = T_{AND}(m) + T_{MUX}$$

As the propagate signals are computed <u>in parallel</u> and are early available,

$$\mathbf{p}_{i} = \mathbf{a}_{i} \oplus \mathbf{b}_{i}$$

the critical path for the <u>skip logic</u> in a Carry Skip Adder consists of the delay imposed by the <u>multiplexer</u> (conditional skip)

$T_{CSK} = T_{MUX} = 2D$

Www.cs.tufts.edu

https://en.wikipedia.org/wiki/Carry-skip\_adder

#### Carry Skip Adder (5A)

20

Fixed size block carry skip adders split the n bits of the input bits Into blocks of m bits each, resulting in k = n / m blocks.

The critical path consists of the ripple path and the skip element of the first block, The skip apths that are enclosed between the first and the last block, And finally the ripple path of the last block

$T_{FCSA}(n) = T_{CRA[0:cout]}(m) + T_{CSK} + (k-2)T_{CSK} + T_{CRA}(m)$ = 3D + m 2D + (k-1)2D + (m+2)2D = (2m+k)2D + 5d

The optimal block size for a given adder width n is derived by equating to 0

$dT_{FCSA}(n) / dm = 0$

$2D(2-n(1/m^2)) = 0$

M1,2 = +-sqrt(n/2) m = sqrt(m/2)

Block carry skip adders are composed of a number of carry skip adders

There are two types of block carry skip adders

The two operands  $A = (a_{n-1}, a_{n-2}, \dots a_1, a_0)$  and  $B = (b_{n-1}, b_{n-2}, \dots b_1, b_0)$ Are split in k blocks of  $(m_k, m_{k-1}, \dots m_2, m_1)$  bits

Why are block carry skip adders used Should the block size be constant or variable? Fixed block width vs. variable block width

Oklobdzija: High-Speed VLSI arithmetic units : adders and multipliers

#### Block Carry Skip Adder

Since the Cin-to-Cout represents the longest path in the ripple-carry-adder, an obvious attempt is to accelerate carry propagation through the adder.

This is accomplished by using Carry-Propagate p, signals within a group of bits.

If <u>all</u> the  $p_i$  signals within the group are  $p_i = 1$ , the condition exist for the carry to bypass the entire group:

$\mathsf{P} = \mathsf{p}_{\mathsf{i}} \bullet \mathsf{p}_{\mathsf{i+1}} \bullet \mathsf{p}_{\mathsf{i+2}} \bullet \dots \bullet \mathsf{p}_{\mathsf{i+k-1}}$

Oklobdzija: High-Speed VLSI arithmetic units : adders and multipliers

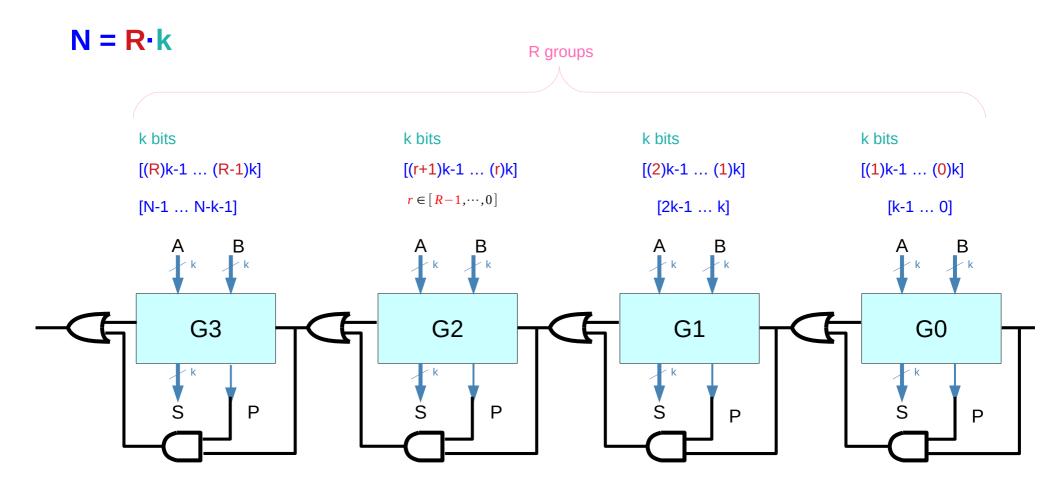

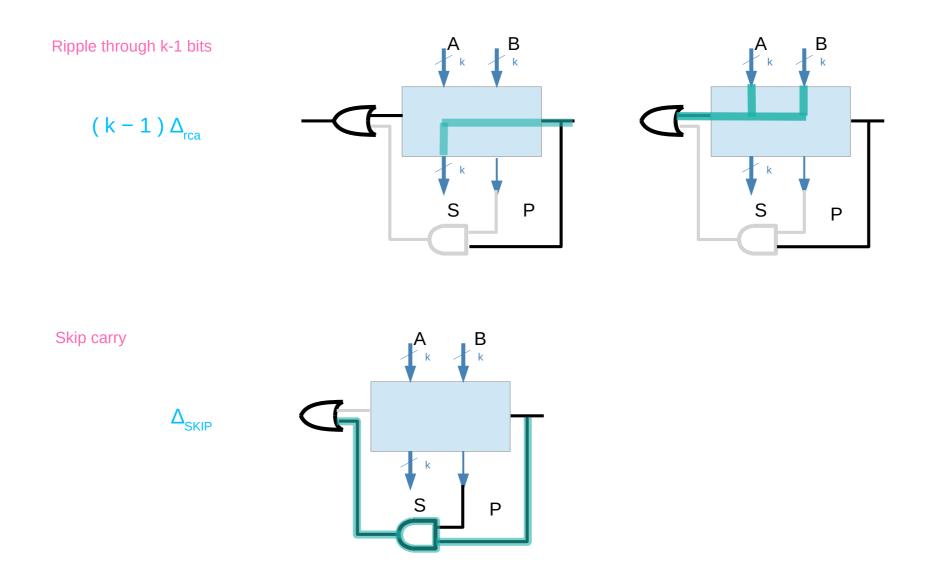

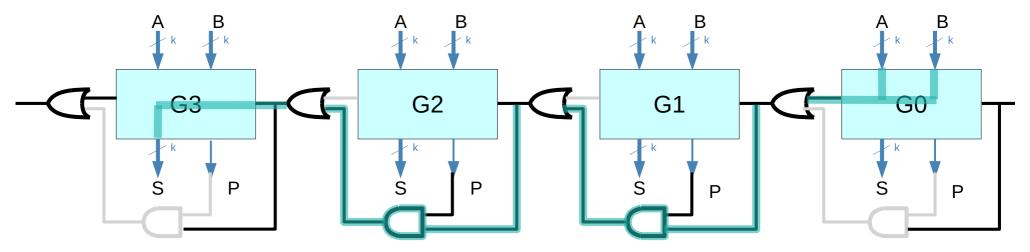

The Carry Skip Adder (CSKA) <u>divides</u> the words to be added into <u>groups</u> of <u>equal size</u> of **k-bits**.

The basic structure of an N-bit Carry Skip Adder

Within the group, carry propagates in a ripple-carry fashion.

In addition, an AND gate is used to form the group propagate signal P.  $P = p_i \cdot p_{i+1} \cdot p_{i+2} \cdot \dots \cdot p_{i+k-1}$

If P = 1 the condition exists for carry to bypass (skip) over the group

Oklobdzija: High-Speed VLSI arithmetic units : adders and multipliers

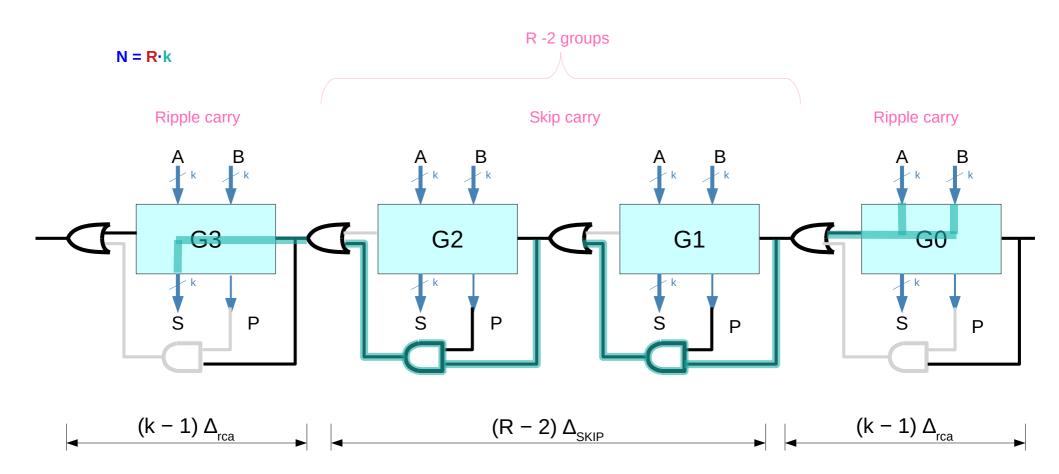

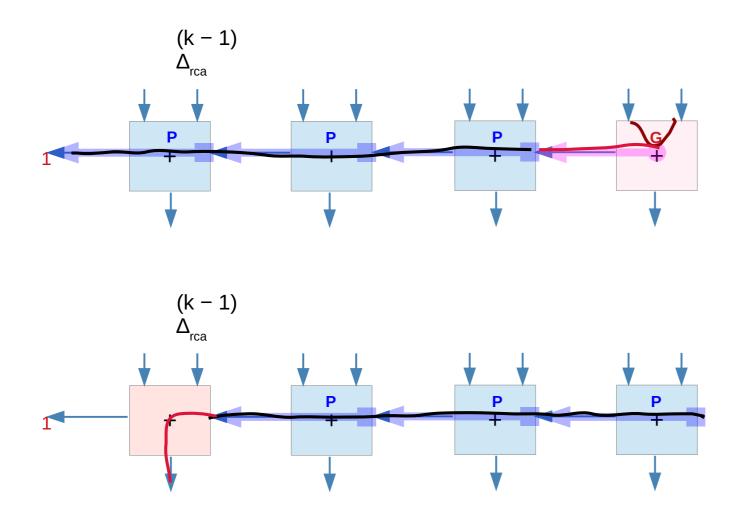

Any kill or generate condition results in divided (broken) critical paths

All FA's in R-2 groups must have the propagate condition

Oklobdzija: High-Speed VLSI arithmetic units : adders and multipliers

The <u>maximal delay</u>  $\Delta$  of a Carry Skip Adder is encountered <u>when carry</u> is generated in the <u>least-significant bit</u> position,

- rippling through *k*-1 bit positions,

- skipping over R-2 = N/k-2 groups in the middle,

- rippling to the k-1 bits of most significant group and

- being assimilated in the *N*-th bit position to produce the sum  $S_N$ :

$$\begin{split} \Delta_{\rm CSA} &= (k-1) \, \Delta_{\rm rca} + (R-2) \, \Delta_{\rm SKIP} + (k-1) \, \Delta_{\rm rca} \\ &= 2 \, (k-1) \, \Delta_{\rm rca} + (R-2) \, \Delta_{\rm SKIP} \\ &= 2 \, (k-1) \, \Delta_{\rm rca} + (N/k-2) \, \Delta_{\rm SKIP} \end{split}$$

Oklobdzija: High-Speed VLSI arithmetic units : adders and multipliers

$$\begin{split} \Delta_{\rm CSA} &= (k-1) \, \Delta_{\rm rca} + (R-2) \, \Delta_{\rm SKIP} + (k-1) \, \Delta_{\rm rca} \\ &= 2 \, (k-1) \, \Delta_{\rm rca} + (R-2) \, \Delta_{\rm SKIP} \\ &= 2 \, (k-1) \, \Delta_{\rm rca} + (N/k-2) \, \Delta_{\rm SKIP} \end{split}$$

Carry Skip Adder is faster than RCA at the expense of a few relatively simple modifications.

The delay is still linearly dependent on the size of the adder N, however this linear dependence is reduced by a factor of 1/k

Oklobdzija: High-Speed VLSI arithmetic units : adders and multipliers

$N = R \cdot k$

#### Design C (9) – When Cout1 = 1

High Performance Carry Chains for FPGAs, S. Hauck, M. M. Hosler, T. W. Fry

If an arbitrary block generated a carry by itself, The carry will always propagate to the next block However, if the second block generates a carry itself, Or kill the carry, then that is the end of the critical path

If the second block propagates the carry, then we see The advantage of the CSA architecture

https::/electronics.stackexchange.com/questions/21251/critical-path-for-carryskip-adder

https::/electronics.stackexchange.com/questions/21251/critical-path-for-carry-skip-adder

#### References

- [1] en.wikipedia.org

- [2] Parhami, "Computer Arithmetic Algorithms and Hardware Designs"