## CMOS Delay-7 (H.8) Delay Model

20170125

Copyright (c) 2015 - 2016 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

| • | References                                                                         |

|---|------------------------------------------------------------------------------------|

|   | ricicies                                                                           |

|   |                                                                                    |

|   | Some Figures from the following sites                                              |

|   |                                                                                    |

|   | [1] http://pages.hmc.edu/harris/cmosvlsi/4e/index.html<br>Weste & Harris Book Site |

|   | [2] on wikingdia org                                                               |

|   | [2] en.wikipedia.org                                                               |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

|   |                                                                                    |

B: Device Transconductance Parameter

k: Process Transconductance Parameter

M: Electron / Hole Mobility

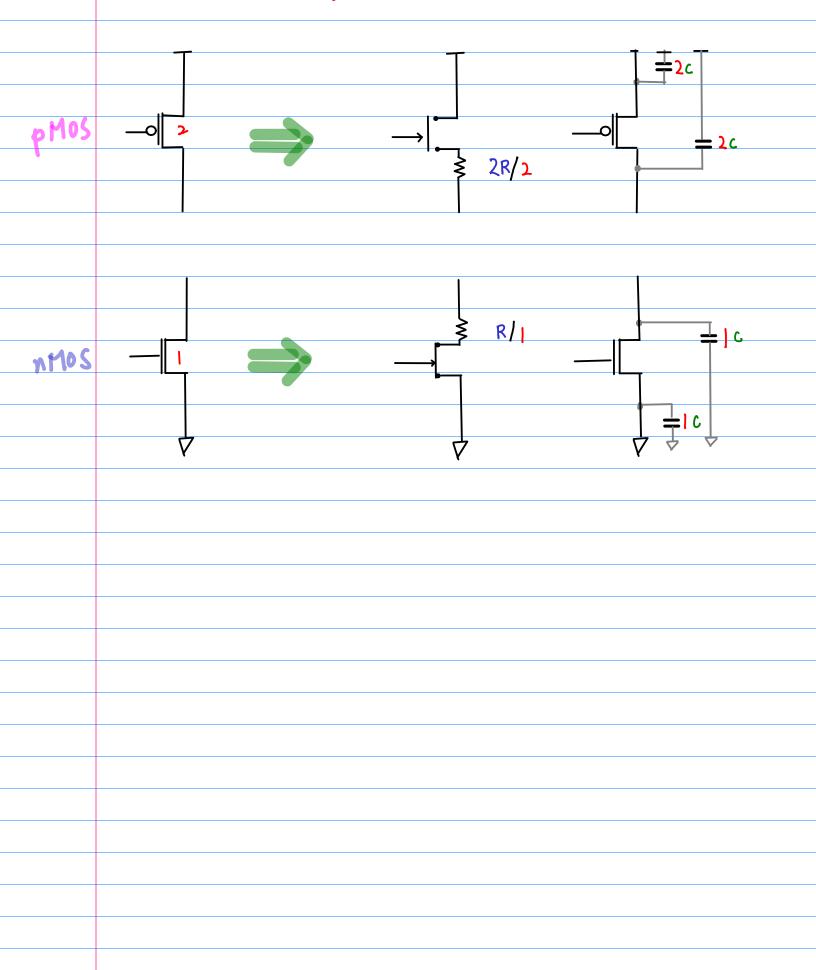

PMOS

$$\beta_P = k_P' \left( \frac{\omega}{L} \right)_P$$

$k_P' = \mu_P C_{ox}$   $C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$

$$n MOS$$

$\beta_n = k'_n \left(\frac{\omega}{L}\right)_n$   $k'_n = \mu_n C_{ox}$   $C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$

Saturation Current

$$I_{dp} = \frac{\beta_p}{2} \left( V_{GSN} - |V_{Tp}| \right)^2 \qquad V_{Tp} < 0$$

$$I_{dn} = \frac{\rho_n}{2} \left( V_{GSn} - V_{Tn} \right)^2 \qquad V_{Tn} > 0$$

$$\frac{\beta_n}{\beta_p} = \frac{k'_n \left(\frac{\omega}{L}\right)_n}{k'_p \left(\frac{\omega}{L}\right)_p}$$

$$\frac{k'_n}{k'_p} = 2 \sim 3$$

$$\frac{k'_n}{k'_p} = \frac{\mu_n}{\mu_p} = r$$

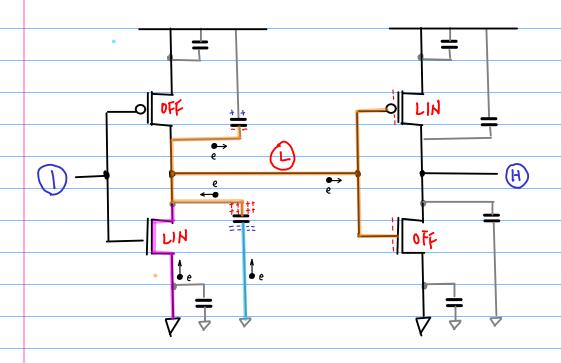

fall time tf

rise time tr

$$R_n = \frac{1}{\beta_n (V_{DD} - V_{T_D})}$$

$$R_{p} = \frac{1}{\beta_{n} (V_{pp} - V_{T_{p}})}$$

| fall time              | $t_f = 2.2  T_n = \ln 9  T_n$                                                       | 0.9 Upp -> 0.1 Vpp      |

|------------------------|-------------------------------------------------------------------------------------|-------------------------|

| rise time              | tr = 2.2 Tp = ln 9 Zp                                                               | 0.1 Vpp -> 0.9 Vpp      |

| propagation delay time | $t_p = \frac{1}{2} (t_{pf} + t_{pr})$<br>= 0.35(t <sub>pf</sub> + t <sub>pr</sub> ) | 0.5 Vpp -> 0.5 Vpp      |

| propagation fall time  | tpf = 0.η ζη = ln 2 ζη                                                              | Vpb → O.5 Vbb           |

| propagation rise time  | tpr = 0.7 Tp = ln 2 Tp                                                              | 0 → 0.5 V <sub>Pb</sub> |

|                        | $\frac{7_n = Rn(Cpara + C_1)}{T_n = n(C_1 + C_2)}$                                  |                         |

|                        | Tp = Rp (Cpana + CL)                                                                |                         |

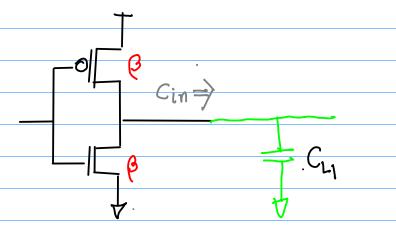

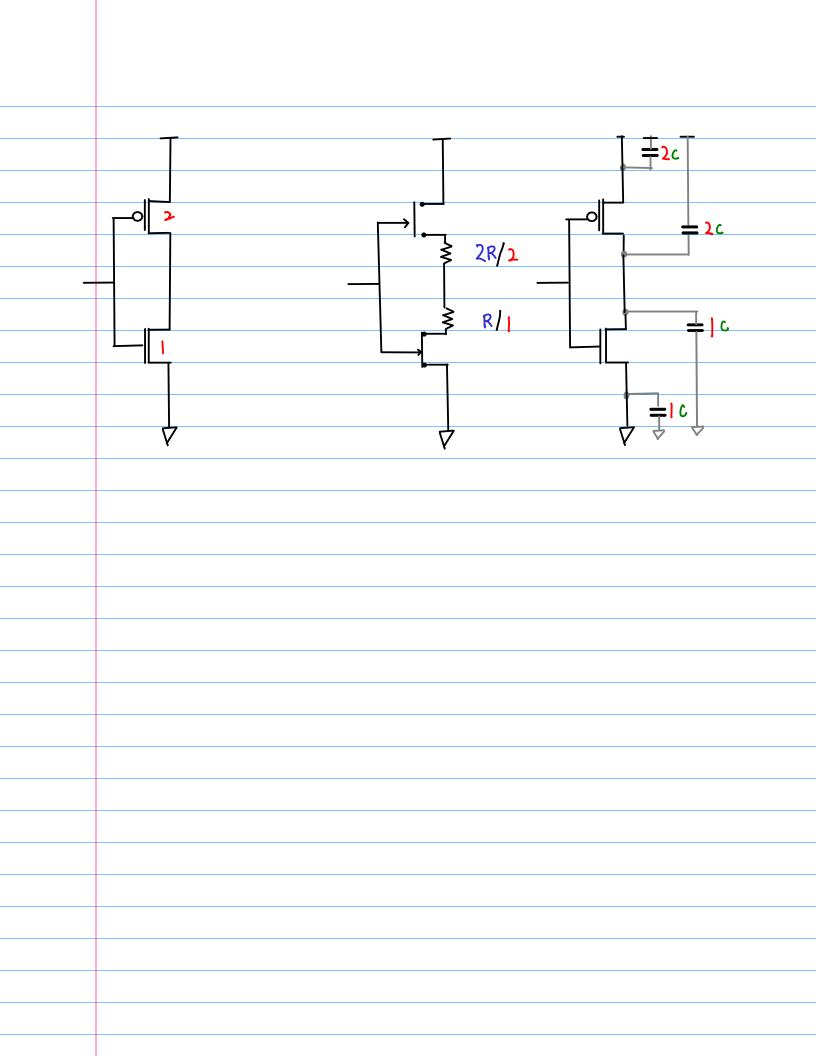

Cout = Cpara + C1

$$\left(\frac{W}{L}\right)_{p} = \gamma \left(\frac{W}{L}\right)_{n}$$

$$\gamma = \frac{\mu_n}{\mu_p} = \frac{k_n}{k_p} > 1$$

$$R_n = R_p = R^2 \frac{1}{\beta(V_{pp} - V_T)}$$

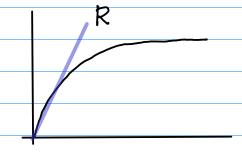

$$\begin{cases} V_{\text{out}}(t) = V_{\text{pv}}(1 - e^{-t/z}) \\ V_{\text{out}}(t) = V_{\text{pv}}e^{-t/z} \end{cases}$$

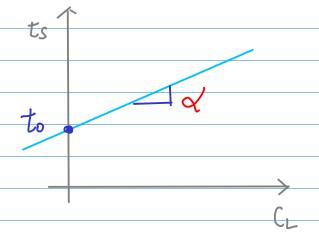

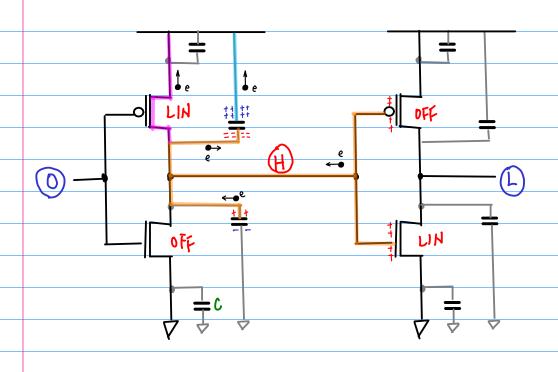

#### Generic Switching Delay

$$ts = t_0 + \alpha C_L \Rightarrow t_s = t_r - t_f$$

### Generic Switching Delay

to: zero delay x: slope

reference case

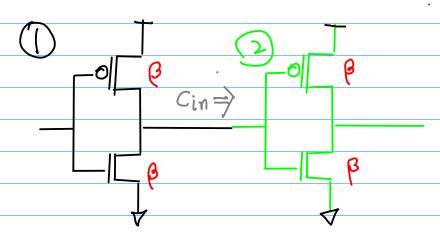

Generic Switching Delay of

$$ts_1 = t_0 + \alpha C_{21}$$

=  $t_0 + \alpha C_{in}$

the channel length L assumed

$$Cin = Cox L (W_n + W_p)$$

$$= Cox L (W_n + Y W_p)$$

$$= Cox L W_n \cdot (1 + Y)$$

$$= Cox L W_n \cdot (1 + Y)$$

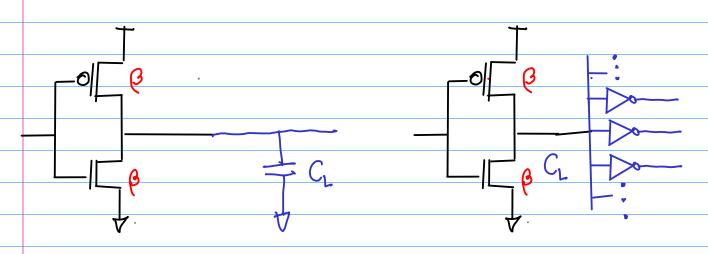

When CL>>> Cin

to minimize ts

Speed V.s. area tradeoff

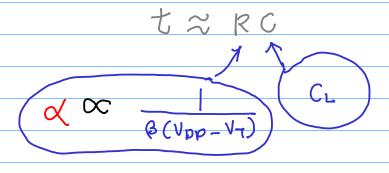

$$ts = t_0 + \alpha C_L t \approx RC$$

$$\alpha \propto \frac{1}{\beta(V_{pp}-V_T)} C_L$$

to minimize ts

Speed V.s. area tradeoff

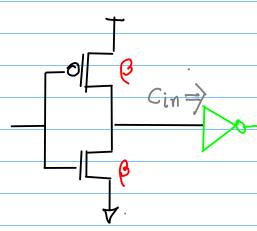

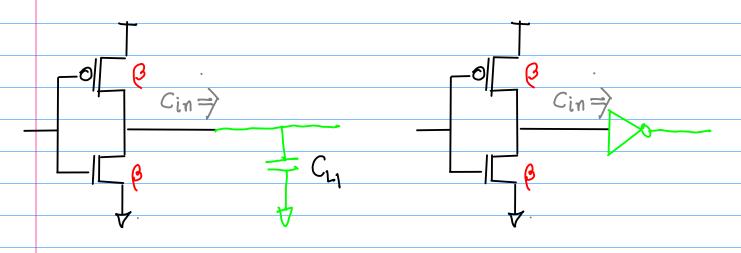

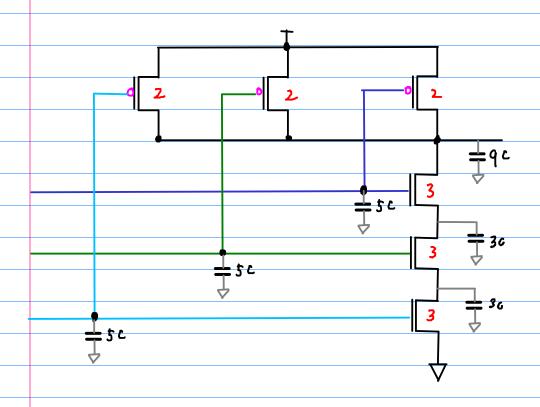

Scaling Factor S

$$R' = \frac{R}{\sqrt{3}}$$

$$\alpha' = \alpha$$

$$ts = t_0 + \frac{\alpha}{\beta} C_L$$

Compensation Factor S

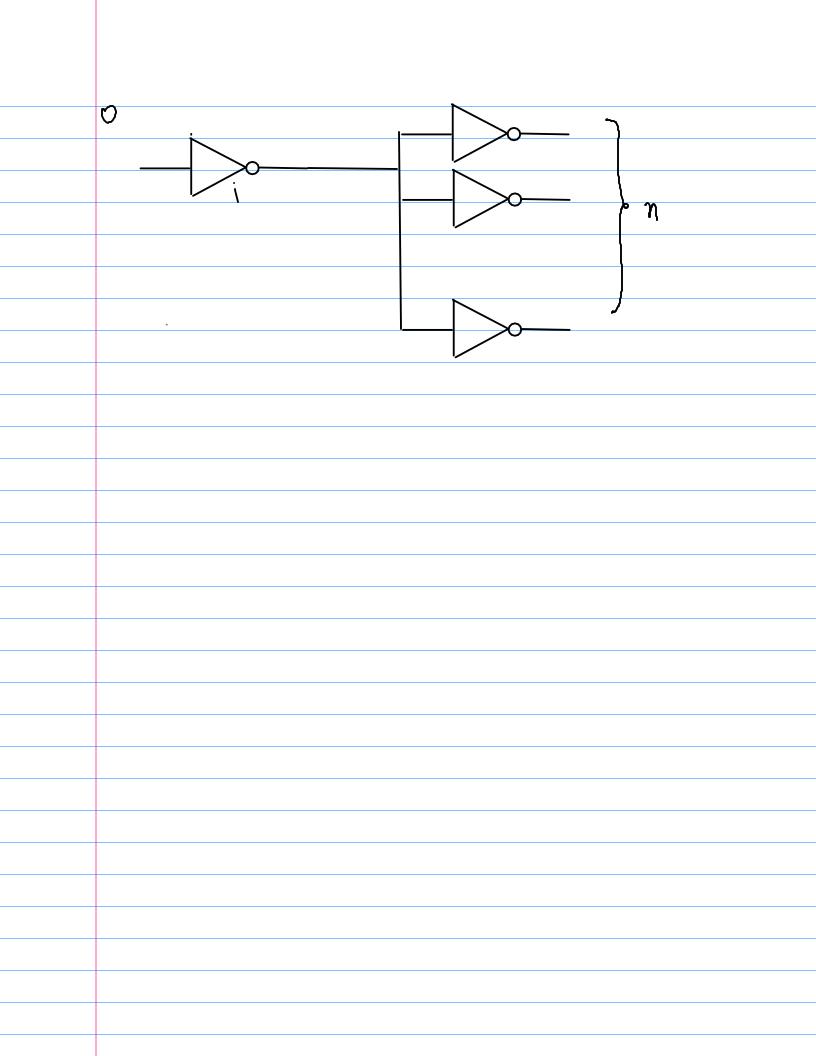

enables a NOT gate drive larger values of CL

If  $C_{L}=5$  Cin (increased by the scaling factor \$)

then the switching time is the same

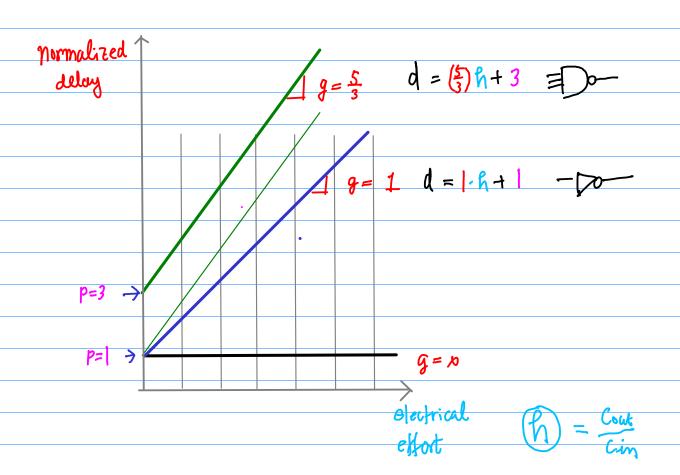

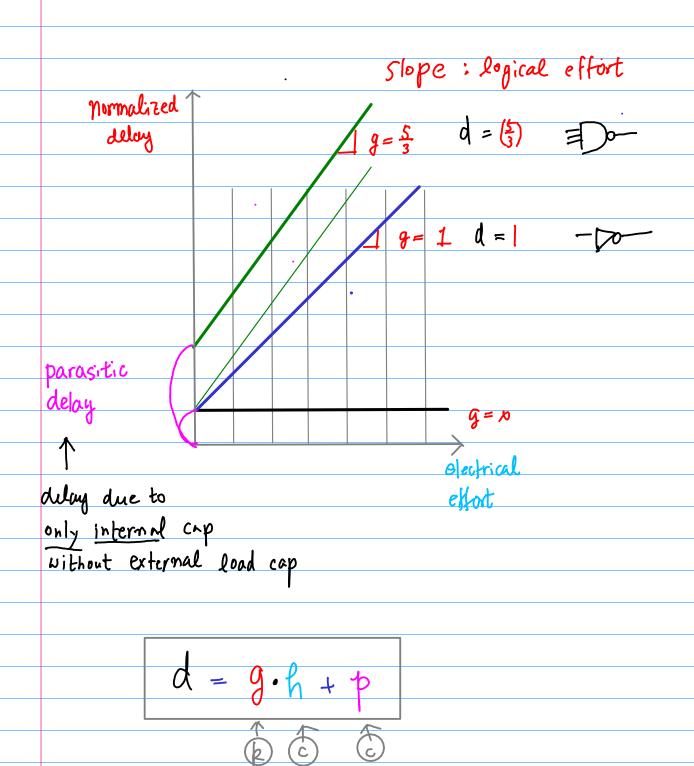

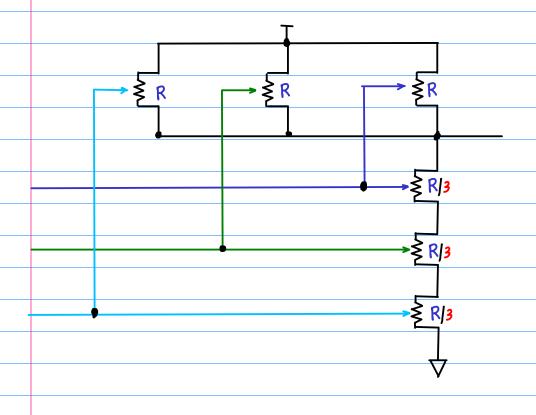

# RC Delay Model

## Linear Delay Model