## CMOS Delay-9 (H.0) Interconnect Delay

20170119

Copyright (c) 2015 - 2016 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

# References Some Figures from the following sites [1] http://pages.hmc.edu/harris/cmosvlsi/4e/index.html Weste & Harris Book Site [2] en.wikipedia.org

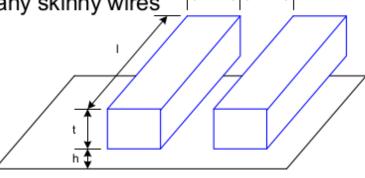

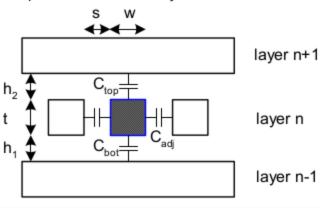

## Wire Geometry

- ☐ Pitch = w + s

- ☐ Aspect ratio: AR = t/w

- Old processes had AR << 1

- Modern processes have AR ≈ 2

Pack in many skinny wires

14: Wires

CMOS VLSI Design 4th Ed.

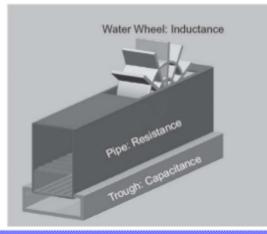

## Interconnect Modeling

- ☐ Current in a wire is analogous to current in a pipe

- Resistance: narrow size impedes flow

- Capacitance: trough under the leaky pipe must fill first

- Inductance: paddle wheel inertia opposes changes in flow rate

- Negligible for most wires

14: Wires

CMOS VLSI Design 4th Ed.

٠,

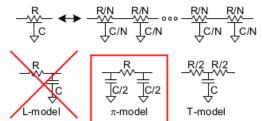

#### **Lumped Element Models**

- ☐ Wires are a distributed system

- Approximate with lumped element models

N segments

- $\Box$  3-segment  $\pi$ -model is accurate to 3% in simulation

- ☐ L-model needs 100 segments for same accuracy!

- $lue{}$  Use single segment  $\pi$ -model for Elmore delay

14: Wires

CMOS VLSI Design 4th Ed.

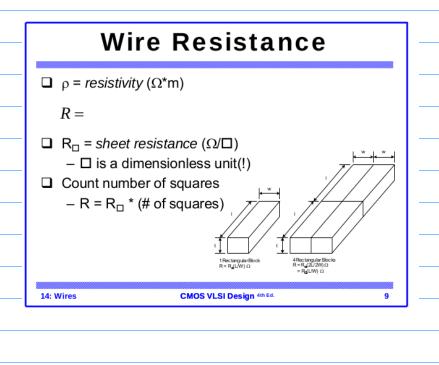

## Wire Capacitance

- Wire has capacitance per unit length

- To neighbors

- To layers above and below

$$\Box C_{total} = C_{top} + C_{bot} + 2C_{adj}$$

14: Wires

CMOS VLSI Design 4th Ed.

## Diffusion & Polysilicon

- Diffusion capacitance is very high (1-2 fF/μm)

- Comparable to gate capacitance

- Diffusion also has high resistance

- Avoid using diffusion runners for wires!

- □ Polysilicon has lower C but high R

- Use for transistor gates

- Occasionally for very short wires between gates

14: Wires

CMOS VLSI Design 4th Ed.

# Wire RC Delay

Estimate the delay of a 10x inverter driving a 2x inverter at the end of the 1 mm wire. Assume wire capacitance is 0.2 fF/μm and that a unit-sized inverter has R = 10 KΩ and C = 0.1 fF.

$$- t_{od} = 800 \Omega$$

$$1000 \Omega \Rightarrow 1000 \text{ fF} 100 \text{ fF} 0.6 \text{ fF}$$

Driver Wire Load

14: Wires CMOS VLSI Design 4th Ed. 19