# ISA Assembler Format (4C)

**Coprocessor Instructions**

| Copyright (c) 2014 - 2019 Young W. Lim.                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License". |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

| Please send corrections (or suggestions) to youngwlim@hotmail.com.                                                                                                                                                                                                                                                                                                              |

| This document was produced by using LibreOffice.                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

### Based on

ARM System-on-Chip Architecture, 2<sup>nd</sup> ed, Steve Furber

### **Coprocessor Instruction**

#### **Coprocessor Data Transfers**

LDC | STC {<cond>} {L} <CP#>, CRd, [Rn, <offset>] {!} LDC | STC {<cond>} {L} <CP#>, CRd, [Rn], <offset>

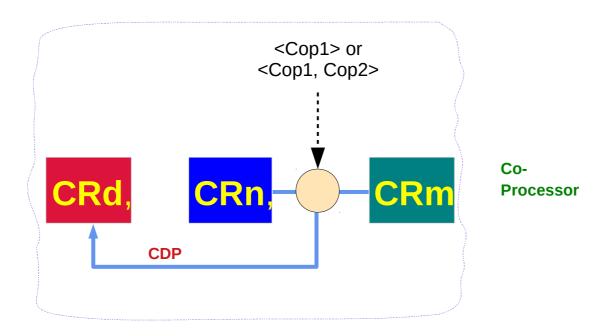

#### **Coprocessor Data Operations**

CDP {<cond>} <CP#>, <Cop1>, CRd, CRn, CRm {, <Cop2>}

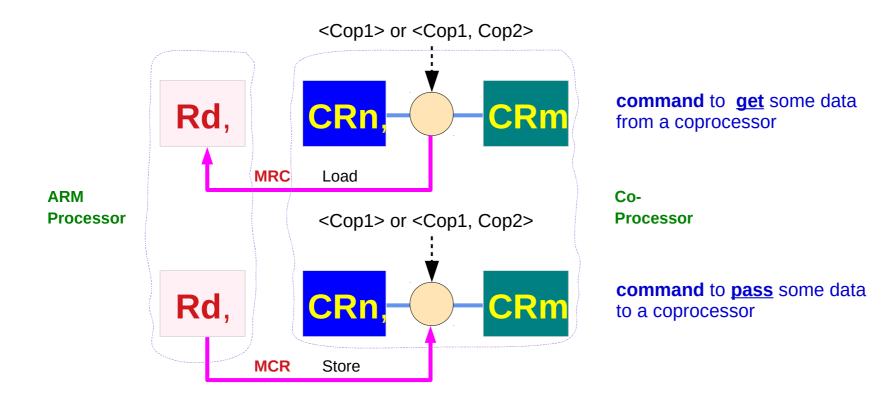

#### **Coprocessor Register Transfers**

MRC {<cond>} <CP#>, <Cop1>, Rd, CRn, CRm {, <Cop2>} MCR {<cond>} <CP#>, <Cop1>, Rd, CRn, CRm {, <Cop2>}

### **Coprocessor Instruction Mnemonics**

L o a d coprocessor

Load data from the <u>memory</u> into a <u>coprocessor</u> <u>register</u>

CRd, [Rn, <offset>] {!} CRd, [Rn], <offset>

S T C coprocessor

Store data from a <u>coprocessor</u> register to the <u>memory</u>

C D P coprocessor Data Processing

Perform an operation over CRd and CRm and place the result in CRd

CRd, CRn, CRm

Move Reg coprocessor

**command** to **get** some data from a coprocessor

Move coprocessor Reg

**command** to **pass** some data to a coprocessor

Rd, CRn, CRm

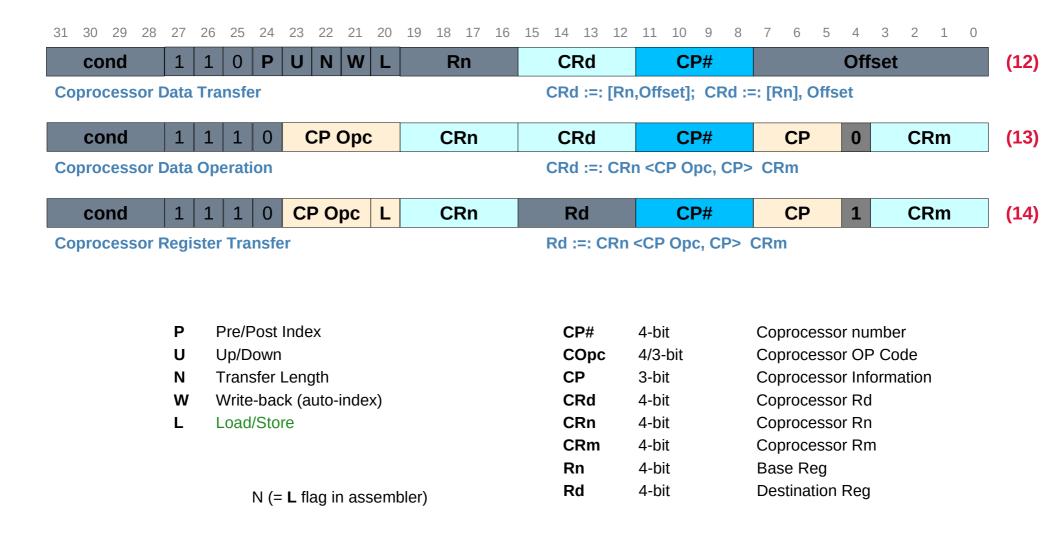

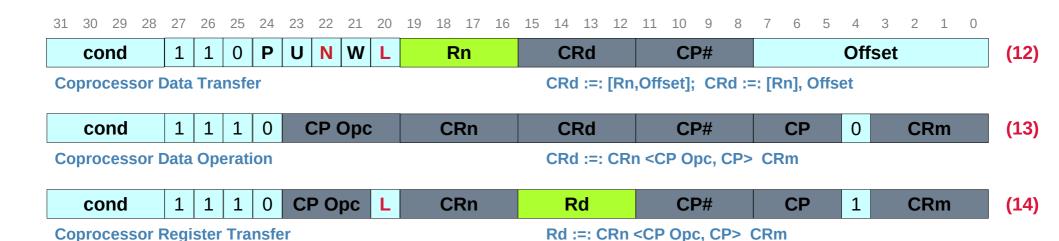

### Coprocessor Instruction Encodings

CP Opc

| cond |    |    | 1 1 0 P U N W L |   |   |   | Rn CRd |  |        |  |  | CP# |     |  |  | Offset |     |  |  |     |  | (12) |  |  |    |  |   |  |    |   |      |

|------|----|----|-----------------|---|---|---|--------|--|--------|--|--|-----|-----|--|--|--------|-----|--|--|-----|--|------|--|--|----|--|---|--|----|---|------|

|      | СО | nd |                 | 1 | 1 | 1 | 0      |  | CP Opc |  |  |     | CRn |  |  |        | CRd |  |  | CP# |  |      |  |  | CP |  | 0 |  | CR | m | (13) |

Rd

CP#

**CP**

1

**CRm**

(14)

#### **Coprocessor Data Transfers**

1

0

1

cond

1

LDC | STC {<cond>} {L} < CP#>, CRd, [Rn, <offset>] {!}

**CRn**

LDC | STC {<cond>} {L} < CP#>, CRd, [Rn], <offset>

#### **Coprocessor Data Operations**

CDP {<cond>} <**CP**#>, <Cop1>, CRd, CRn, CRm {, <Cop2>}

#### **Coprocessor Register Transfers**

MRC {<cond>} <**CP**#>, <Cop1>, Rd, CRn, CRm {, <Cop2>}

MCR {<cond>} <**CP**#>, <Cop1>, Rd, CRn, CRm {, <Cop2>}

# **ARM Coprocessor Instruction Fields**

**<CP#>** Coprocessor number

<Cop1> Coprocessor operation 1 <CP Opc>

<Cop2> Coprocessor operation 2 <CP>

**CRd** Coprocessor Rd

**CRn** Coprocessor Rn

**CRm** Coprocessor Rm

**CP#**: identifes a coprocessor (a number in [0, 15]) a coprocessor will <u>ignore</u> any instruction that has an incorrect **CP#**

CP Opc (Cop1) and possible the CP (Cop2): specified what operation the coprocessor should perform on the contents of CRn and CRm, and place the result in CRd.

### Coprocessor Access Fields

#### **ARM Access Fields**

L=0 Store to memory STC MCR

L=1 Load from memory LDC MRC

N=0 Short Transfer

N=1 Long Transfer with L flag in assembler

### Coprocessor Data Transfers

#### **Preindex Coprocessor Data Transfer**

LDC | STC {<cond>} {**L**} <CP#>, CRd, [Rn, <offset>] {!}

**Postindex Coprocessor Data Transfer**

LDC | STC {<cond>} {**L**} <CP#>, CRd, [Rn], <offset>

**CP#**: identifes a coprocessor (a number in [0, 15]) a coprocessor will <u>ignore</u> any instruction that has an <u>incorrect</u> CP#

The **CRd** field and the **N** bit field in the <u>encoding</u> contain information which may be interpreted in different ways by different coprocessors,

**CRd** is the register to be transferred (the first register)

N bit selects transfer length options.

**N=0** the transfer of a <u>single</u> register :: when  $\bot$  is present (long transfer)

**N=1** the transfer of <u>all</u> the <u>registers</u> for <u>context switching</u>. :: otherwise

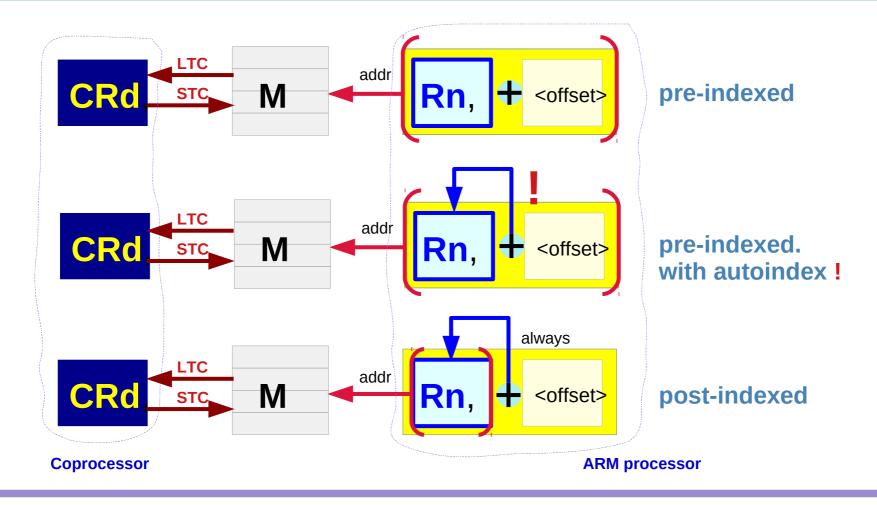

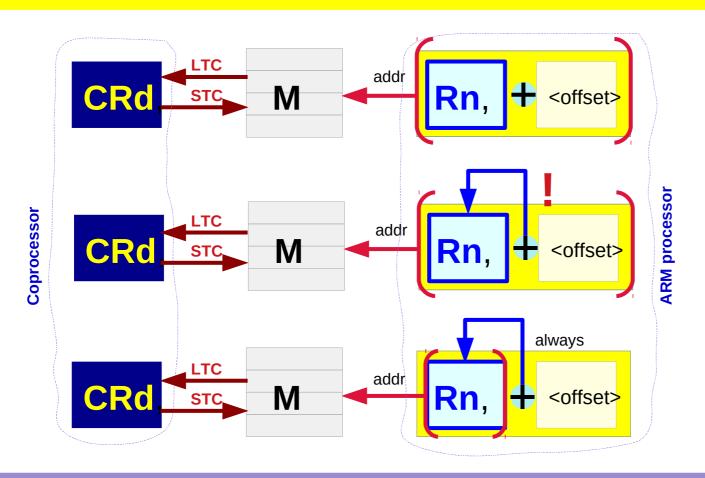

# Pre-indexing and Post-indexing Coprocessor Instructions

### Pre-indexing and Post-indexing Coprocessor Instructions

#### **Coprocessor Data Transfers**

Pre-indexed CRd, [Rn, <offset>]

pre-indexed. with autoindex! CRd, [Rn, <offset>]!

Post-indexed CRd, [Rn], <offset>

### Coprocessor Data Transfers – Preindex

#### **Preindex Coprocessor Data Transfer**

```

LDC | STC {<cond>} {L} <CP#>, CRd, [Rn, <offset>] {!}

```

```

LDC | STC

<CP#>, CRd, [Rn, <offset>]

LDC | STC <cond>

<CP#>, CRd, [Rn, <offset>]

LDC | STC

<CP#>, CRd, [Rn, <offset>] !

LDC | STC <cond>

<CP#>, CRd, [Rn, <offset>] !

LDC | STC

L

<CP#>, CRd, [Rn, <offset>] !

LDC | STC <cond> L

<CP#>, CRd, [Rn, <offset>] !

LDC | STC <cond> L

<CP#>, CRd, [Rn, <offset>] !

LDC | STC <cond> L

<CP#>, CRd, [Rn, <offset>] !

```

### Coprocessor Data Transfers – Postindex

#### **Postindex Coprocessor Data Transfer**

LDC | STC {<cond>} {L} <CP#>, CRd, [Rn], <offset>

```

LDC | STC

<CP#>, CRd, [Rn], <offset>

LDC | STC <cond>

<CP#>, CRd, [Rn], <offset>

LDC | STC

L

<CP#>, CRd, [Rn], <offset>

LDC | STC <cond> L

<CP#>, CRd, [Rn], <offset> !

LDC | STC

<CP#>, CRd, [Rn], <offset> !

LDC | STC <cond> L

<CP#>, CRd, [Rn], <offset> !

LDC | STC <cond> L

<CP#>, CRd, [Rn], <offset> !

LDC | STC <cond> L

<CP#>, CRd, [Rn], <offset> !

```

### **Coprocessor Data Operations**

#### **Coprocessor Data Processing Operations**

```

CDP {<cond>} <CP#>, <Cop1>, CRd, CRn, CRm

CDP {<cond>} <CP#>, <Cop1>, CRd, CRn, CRm, <Cop2>

```

**CP#**: identifes a coprocessor (a number in [0, 15]) a coprocessor will <u>ignore</u> any instruction that has an <u>incorrect</u> CP#

CP Opc (Cop1) and possible the CP (Cop2): specified what operation the coprocessor should perform on the contents of CRn and CRm, and place the result in CRd.

<expression1> evaluated to a constant and placed in the CP Opc field

<expression2> where present is evaluated to a constant and placed in the CP field

### **Coprocessor Data Operations**

#### **Coprocessor Data Processing Operations**

CDP {<cond>} <CP#>, <Cop1>, CRd, CRn, CRm CDP {<cond>} <CP#>, <Cop1>, CRd, CRn, CRm, <Cop2>

### **Coprocessor Data Operations**

#### **Coprocessor Data Processing Operations**

```

CDP {<cond>} <CP#>, <Cop1>, CRd, CRn, CRm

CDP {<cond>} <CP#>, <Cop1>, CRd, CRn, CRm, <Cop2>

```

# Coprocessor Register Transfers (R←C, C←R)

**Move to ARM Register from Coprocessor**

MRC {<cond>} <CP#>, <Cop1>, Rd, CRn, CRm {, <Cop2>}

**Move to Coprocessor from ARM Registers**

MCR {<cond>} <CP#>, <Cop1>, Rd, CRn, CRm {, <Cop2>}

**CP#**: identifes a coprocessor (a number in [0, 15]) a coprocessor will <u>ignore</u> any instruction that has an <u>incorrect</u> CP#

CP Opc (Cop1) and possible the CP (Cop2): specified what operation the coprocessor should perform on the contents of CRn and CRm, and place the result in CRd.

**CRn** is the coprocessor src / dst register of the transformation

**CRm** is a 2<sup>nd</sup> coprocessor register involved in some way which depends on the particular operation specified.

# Coprocessor Register Transfers (R←C, C←R)

#### **Move to ARM Register from Coprocessor**

MRC {<cond>} <CP#>, <Cop1>, Rd, CRn, CRm {, <Cop2>}

**Move to Coprocessor from ARM Registers**

MCR {<cond>} <CP#>, <Cop1>, Rd, CRn, CRm {, <Cop2>}

# Coprocessor Register Transfers (R←C)

#### **Move to ARM Register from Coprocessor**

```

MRC {<cond>} <CP#>, <Cop1>, Rd, CRn, CRm

MRC {<cond>} <CP#>, <Cop1>, Rd, CRn, <u>CRm</u>, <Cop2>

```

# Coprocessor Register Transfers (C←R)

#### **Move to Coprocessor from ARM Registers**

```

MCR {<cond>} <CP#>, <Cop1>, Rd, CRn, CRm

MCR {<cond>} <CP#>, <Cop1>, Rd, CRn, CRm, <Cop2>

```

# **Breakpoint Instruction**

**Breakpoint Instruction (BKPT)**

BRK

#### References

- [1] ftp://ftp.geoinfo.tuwien.ac.at/navratil/HaskellTutorial.pdf

- [2] https://www.umiacs.umd.edu/~hal/docs/daume02yaht.pdf