# Latches and Flip-flops (1A)

Young Won Lim 11/6/13 Copyright (c) 2011-2013 Young W. Lim.

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".

Please send corrections (or suggestions) to youngwlim@hotmail.com.

This document was produced by using OpenOffice and Octave.

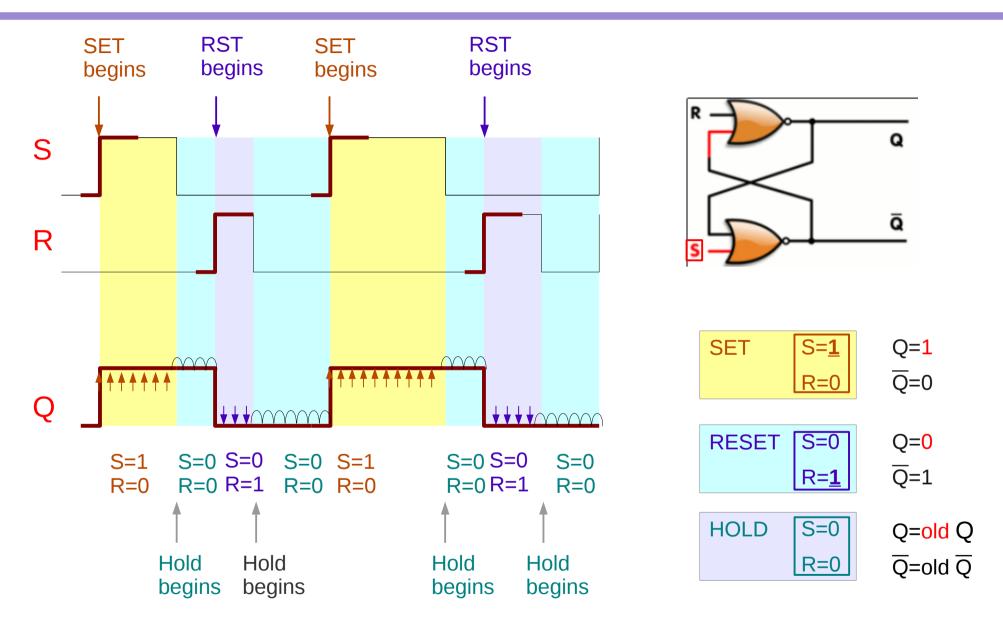

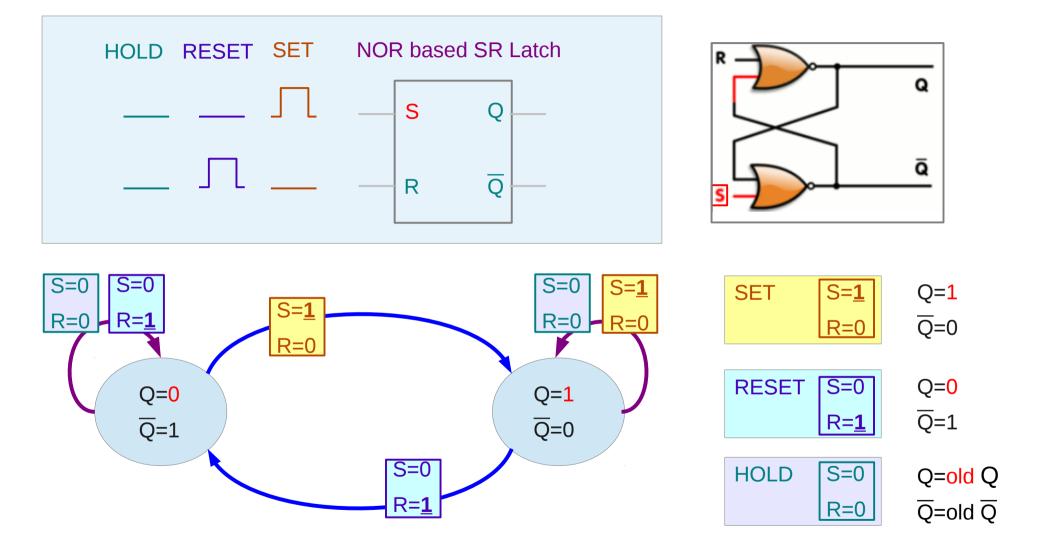

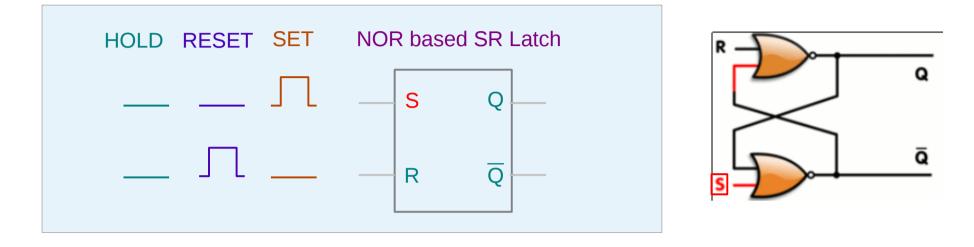

# NOR-based SR Latch

#### **NOR-based SR Latch States**

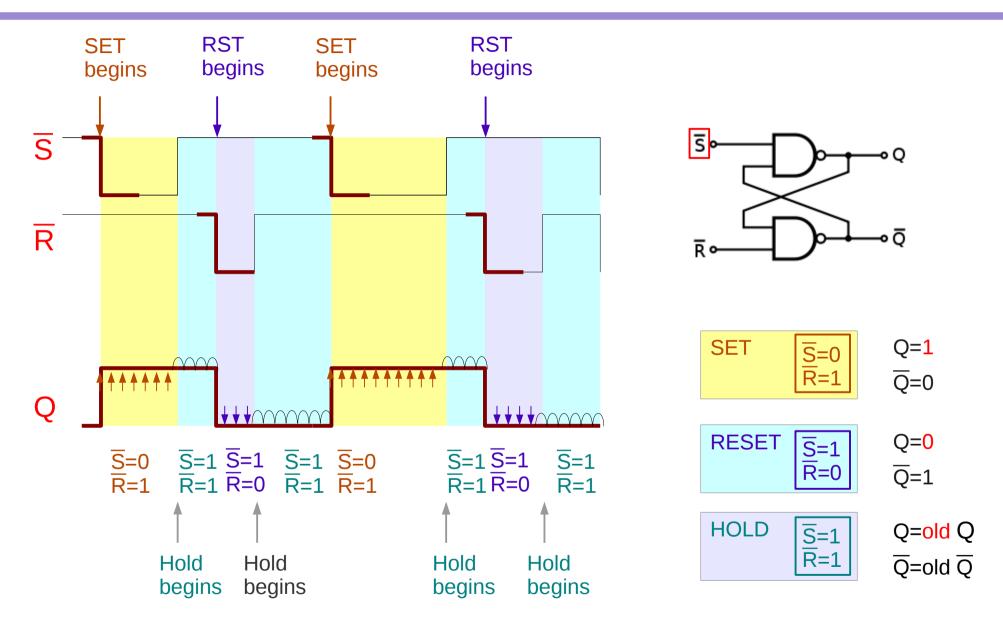

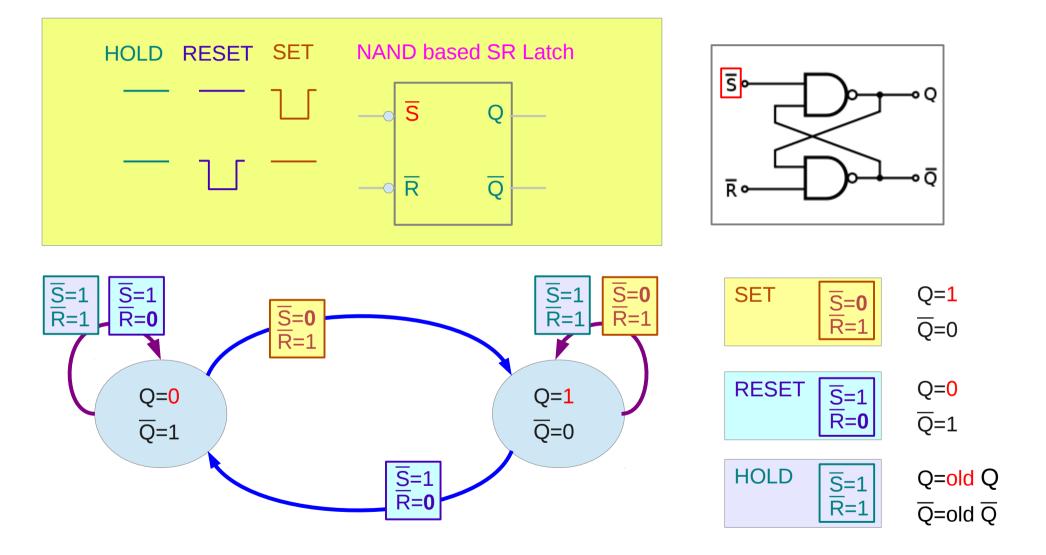

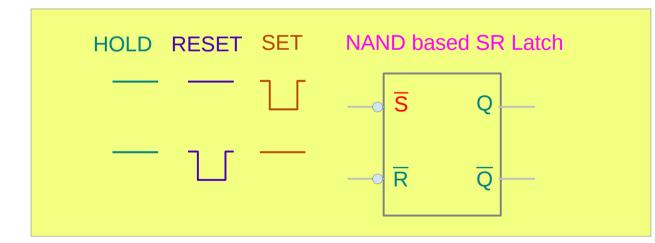

# NAND-based SR Latch

#### NAND-based SR Latch States

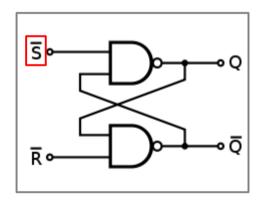

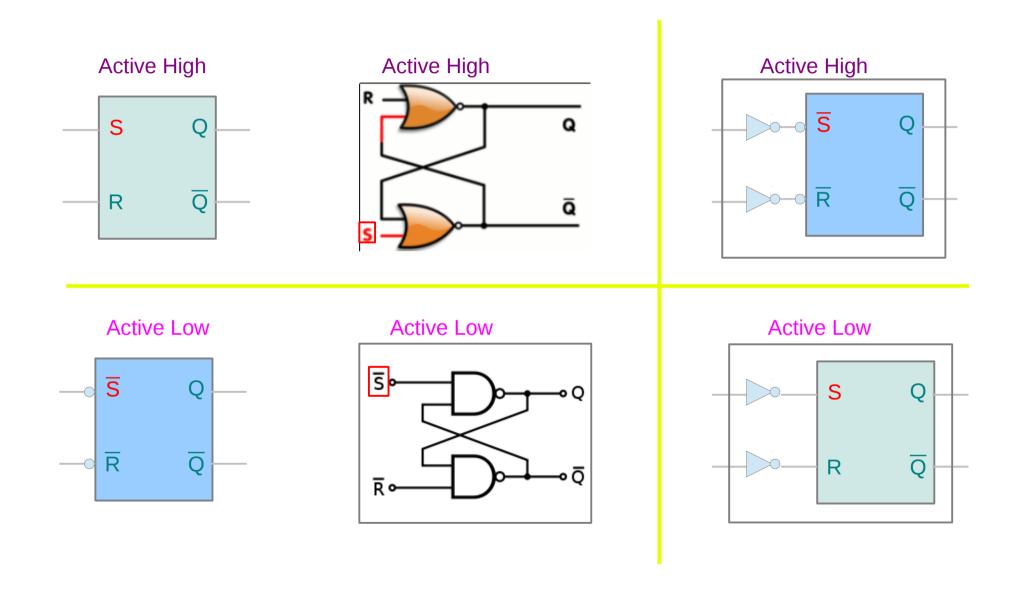

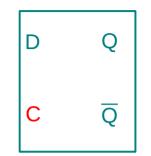

#### SR Latch Symbols

#### Active High and Low Inputs

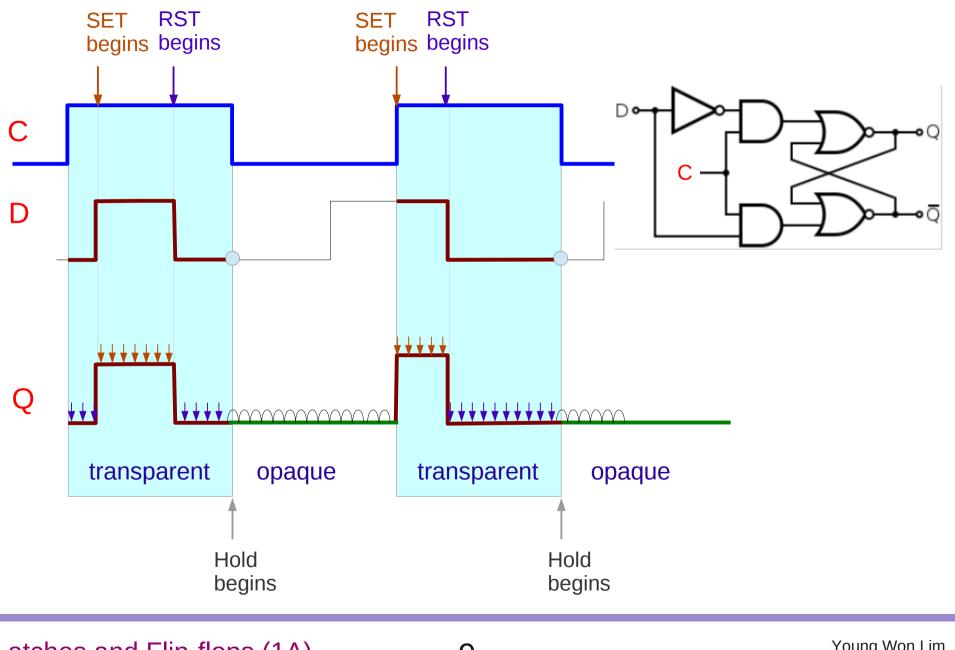

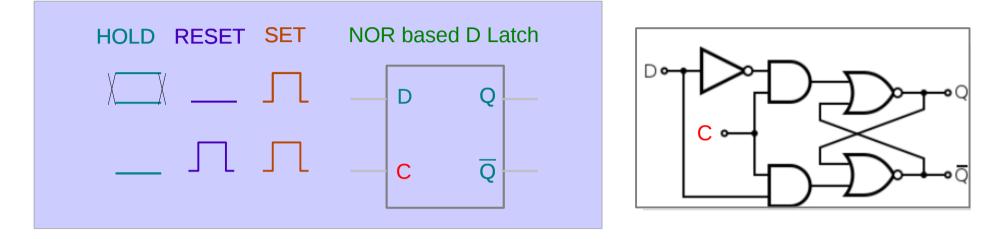

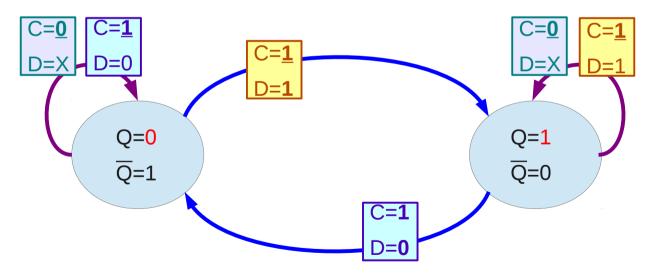

#### NOR-based D Latch

#### NOR-based D Latch

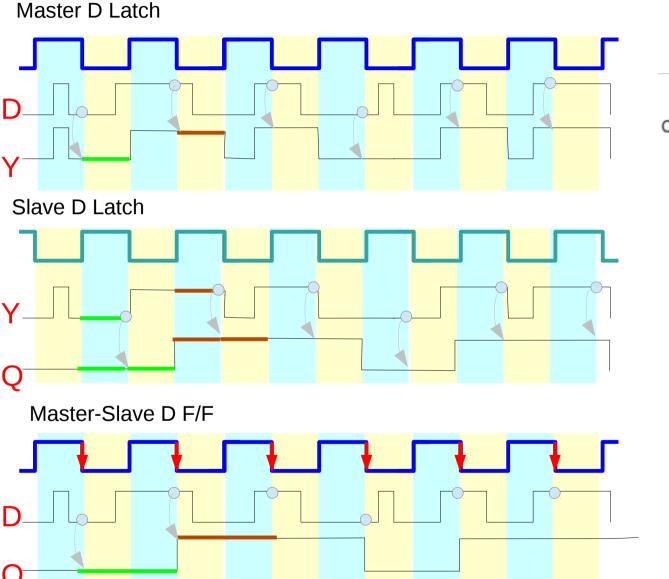

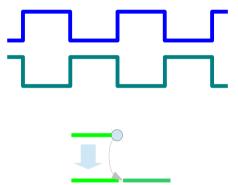

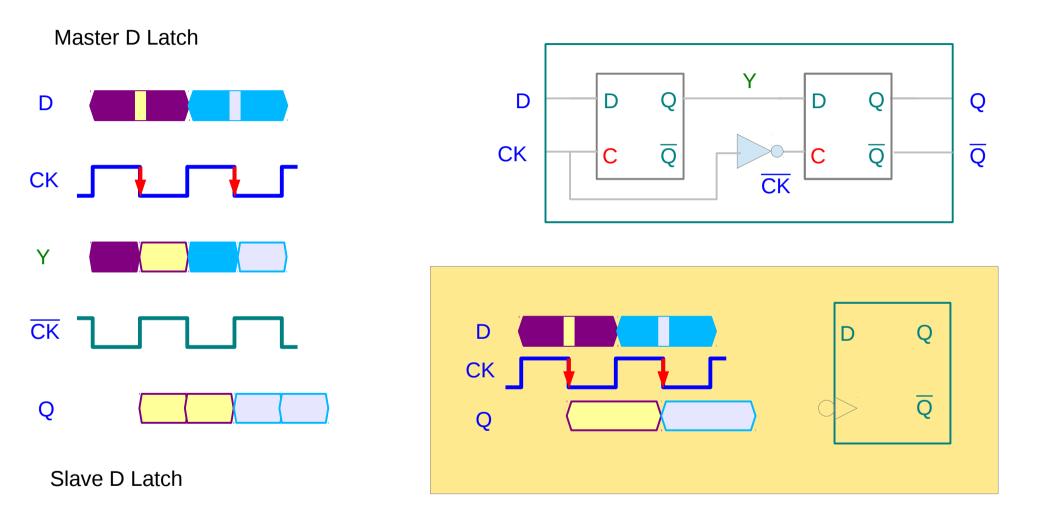

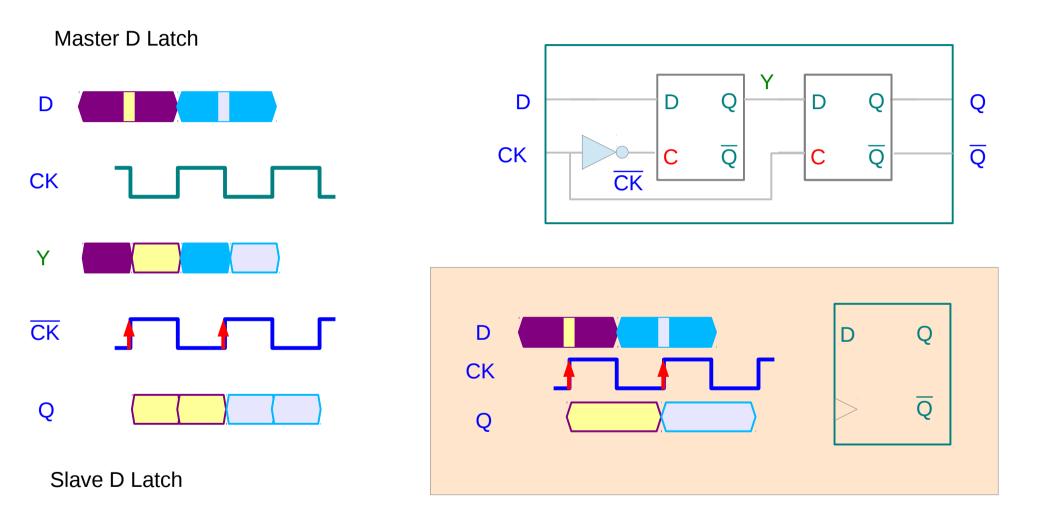

# Master-Slave D FlipFlop

the hold output of the master is transparently reaches the output of the slave this value is held for another half period

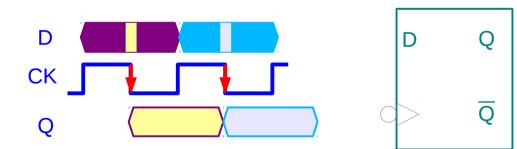

# Master-Slave D FlipFlop – Falling Edge

# Master-Slave D FlipFlop – Rising Edge

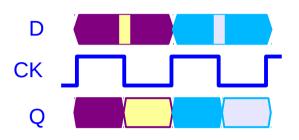

# D Latch & D FlipFlop

Level Sensitive D Latch

CK=1 transparent CK=0 opaque

Edge Sensitive D FlipFlop

$CK=1 \rightarrow 0$  transparent opaque

#### Advantages of Latches over FFs

#### Flipflop designs are very easy to verify timing

- Each path between flip-flops must be less than the clock period

- Tools check for skew, setup, and hold time violations

- Short paths are padded (buffers are added to slow down the signals)

- Skew in flip-flop based systems affects the critical path

Most designs in industry are based on flip-flops

Latch designs are more flexible than a flip-flop design

- Need to CAD tools to make sure it works

- Can borrow time to allow a path to be longer than clock period

- Can tolerate clock skew

- -- skew does not directly add to cycle time

- Less silicon area

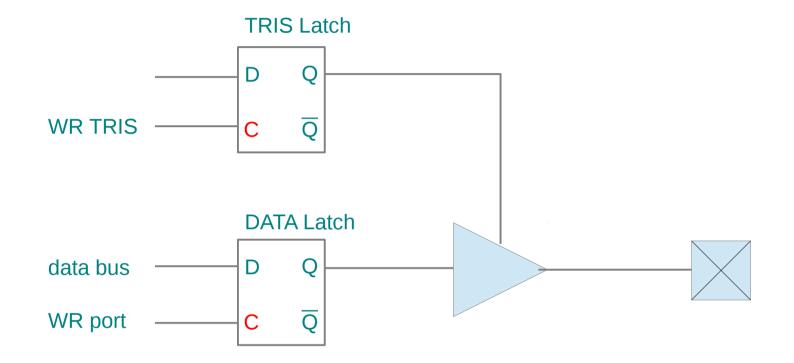

#### Latches at the output ports

#### References

- [1] http://en.wikipedia.org/

- [2] M. M. Mano, C. R. Kime, "Logic and Computer Design Fundamentals", 4<sup>th</sup> ed.

- [3] D.M. Harris, S. L. Harris, "Digital Design and Computer Architecture"

- [4] http://www.ee.ic.ac.uk/pcheung lecture note "Topic 7 clocking strategies"